HAL Id: tel-01297688

https://tel.archives-ouvertes.fr/tel-01297688

Submitted on 4 Apr 2016HAL is a multi-disciplinary open access archive for the deposit and dissemination of sci-entific research documents, whether they are pub-lished or not. The documents may come from teaching and research institutions in France or

L’archive ouverte pluridisciplinaire HAL, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d’enseignement et de recherche français ou étrangers, des laboratoires

de circuits intégrés

Ingrid Exurville

To cite this version:

Ingrid Exurville. Détection non destructive de modification malveillante de circuits intégrés. Autre. Ecole Nationale Supérieure des Mines de Saint-Etienne, 2015. Français. �NNT : 2015EMSE0800�. �tel-01297688�

NNT : 2015 EMSE 0800

THÈSE

présentée par

Ingrid EXURVILLE

pour obtenir le grade de

Docteur de l’École Nationale Supérieure des Mines de Saint-Étienne

Spécialité : MICROÉLECTRONIQUE

DÉTECTION NON DESTRUCTIVE

DE MODIFICATIONS MALVEILLANTES

SUR CIRCUITS INTÉGRÉS

soutenue à Gardanne, le 30/10/2015

Membres du jury

Président :

Michel AUGUIN

Professeur, Université de Nice, Nice

Rapporteurs :

Jean-Luc DANGER

Bruno ROUZEYRE

Professeur, Telecom ParisTech, Paris

Professeur, Université de Montpellier 2, Montpellier

Examinateurs :

Jean-Luc AUTRAN

Viktor FISCHER

Julien FRANCQ

Professeur, Université Aix Marseille, Marseille

Professeur, Laboratoire Hubert Curien, S

tÉtienne

Docteur, Airbus - CyberSecurity, Paris

ABSI Nabil CR Génie industriel CMP

AVRIL Stéphane PR2 Mécanique et ingénierie CIS

BALBO Flavien PR2 Informatique FAYOL

BASSEREAU Jean-François PR Sciences et génie des matériaux SMS

BATTON-HUBERT Mireille PR2 Sciences et génie de l'environnement FAYOL

BERGER DOUCE Sandrine PR2 Sciences de gestion FAYOL

BERNACHE-ASSOLLANT Didier PR0 Génie des Procédés CIS

BIGOT Jean Pierre MR(DR2) Génie des Procédés SPIN

BILAL Essaid DR Sciences de la Terre SPIN

BLAYAC Sylvain MA(MDC) Microélectronique CMP

BOISSIER Olivier PR1 Informatique FAYOL

BORBELY Andras MR(DR2) Sciences et génie des matériaux SMS

BOUCHER Xavier PR2 Génie Industriel FAYOL

BRODHAG Christian DR Sciences et génie de l'environnement FAYOL

BRUCHON Julien MA(MDC) Mécanique et ingénierie SMS

BURLAT Patrick PR1 Génie Industriel FAYOL

COURNIL Michel PR0 Génie des Procédés DIR

DARRIEULAT Michel IGM Sciences et génie des matériaux SMS

DAUZERE-PERES Stéphane PR1 Génie Industriel CMP

DEBAYLE Johan CR Image Vision Signal CIS

DELAFOSSE David PR0 Sciences et génie des matériaux SMS

DESRAYAUD Christophe PR1 Mécanique et ingénierie SMS

DOLGUI Alexandre PR0 Génie Industriel FAYOL

DRAPIER Sylvain PR1 Mécanique et ingénierie SMS

FEILLET Dominique PR1 Génie Industriel CMP

FEVOTTE Gilles PR1 Génie des Procédés SPIN

FRACZKIEWICZ Anna DR Sciences et génie des matériaux SMS

GARCIA Daniel MR(DR2) Génie des Procédés SPIN

GERINGER Jean MA(MDC) Sciences et génie des matériaux CIS

GOEURIOT Dominique DR Sciences et génie des matériaux SMS

GRAILLOT Didier DR Sciences et génie de l'environnement SPIN

GROSSEAU Philippe DR Génie des Procédés SPIN

GRUY Frédéric PR1 Génie des Procédés SPIN

GUY Bernard DR Sciences de la Terre SPIN

HAN Woo-Suck MR Mécanique et ingénierie SMS

HERRI Jean Michel PR1 Génie des Procédés SPIN

KERMOUCHE Guillaume PR2 Mécanique et Ingénierie SMS

KLOCKER Helmut DR Sciences et génie des matériaux SMS

LAFOREST Valérie MR(DR2) Sciences et génie de l'environnement FAYOL

LERICHE Rodolphe CR Mécanique et ingénierie FAYOL

LI Jean-Michel Microélectronique CMP

MALLIARAS Georges PR1 Microélectronique CMP

MAURINE Philippe CMP

MOLIMARD Jérôme PR2 Mécanique et ingénierie CIS

MONTHEILLET Frank DR Sciences et génie des matériaux SMS

MOUTTE Jacques CR Génie des Procédés SPIN

NEUBERT Gilles FAYOL

NIKOLOVSKI Jean-Pierre Ingénieur de recherche CMP

NORTIER Patrice PR1 SPIN

PIJOLAT Christophe PR0 Génie des Procédés SPIN

PIJOLAT Michèle PR1 Génie des Procédés SPIN

PINOLI Jean Charles PR0 Image Vision Signal CIS

POURCHEZ Jérémy MR Génie des Procédés CIS

ROBISSON Bruno Ingénieur de recherche CMP

ROUSSY Agnès MA(MDC) Génie industriel CMP

ROUSTANT Olivier MA(MDC) Mathématiques appliquées FAYOL

ROUX Christian PR Image Vision Signal CIS

STOLARZ Jacques CR Sciences et génie des matériaux SMS

TRIA Assia Ingénieur de recherche Microélectronique CMP

VALDIVIESO François PR2 Sciences et génie des matériaux SMS

VIRICELLE Jean Paul DR Génie des Procédés SPIN

WOLSKI Krzystof DR Sciences et génie des matériaux SMS

XIE Xiaolan PR1 Génie industriel CIS

YUGMA Gallian CR Génie industriel CMP

BERGHEAU Jean-Michel PU Mécanique et Ingénierie ENISE

BERTRAND Philippe MCF Génie des procédés ENISE

DUBUJET Philippe PU Mécanique et Ingénierie ENISE

FEULVARCH Eric MCF Mécanique et Ingénierie ENISE

FORTUNIER Roland PR Sciences et Génie des matériaux ENISE

GUSSAROV Andrey Enseignant contractuel Génie des procédés ENISE

HAMDI Hédi MCF Mécanique et Ingénierie ENISE

LYONNET Patrick PU Mécanique et Ingénierie ENISE

RECH Joël PU Mécanique et Ingénierie ENISE

SMUROV Igor PU Mécanique et Ingénierie ENISE

EMSE : Enseignants-chercheurs et chercheurs autorisés à diriger des thèses de doctorat (titulaires d’un doctorat d’État ou d’une HDR)

ENISE : Enseignants-chercheurs et chercheurs autorisés à diriger des thèses de doctorat (titulaires d’un doctorat d’État ou d’une HDR) Spécialités doctorales Responsables :

SCIENCES ET GENIE DES MATERIAUX K. Wolski Directeur de recherche MECANIQUE ET INGENIERIE S. Drapier, professeur GENIE DES PROCEDES F. Gruy, Maître de recherche SCIENCES DE LA TERRE B. Guy, Directeur de recherche SCIENCES ET GENIE DE L’ENVIRONNEMENT D. Graillot, Directeur de recherche

Spécialités doctorales Responsables

MATHEMATIQUES APPLIQUEES O. Roustant, Maître-assistant INFORMATIQUE O. Boissier, Professeur IMAGE, VISION, SIGNAL JC. Pinoli, Professeur GENIE INDUSTRIEL A. Dolgui, Professeur MICROELECTRONIQUE S. Dauzere Peres, Professeur

ise à jo ur : 28/10/ 2014

Remerciements

Je tiens `a adresser mes remerciements aux personnes qui m’ont guid´ee, qui ont cru en moi et qui m’ont soutenue au cours de ces trois ann´ees de travail.

Tout d’abord, je commencerai par remercier les membres de mon jury pour leurs re-marques constructives sur mon manuscrit ainsi que leurs implications au cours de la sou-tenance : merci au pr´esident du jury de th`ese monsieur Michel Auguin, `a mes rapporteurs messieurs Jean-Luc Danger et Bruno Rouzeyre, `a mes examinateurs messieurs Jean-Luc Autran, Viktor Fischer et Julien Francq, `a mon directeur de th`ese monsieur Bruno Robis-son, `a mon encadrant monsieur Jean-Baptiste Rigaud ainsi qu’`a ma correspondante DGA madame Rose-Marie Sauvage.

J’adresse ´egalement mes remerciements `a toutes les personnes formidables que j’ai rencontr´e au Centre de Micro´electronique de Provence (CMP), ´etablissement dans lequel j’ai pass´e trois ann´ees en tant qu’´el`eve-ing´enieure, puis trois ann´ees comme th´esarde. Je remercie particuli`erement mes coll`egues du laboratoire Syst`emes et Architectures S´ ecuri-s´es. J’ai une pens´ee particuli`ere pour Jacques Fournier qui m’a pr´esent´ee le monde de la recherche au cours d’un stage ing´enieur : cette exp´erience enrichissante m’a encourag´ee `a faire une th`ese. Je remercie du fond du cœur tous les doctorants, les post-doctorants et les ing´enieurs de recherche qui ont rendu ces trois ann´ees vraiment plus agr´eables en tout point de vue. J’adresse sp´ecialement un merci `a Thomas Sarno, qui a r´ealis´e sa th`ese en mˆeme temps que moi, avec qui j’ai pass´e de longues heures `a parler de nos ch`eres vies de th´esards et `a tenter de refaire le monde. Merci aussi `a Lo¨ıc Zussa, Nicolas Moro et Marc Lacruche pour ces moments riches en joie et en d´ecouvertes en tout genre.

Je tiens `a exprimer toute ma gratitude ´egalement `a Assia Tria, V´eronique Villar´eal et Pierre Joubert qui m’ont aid´e `a soutenir dans les temps, `a rendre un manuscrit de bonne qualit´e, et surtout, qui m’ont permit d’appr´ehender cette fin de th`ese avec plus de s´er´enit´e. Je tiens ´egalement `a t´emoigner de mes remerciements les plus sinc`eres et mon amour `

a mes parents, et plus largement `a ma famille, qui ont toujours cru en moi et qui m’ont ´epaul´ee dans les moments heureux et difficiles que l’on rencontre au cours d’une vie, et ce, malgr´e la distance. Enfin, je remercie Lo¨ıc Zussa pour avoir ´et´e `a mes cˆot´es sur tous les aspects aussi bien sur les points techniques de relecture et correction de mes travaux de recherche que sur les points humains.

”Sachez que le travail, l’amour et l’amiti´e doivent reposer sur des liens construits sur la confiance et l’honnˆetet´e. Sans cette base, nous allons au devant de nombreux probl`emes.”

Sommaire

Remerciements v

Sommaire xii

Glossaire / Index 1

Introduction 3

1 Fabrication et menaces envers les circuits int´egr´es 5

1.1 Pr´esentation des circuits int´egr´es . . . 6

1.1.1 Contexte g´en´eral . . . 6

1.1.2 Circuits de s´ecurit´e et menaces associ´ees . . . 7

1.2 Cas r´ef´erenc´es de Chevaux de Troie Mat´eriels (CTM). . . 9

1.3 Pourquoi parle-t-on de CTM ?. . . 9 1.4 Taxonomie . . . 10 1.5 Phase d’insertion . . . 11 1.5.1 Acteurs . . . 11 1.5.2 Sp´ecifications . . . 12 1.5.3 Conception . . . 12

1.5.3.1 Logiciels de Conception Assist´ee par Ordinateur (CAO) . . 13

1.5.3.2 Biblioth`eque de cellules . . . 13

1.5.4 Fabrication . . . 13

1.5.4.1 Production de wafer . . . 14

1.5.4.2 Photolithographie . . . 16

1.5.4.3 Gravure et dopage . . . 17

1.5.4.4 V´erification des wafers . . . 17

1.5.5 Encapsulation et assemblage . . . 18

1.5.6 Tests. . . 18

1.6 Caract´eristiques physiques . . . 18

1.7 Effets . . . 19

1.11 Conclusion . . . 21

2 M´ethodes de protection contre les CTM 23 2.1 Protection des circuits int´egr´es . . . 24

2.2 D´efinition de la strat´egie d’approche pour la protection de circuits int´egr´es contre les CTM . . . 25

2.3 Mesures pr´eventives . . . 26

2.3.1 ”Built-In Self-Test ”, BIST . . . 26

2.3.2 Obfuscation . . . 26

2.3.3 Congestion des circuits. . . 27

2.3.4 Technique de chiffrement de logique mat´erielle . . . 27

2.3.5 Encodage des ´etats logiques . . . 27

2.4 Proc´ed´es de d´etection de CTM . . . 28

2.4.1 M´ethodes destructives . . . 29

2.4.2 M´ethodes non destructives . . . 31

2.4.2.1 Analyses par canaux auxiliaires et par injection de fautes . 31 2.4.2.2 Tests logiques . . . 34

2.5 Difficult´es techniques li´ees `a la d´etection de CTM . . . 35

2.5.1 Variabilit´e des proc´ed´es de fabrication . . . 36

2.5.2 Le vieillissement du circuit . . . 36

2.6 Positionnement de la th`ese par rapport `a l’´etat de l’art . . . 38

2.7 Conclusion . . . 39

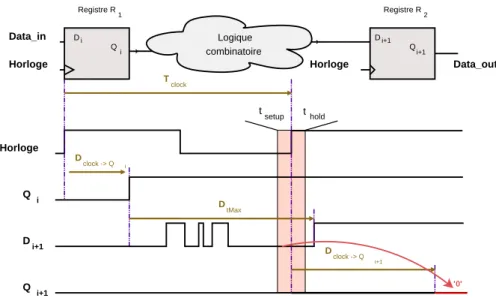

3 Description des outils et des bancs de mesures utilis´es 41 3.1 Les contraintes temporelles . . . 42

3.1.1 Fonctionnement d’un circuit synchrone. . . 42

3.1.2 Violations des contraintes temporelles . . . 44

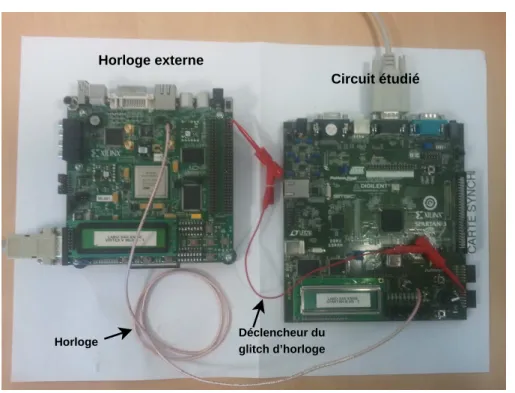

3.2 Injection de fautes par modification transitoire de la fr´equence d’horloge . . 46

3.2.1 Description du banc de glitchs d’horloge . . . 46

3.2.2 Approche de d´etection . . . 49

3.2.3 Protocole exp´erimental. . . 50

3.3 FPGA . . . 51

3.4 Cibles ´etudi´ees . . . 52

3.4.1 Circuit XOR . . . 52

3.4.2 Circuit AES. . . 53

3.4.2.2 SubBytes . . . 55

3.4.2.3 ShiftRows. . . 56

3.4.2.4 MixColumns . . . 57

3.4.3 Implantation . . . 58

3.5 Logiciels utilis´es. . . 59

3.5.1 Insertion d’un CTM au niveau RTL . . . 60

3.5.2 Insertion d’un CTM apr`es Placement et Routage . . . 60

3.6 Conclusion . . . 61

4 Utilisation des temps de calcul pour la d´etection de CTM 63 4.1 Validation de l’outil de glitch d’horloge pour la mesure des temps de calcul sur le circuit XOR . . . 64

4.1.1 Montage XOR compos´e d’un suiveur par chemin . . . 64

4.1.2 Montage XOR compos´e de cinq suiveurs par chemin . . . 65

4.1.3 Montage XOR compos´e d’un nombre diff´erent de suiveurs par chemin 66 4.2 Relation entre des blocs d´ependants logiquement . . . 67

4.3 Relation entre des blocs ind´ependants logiquement . . . 70

4.3.1 Principe de la contre-mesure ´etudi´ee . . . 70

4.3.2 Mise en ´evidence et exploitation des liens ´electriques entre des blocs logiquement ind´ependants . . . 72

4.4 Mod`ele de d´elai existant . . . 74

4.5 D´efinition d’un nouveau mod`ele de d´elai . . . 75

4.6 Conclusion . . . 76

5 D´etection de CTM ins´er´es au niveau du code VHDL et apr`es l’´etape de Placement et Routage sur circuit AES 77 5.1 Validation exp´erimentale du mod`ele de temps de calcul . . . 78

5.1.1 Les donn´ees en entr´ee . . . 78

5.1.2 Les conditions exp´erimentales . . . 79

5.1.3 Les variations de proc´ed´es . . . 81

5.2 Ajout de CTM niveau RTL . . . 83

5.3 D´etection de CTM ins´er´e au niveau RTL. . . 84

5.3.1 Observation de l’effet de l’ajout d’un CTM sur une carte . . . 84

5.3.2 D´etection d’un CTM avec prise en compte des variations de proc´ed´es 86 5.4 Ajout de CTM apr`es l’´etape de Placement & Routage . . . 89

5.4.1 Sc´enario d’insertion . . . 89

5.4.2 Description des CTM . . . 90

5.5.1 Observation de l’effet de l’ajout d’un CTM sur une carte . . . 91

5.5.2 Observation de l’impact des variations de proc´ed´es sur les temps de calcul internes . . . 93

5.6 Quantification de l’impact des variations de proc´ed´es par rapport `a la pr´ e-sence des CTM sur les temps de calcul internes . . . 94

5.7 Conclusion . . . 96

6 D´etection de CTM par l’att´enuation de l’impact des variations de pro-c´ed´es sur les d´elais mesur´es 99 6.1 Technique d’att´enuation des variations de proc´ed´es . . . 100

6.2 Construction du mod`ele de r´ef´erence . . . 103

6.3 M´ethode de d´etection des CTM . . . 104

6.4 D´etection exp´erimentale des CTM avec prise en compte des variations de proc´ed´es . . . 105

6.4.1 Construction du GM . . . 105

6.4.2 Application de la m´ethode de d´etection . . . 105

6.5 Axes d’am´elioration de la m´ethode de d´etection de CTM. . . 110

6.5.1 Nombre de stimuli . . . 110

6.5.2 Nombre de Stress. . . 111

6.6 Conclusion . . . 112

Conclusion et perspectives 113

Listes des figures 119

Listes des tableaux 121

Publications personnelles 123

Glossaire / Index

AES : Advanced Encryption Standard

ASIC : Application-Specific Integrated Circuit ATPG : Automatic Test Pattern Generation BIST : Built-In Self-Test

CE : Chip Enable

CLB : Configurable Logic Blocks

CMOS : Complementary Metal Oxide Semi-conductor CPA : Correlation Power Analysis

CTM : Cheval de Troie Mat´eriel DFA : Differential Fault Analysis DLL : Delay Locked Loop

EM : ´ElectroMagn´etique

FPGA : Field-Programmable Gate Array FSA : Fault Sensitivity Analysis

GDSII : Graphical Datatbase System GM : Golden Model

MEB : Microscope ´Electronique `a Balayage LUT : LookUp table

RTL : Register Transfer Level

VHDL : VHSIC Hardware Description Language VHSIC : Very High Speed Integrated Circuit

Introduction

Le secteur de l’´electronique s’est d´evelopp´e de fa¸con exponentielle au cours de ces derni`eres d´ecennies. Pr´esent notamment dans les domaines des transports, du militaire, de la d´efense, des communications et des finances, le monde qui nous entoure s’articule, en partie, autour de ces nouvelles technologies mat´erielles. Cette demande massive de circuits int´egr´es a favoris´e la croissance de nombreuses entreprises. Ce ph´enom`ene s’accompagne ´egalement d’une hausse constante du coˆut ´economique des usines ainsi qu’une ´economie tendant vers une certaine mutualisation de ces usines on´ereuses. Afin de limiter les frais de production, des industries de fabrication des semi-conducteurs sont d´elocalis´ees.

Les circuits int´egr´es peuvent induire des failles de s´ecurit´e. Il est donc important de s’assurer de leur int´egrit´e. La d´elocalisation des usines de production entraine une perte du contrˆole du flot de conception. Des fonctionnalit´es malicieuses peuvent ˆetre ins´er´ees avant qu’une puce soit mise sur le march´e. On parle de Chevaux de Troie Mat´eriels (CTM, Har-ware Trojans en anglais). Leur principe est similaire `a celui des virus ou logiciels espions, sauf qu’ils proviennent de modifications mat´erielles et non logicielles. Les r´epercussions envisageables sont nombreuses : des informations confidentielles peuvent ˆetre extraites `a l’insu de l’utilisateur, voire des d´enis de service provoqu´es.

Face `a la complexit´e technologique d’un circuit int´egr´e, la d´etection de modifications malicieuses potentielles est une menace de plus en plus `a consid´erer. Elle est devenue depuis peu le fruit de multiples recherches visant `a s´ecuriser un circuit et/ou d´etecter un CTM. Aujourd’hui, il s’agit d’une pr´eoccupation mondiale. Ce d´efi est rendu difficile par le comportement de certaines entreprises victimes, qui refusent de mettre `a disposition leurs circuits infect´es afin de pr´eserver leur propri´et´e intellectuelle et ´eviter de compromettre leur r´eputation.

Il existe deux approches pour prot´eger les circuits int´egr´es des CTM : la d´etection et la pr´evention. L’objectif de cette th`ese est d’´etudier et de d´evelopper une technique de d´etection de CTM non destructrice, avant l’activation de ce dernier.

Le travail de ce manuscrit s’oriente vers une m´ethode d’identification de circuits fiables. Le principe g´en´eral est de mesurer les temps de calcul internes d’un syst`eme et ne pas li-miter l’´etude uniquement `a ses chemins critiques. Ces mesures serviront d’empreintes pour authentifier un circuit. En comparant les empreintes de cartes de r´ef´erence `a d’autres

pro-venant de cartes dont l’int´egrit´e est `a v´erifier, on tentera de d´etecter la pr´esence de CTM. Un outil permettant de diminuer une p´eriode d’horloge localement est utilis´e pour r´ealiser les mesures de temps de calcul internes. Son principe repose sur les violations de contraintes temporelles. De plus, cette ´etude se concentre particuli`erement sur la caract´erisation des variations comportementales li´ees aux proc´ed´es de fabrication des circuits int´egr´es ainsi qu’aux conditions exp´erimentales. Ces param`etres ajoutent un caract`ere impr´evisible aux mesures, rendant la d´etection de CTM plus complexe.

Le premier chapitre introduit le contexte g´en´eral des circuits int´egr´es et la menace repr´esent´ee par les CTM. Les possibilit´es d’insertion de modifications malveillantes sont ´

enum´er´ees pour chaque ´etape de fabrication. Finalement, les ´el´ements permettant de d´ e-crire un CTM sont propos´es.

Le second chapitre d´ecrit l’´etat de l’art des m´ethodes de protection contre les CTM. Il d´etaille les approches de d´etection et de pr´evention ainsi que les difficult´es techniques relatives `a leurs mises en place.

Une description des outils et des bancs de mesures utilis´es est faite dans le troisi`eme chapitre. On rappelle les contraintes temporelles auxquelles est soumis un circuit syn-chrone. Par la suite, les circuits cibles utilis´es pour les mesures, les logiciels ainsi que les supports mat´eriels sont pr´esent´es.

Le chapitre 4 insiste sur l’usage des temps de calcul internes comme canal prometteur pour la d´etection de CTM. On v´erifie que les violations de contraintes temporelles im-pactent la logique combinatoire des circuits cibles. Ensuite, les relations ´electriques entre blocs logiques (d´ependants ou non) sont d´ecrites. Pour finir, un nouveau mod`ele de temps de calcul qui servira de support aux ´etudes sera propos´e.

Le travail de recherche du chapitre 5 valide le mod`ele qui prend en compte les variations de proc´ed´es, l’influence ´electrique des composants les uns sur les autres et les conditions exp´erimentales. La premi`ere d´emarche consiste `a valider la mesure de temps de calcul comme canal permettant de rep´erer la pr´esence d’un CTM. Un CTM combinatoire est ajout´e au niveau de la description VHDL d’un AES-128 bits implant´e sur 4 cartes FPGA de mˆeme mod`ele. La seconde d´emarche consiste `a ins´erer deux CTM s´epar´ement apr`es l’´etape de Placement & Routage.

Le chapitre 6 propose une nouvelle technique de traitement des donn´ees. Cette m´ethode repose sur la diminution de l’impact des variations de proc´ed´es sur les mesures effectu´ees. Au cours des diff´erentes ´etudes, les pistes de recherches et d’am´eliorations sont ´egalement pr´esent´ees.

Chapitre

1

Fabrication et menaces envers les circuits

int´egr´es

Sommaire

1.1 Pr´esentation des circuits int´egr´es . . . 6

1.1.1 Contexte g´en´eral . . . 6

1.1.2 Circuits de s´ecurit´e et menaces associ´ees . . . 7

1.2 Cas r´ef´erenc´es de Chevaux de Troie Mat´eriels (CTM) . . . 9

1.3 Pourquoi parle-t-on de CTM ?. . . 9 1.4 Taxonomie. . . 10 1.5 Phase d’insertion. . . 11 1.5.1 Acteurs . . . 11 1.5.2 Sp´ecifications . . . 12 1.5.3 Conception . . . 12 1.5.4 Fabrication . . . 13 1.5.5 Encapsulation et assemblage . . . 18 1.5.6 Tests. . . 18

1.6 Caract´eristiques physiques . . . 18

1.7 Effets . . . 19

1.8 M´ecanisme d’activation . . . 19

1.9 Niveau d’abstraction . . . 20

1.10 Emplacement . . . 20

Apr`es une br`eve introduction des menaces concernant les circuits int´egr´es, ce chapitre d´ecrit le fonctionnement g´en´eral d’un cheval de Troie Mat´eriel.

Ensuite, les risques de modifications malveillantes existants lors des diff´erentes ´etapes de production d’un circuit int´egr´e seront abord´es. Dans cette pr´esentation d´etaill´ee du flot de conception, les phases les plus sensibles seront identifi´ees.

Pour finir, les m´ethodes d’ajout de Chevaux de Troie Mat´eriels seront d´ecrites.

1.1 Pr´

esentation des circuits int´

egr´

es

1.1.1 Contexte g´en´eral

De nos jours, les circuits int´egr´es (on parle ´egalement de puces ´electroniques) sont pr´esents dans de multiples secteurs tels que la communication, les transports, la sant´e et la finance. Leurs composants ´el´ementaires (m´emoires, capteurs, logique, microprocesseurs, etc.) doivent r´epondre `a des contraintes de fiabilit´e, de s´ecurit´e et de dimensionnement.

-1% 1% 3% 5% 7% 9% 11% 13% 15% 17% 19% 21% 23% 0% 5% 10% 15% 20% 25% 30% PC standards 59.1$ Téléphones portables 70.7$ Serveurs 14$ Décodeurs 5.5$ TV numériques 14.1$ Automobiles 21.7$ Consoles de jeu 4.5$ Médical 4.5$ Tablettes

17.6$ Réseaux sans fil 9.4$

Fournitures connexion Internet

3.3$ 25%

Marché de l’utilisation finale des circuits intégrés (en Milliard de $) et leur taux de croissance

Taux de croissance annuel

Figure 1.1 – March´e des circuits int´egr´es

La figure 1.1repr´esente le march´e de l’utilisation finale des circuits int´egr´es ainsi que l’estimation de leur croissance pour 11 principaux domaines d’application. Cette ´etude, r´ealis´ee en 2013, est bas´ee sur des pr´evisions `a 5 ans de ces march´es [57]. Le chiffre d’affaires g´en´er´e pour ces 11 grands secteurs d’activit´e repr´esente 76 % du march´e total des puces

1.1. Pr´esentation des circuits int´egr´es

´electroniques dans le monde en 2014. Les analystes pr´evoient une croissance de 85 % `a horizon 2018.

1.1.2 Circuits de s´ecurit´e et menaces associ´ees

Les premiers circuits int´egr´es d´edi´es aux applications s´ecuritaires ont ´et´e introduits dans les ann´ees 90 par le biais des cartes `a puces. Leur rˆole premier est d’assurer des fonctions d’identification comme notamment les cartes SIM et les cartes VITALE. En 1998, des chercheurs de l’universit´e de Cambridge ont mis en avant la possibilit´e de r´ealiser des attaques plus ou moins complexes dans le but d’extraire des donn´ees confidentielles ou sensibles. Cette mise `a mal `a imposer `a l’industrie de la carte `a puce de mettre des moyens cons´equents pour prot´eger les circuits contre diff´erents types d’attaques. En effet, il existe par exemple un ensemble d’attaques dites ¨attaques en fautes” qualifi´ees d’actives (cf [50]). D’autres types d’approches ont ´et´e ´egalement mises au point telles que les attaques par sondage ou par canaux auxiliaires qui sont dites passives (cf section 2.4).

Par ailleurs, compte tenu des besoins croissants en terme de composants ´electroniques (cf figure1.1), il est n´ecessaire de disposer des ressources industrielles ad´equates pour r´ e-pondre `a ce march´e. Seuls de grands groupes disposant d’unit´es de production ´evolu´ees sont capables d’assurer cette fourniture en composants. L’industrie des semi-conducteurs est un secteur de l’´economie o`u les coˆuts sont les plus importants au regard de l’´evolution technologique. En effet, un changement de technologie engendre 30 % de coˆuts suppl´ emen-taires. Les principales unit´es de fabrication en Europe ne permettent plus d’assurer des volumes suffisants. Ceci impose donc de faire appel `a des usines hors de ses fronti`eres. Le tableau1.1r´ecapitule le classement des plus gros fondeurs dans le monde [101]. Une grande majorit´e de ces entreprises sont regroup´ees dans certaines r´egions du globe en raison d’une main d’œuvre bon march´e et d’aides financi`eres gouvernementales [26]. Ce regroupement soul`eve des questionnements d’ordre g´eopolitique quant `a l’int´egrit´e des circuits d´elivr´es. Cette ouverture `a l’´etranger pose de s´erieux probl`emes de confiance de deux types :

– la contrefa¸con : selon le site de l’INPI [56] ¨la contrefa¸con se d´efinit comme la repro-duction, l’imitation ou l’utilisation totale ou partielle d’un droit de propri´et´e intel-lectuelle sans l’autorisation de son propri´etaire”. Au niveau mondial, la contrefa¸con des circuits int´egr´es repr´esente 7 % de part de march´e d’apr`es [81], ce qui induit une perte de plus de 10 milliards de dollars par an. Outre les pertes financi`eres, l’utilisa-tion des composants contrefaits repr´esente un danger vis-`a-vis de la s´ecurit´e et de la fiabilit´e. L’ERAI (Electronic Resellers Association International) est une association priv´ee qui travaille pour des entreprises afin de traquer les composants ´electroniques contrefaits. En 2011, elle a recens´e plus de 1 300 cas de falsifications partout dans le monde [51]. C’est plus du double des cas report´es en 2010, et du quadruple de ceux

rapport´es en 2009. Les auteurs de [93] pr´esentent des r`egles `a suivre pour tenter de limiter le risque de contrefa¸cons. Ils illustrent leurs propos avec quelques exemples de compagnies victimes de ces attaques. On distingue notamment le cas de l’entreprise NEC, g´eant japonais dans le secteur de l’´electronique, qui a d´ecouvert un r´eseau de contrefa¸cons allant de la fabrication `a la distribution de ces produits. Face `a cet inci-dent, l’entreprise a d´evelopp´e durant 3 ans une protection bas´ee sur des empreintes digitales d’objets via des motifs 3D. Cette technique est disponible depuis juin 2015 [75]. Elle pourrait ˆetre applicable `a d’autres domaines d’activit´e.

– les Chevaux de Troie Mat´eriels : d’apr`es [94], on appelle Cheval de Troie Mat´eriel (CTM) toute modification malicieuse de circuits ¨l´egitimes” faite au cours des ´etapes de production d’une puce. Il existe des fabricants traditionnels de circuits int´egr´es (appel´es IDM pour Integrated Device Manufacturers) qui r´ealisent eux-mˆemes la pro-duction et la vente de leurs circuits int´egr´es. On distingue notamment les am´ericains Intel, Texas Instruments, les europ´eens STMicroelectronics ou Infineon et le japonais Renesas. N´eanmoins, les IDM sont peu nombreux car la mise en place du proc´ed´e de fabrication requiert des ´equipements coˆuteux, de l’ordre du milliard d’euros, pour lesquels peu d’entreprises peuvent se permettre d’investir. On dit alors qu’une soci´et´e est fabless lorsqu’elle ne s’est sp´ecialis´ee que dans la conception et la vente de puces ´

electroniques. La fabrication de ces circuits est sous-trait´ee `a des soci´et´es sp´ecialis´ees externes appel´ees fonderies. Cependant, l’externalisation du processus de fabrication des composants ´electroniques qui induit la d´el´egation `a une tierce partie, lui donne ainsi la possibilit´e d’implanter des fonctionnalit´es non d´esir´ees au sein du syst`eme, voire d’ajouter du mat´eriel malveillant au circuit original. On parle d’insertion de CTM.

Le travail pr´esent´e dans ce manuscrit s’inscrit dans le contexte des circuits d´edi´es `a des applications de s´ecurit´e qui sont produits dans des environnements o`u la confiance ne peut ˆetre garantie. Il se focalise particuli`erement sur la d´etection des CTM. Cette th`ese est cofinanc´ee par le Commissariat aux ´Energies Atomiques (CEA) et par la Direction G´en´erale de l’Armement (DGA). Elle a ´et´e r´ealis´ee dans le laboratoire Syst`emes et Archi-tectures S´ecuris´ees (SAS). Ce laboratoire travaille notamment sur le th`eme de la protection des circuits int´egr´es contre les CTM dans le cadre de deux projets de recherche d´emarr´es en 2012 : un projet europ´een appel´e HINT [1] et un projet ANR (Agence Nationale de la Recherche) nomm´e HOMERE+ [2]. Ils ont pour but d’une part de rechercher et de d´evelopper des m´ethodes de d´etection de CTM, et d’autre part de trouver des solutions permettant d’empˆecher leur insertion.

1.2. Cas r´ef´erenc´es de Chevaux de Troie Mat´eriels (CTM)

Classement Compagnie Emplacement Chiffre d’affaire (Millions de $)

1 TSMC Ta¨ıwan 19 850

2 GlobalFoundries Etats-Unis´ 4 261

3 UMC Ta¨ıwan 3 959

4 Samsung Cor´ee du Sud 3 950

5 SMIC China 1 973

6 Powerchip Ta¨ıwan 1 175

7 Vanguard Ta¨ıwan 713

8 Huahong Grace Chine 710

9 Dongbu Cor´ee du Sud 570

10 TowerJazz Isra¨el 509

11 IBM Etats-Unis´ 485

12 MagnaChip Cor´ee du Sud 411

Table 1.1 – Classement des fonderies pour l’ann´ee 2014

1.2 Cas r´

ef´

erenc´

es de Chevaux de Troie Mat´

eriels (CTM)

Les premiers exemples de CTM ont ´et´e signal´es `a la fin des ann´ees 2000. Les entreprises dont les circuits ont ´et´e infect´es par des CTM pr´ef`erent garder sous silence ces incidents afin de ne pas entacher leur r´eputation et ainsi r´eduire leur part de march´e. C’est pour cela que peu de cas sont r´ef´erenc´es dans la litt´erature. Cependant, les risques sont bel et bien pr´esents. Du d´eni de service `a la fuite d’informations confidentielles, toutes les cons´equences peuvent ˆetre ´economiquement graves ou dangereuses pour la s´ecurit´e des utilisateurs.

En 2007 par exemple, un radar syrien n’a pas pr´evenu l’arriv´ee d’une attaque a´erienne [7]. `A cause de ce dysfonctionnement, on soup¸conne que ce dernier ´etait pourvu d’un CTM. Les incidents de ce type tendent `a croˆıtre de plus en plus. Bien qu’il n’y ait pas de valeurs chiffr´ees pr´ecises, beaucoup de rapports soul`event cette question des CTM, et notamment la mani`ere dont ils ont pu ˆetre introduits soulevant un fort soup¸con du processus de fabrication.

1.3 Pourquoi parle-t-on de CTM ?

Dans la mythologie grecque antique, selon l’Iliade [28], la guerre de Troie entre les grecs et les troyens est class´ee comme un ´ev`enement l´egendaire qui d´ebute par l’enl`evement d’H´el`ene, l’´epouse du roi grec de Sparte. Hom`ere raconte par la suite dans l’Odyss´ee [53] qu’apr`es plusieurs confrontations, Ulysse fait construire un cheval en bois en guise d’offrande aux troyens pour reconnaitre leur sup´eriorit´e face aux grecs. Pour fˆeter leur

victoire, les troyens font ensuite rentrer le cheval pi´eg´e dans leurs murs. Durant la nuit, alors que tous fˆetent leur succ`es, les guerriers grecs enferm´es dans le cheval sortent de leur cachette, ouvrent les portes de la cit´e `a l’arm´ee grecque qui attendait dehors et assi`egent la ville de Troie. H´el`ene fut ramen´ee `a Sparte 20 ans apr`es son enl`evement. Ce cadeau a ainsi constitu´e une bonne supercherie pour duper les Troyens.

Le terme de cheval de Troie fait ainsi r´ef´erence `a cette intrusion malveillante qui a un effet n´efaste `a l’insu du propri´etaire ou de l’utilisateur. Il s’est g´en´eralis´e dans le domaine de l’informatique et de l’´electronique particuli`erement.

1.4 Taxonomie

Plusieurs descriptions de CTM ont ´et´e propos´ees afin de mieux les r´epertorier. Il existe une taxonomie r´epandue et utilis´ee est pr´esent´ee dans [97] et dans [94]. Elle permet de r´eduire la description d’un CTM en trois principales cat´egories (les trois premi`eres ´ecrites et encadr´ees en bordeaux sur la figure1.2). Cependant, une taxonomie d´etaill´ee fait office de r´ef´erence `a ce jour (pr´esent´ee par la figure1.2). Elle est disponible sur le site Trust-HUB [54].

Chevaux de Troie Matériels

Phase d’insertion Niveau d’abstraction Mécanisme d’activation Effets Emplacement Caractéristiques physiques Spécification Conception Fabrication Tests Assemblage et Emballage Système Environnement de développement Register Transfer Level (RTL) Portes logiques Layout Physique Toujours activé Activation via un trigger Interne Basé sur le temps

Basé sur une condition physique Externe Valeur d’entrée de l’utilisateur Valeur de sortie du composant Modification de la fonctionnalité Dégradation de performances Fuite d’information Deni de service Processeur Mémoire Entrées/Sorties Alimentation électrique Arbre d’horloge Distribution Taille Type Paramétrique Fonctionnel Structure Même layout Layout modifé Taxonomie détaillée

Figure 1.2 – Taxonomie des CTM.

Elle est organis´ee en 6 crit`eres diff´erents qui sont : – la phase d’insertion,

– les caract´eristiques physiques, – les effets,

1.5. Phase d’insertion

– le m´ecanisme d’activation, – le niveau d’abstraction, – l’emplacement.

Une description de ces diff´erentes cat´egories sera faite dans les parties suivantes.

1.5 Phase d’insertion

Il est int´eressant d’explorer les niveaux de fiabilit´e et de vuln´erabilit´e des diff´erentes ´etapes de r´ealisation d’un circuit int´egr´e comme pr´ecis´e dans [86]. La production d’une puce se d´ecompose en 5 phases principales :

– les sp´ecifications, – la conception, – la fabrication, – les tests,

– l’assemblage et l’emballage.

Certaines de ces ´etapes sont favorables `a l’ajout de parties malveillantes en toute discr´etion. Les auteurs dans [21] pr´esentent diff´erents sc´enarii, dans lesquels le circuit pourrait avoir subi des implantations de CTM. On peut constater que presque toutes les ´etapes de production d’un circuit int´egr´e sont potentiellement vuln´erables (cf figure 1.3

inspir´ee de [58]).

Spécification Conception Fabrication Test

Ajout de composants réalisés par un tiers

Utilisation de logiciels CAO Bibliothèques de cellules Production de wafers Photolithographie Gravure et dopage Vérification des wafers Découpage et encapsulation Niveau de suspicion Elevé Faible Mitigé Assemblage Emballage

Figure 1.3 – Niveau de suspicion des ´etapes de production d’un circuit int´egr´e

1.5.1 Acteurs

On distingue 4 principaux acteurs qui interviennent dans le processus de production d’un circuit int´egr´e :

– le concepteur, pour l’´etape de conception, – le fondeur, pour l’´etape de fabrication, – le testeur, pour l’´etape de test.

L’´etape d’assemblage/emballage peut ˆetre r´ealis´ee par le fondeur, l’entreprise cliente, ou par un sous-traitant.

1.5.2 Sp´ecifications

Les protocoles `a utiliser, les fonctions `a r´ealiser ainsi que les performances n´ecessaires sont d´efinis au cours de l’´etape de sp´ecification en prenant soin de respecter les besoins et les contraintes d´efinies du circuit int´egr´e. Dans la plupart des cas, cette ´etape est effectu´ee dans l’entreprise, dans la mesure o`u il n’est pas n´ecessaire d’avoir des ressources logicielles ou mat´erielles sp´ecifiques.

De fa¸con g´en´erale, `a la fin de cette phase, il est assez facile d’analyser les sp´ecifications afin de d´etecter s’il y a eu modifications non d´esir´ees. C’est pour cela qu’elles sont repr´ e-sent´ees sur fond vert dans sur la figure1.3. Les donn´ees relatives aux circuits peuvent ˆetre ais´ement contrˆol´ees, contrairement aux ´etapes de production suivantes. Des mises `a jour voire des changements complets des sp´ecifications du circuit sont r´ealisables sans entrainer de coˆuts suppl´ementaires ´elev´es.

1.5.3 Conception

Avant de fabriquer une puce, il faut tout d’abord en dessiner le sch´ema. La conception permet de sp´ecifier la fa¸con dont le circuit va ˆetre mod´elis´e afin de r´epondre au cahier des charges. Les outils de conception permettent de d´efinir les diff´erents blocs du circuit int´ e-gr´e ainsi que leur placement `a partir de la sp´ecification fonctionnelle de la puce. Chaque ´

el´ement est ensuite rout´e. Apr`es quelques v´erifications physiques LVS (Layout vs. Sche-matic) et DRC (Design Route Checking), des fichiers binaires sont g´en´er´es. On distingue principalement le GDSII. Il repr´esente le dessin des masques de la puce (le layout ). Ces masques sont utilis´es pendant les ´etapes de lithographie.

Les concepteurs accordent beaucoup d’importance `a la s´ecurit´e du circuit, dans la mesure o`u il existe un grand nombre d’influences ext´erieures possibles (dans le cas d’une application finale).

Il est possible le flot de production passe par un tiers, ce qui rajoute un risque d’inser-tion de CTM (cf figure1.3).

1.5. Phase d’insertion

1.5.3.1 Logiciels de Conception Assist´ee par Ordinateur (CAO)

L’utilisation des outils CAO pour les entreprises est indispensable dans le processus de conception des circuits int´egr´es. Le d´eveloppement de ces logiciels est un processus extrˆemement coˆuteux. Ce march´e de conception des outils CAO est domin´e par trois compagnies : Synopsys, Mentor Graphics et Cadence.

L’utilisation de logiciels de conception peut ´egalement constituer une source ext´erieure permettant l’ajout d’un cheval de Troie. En effet, le code source de ces outils n’est pas disponible. Si une faille de s´ecurit´e existe dans le logiciel utilis´e, tous les circuits r´ealis´es par ce logiciel seraient impact´es par cette faille. N´eanmoins, les produits CAO mis `a la vente sont extrˆemement surveill´es, beaucoup plus que les composants faits par un tiers. La fiabilit´e de cette ´etape est consid´er´ee donc comme mitig´ee.

1.5.3.2 Biblioth`eque de cellules

Les biblioth`eques de cellules sont une base de donn´ees informatiques qui regroupe un ensemble de portes ´electroniques basiques. Elles sont sollicit´ees `a diff´erents niveaux de conception d’un circuit int´egr´e [34]. On y trouve des informations concernant les r´esultats des simulations effectu´ees, la g´eom´etrie et les sp´ecifications ´electriques du circuit. Ces cellules sont fournies par le fondeur. Chaque fondeur peut avoir sa propre biblioth`eque.

Si les r`egles de conceptions de fonctions ´el´ementaires sont respect´ees (largeur de grille, niveaux d’interconnexions, etc.), il est envisageable de fabriquer une librairie en y ins´erant des CTM. Ainsi, cette nouvelle biblioth`eque constituerait un moyen d’insertion de CTM. Cependant, compte tenu de leurs petites tailles, il est int´eressant de fabriquer en interne ces fichiers sans faire appel `a un tiers ou de mener des investigations afin v´erifier leur int´egrit´e. Sur la figure 1.3, le niveau de confiance de cette ´etape est mitig´e.

1.5.4 Fabrication

Dans le processus d’´elaboration d’un circuit int´egr´e, la fabrication est la phase o`u on passe de la description num´erique `a une puce r´eelle. Au fil des ann´ees, le processus de fabrication s’est beaucoup am´elior´e, permettant de cr´eer des puces plus petites, plus rapides et ayant besoin de tr`es peu d’´energie. De fa¸con g´en´erale, le rendement d´epend de la maturit´e du processus de fabrication.

La fabrication de circuits int´egr´es requiert une salle blanche qui permet de minimiser au maximum l’introduction, la production et la conservation de particules pouvant alt´erer la qualit´e du circuit fabriqu´e. `A l’´echelle de la puce, un grain de poussi`ere peut ˆetre suffisamment gros pour empˆecher la circulation des ´electrons.

r´ealisation d’un circuit int´egr´e. Ils expliquent les nombreuses difficult´es et complexit´es de fabrication auxquelles de nombreux concepteurs fabless sont confront´es.

1.5.4.1 Production de wafer

La mati`ere premi`ere d’un circuit ´electronique est le silicium (Si). La silice, on parle aussi de dioxyde de silicium (SiO2), repr´esente 25 % de la masse de la croute terrestre. Elle existe `a l’´etat naturel sous forme de sable. Apr`es l’oxyg`ene, c’est l’´el´ement le plus r´epandu sur Terre. L’ars´eniure de gallium ou le germanium sont ´egalement des mat´eriaux utilis´es, mais pour des applications diff´erentes. Le germanium par exemple est utilis´e pour les composants optiques (diode `a faible chute de tension, cellules photovolta¨ıques multi-jonctions).

Le silicium est extrait de la silice, car il n’existe pas `a l’´etat pur. Afin de l’extraire, la silice est d´epos´ee dans un creuset en graphite puis elle est liqu´efi´ee. La temp´erature de fusion du silicium est de 1414˚C. Le silicium liquide est pur `a 98 %, mais est n´eanmoins purifi´e jusqu’`a atteindre un taux de puret´e proche de 99,999 %.

Le silicium obtenu est alors tir´e progressivement afin d’obtenir des lingots, sous couvert de conditions particuli`eres (temp´erature, vitesse de rotation, d´eplacement, etc.). Les figures

1.4et1.5pr´esentent le tirage d’un lingot et le produit final. Le diam`etre des lingots d´epend de la vitesse de tirage (150 mm, 200 mm ou 300 mm). Ce proc´ed´e est effectu´e selon la m´ethode de Czochralski [43].

Figure 1.4 – Tirage d’un lingot de silicium [10]

Le lingot de silicium est ensuite ´equeut´e puis d´ecoup´e en tranches qui sont par la suite polies et trait´ees chimiquement afin de s’assurer d’un r´esultat sans aucune asp´erit´e (cf fig

1.6). On obtient alors des galettes de silicium appel´ees wafers. L’´epaisseur des plaquettes obtenues est g´en´eralement de 380µm. Cette valeur permet de concilier finesse et r´esistance

1.5. Phase d’insertion

Figure 1.5 – Pr´esentation d’un lingot de silicium [10]

face aux contraintes m´ecaniques intervenant au cours des ´etapes de fabrication. Les wafers ayant des larges diam`etres pourront int´egrer plus de circuits int´egr´es `a nombre d’´etapes ´equivalentes.

Figure 1.6 – D´ecoupage du lingot de silicium en wafer [10]

Cette ´etape de base ne contient aucune donn´ee concernant le circuit final. Il n’y a donc aucun risque d’insertion de CTM `a ce niveau de production.

Les transistors sont la base des circuits int´egr´es. Bien que le silicium n’a pas les pro-pri´et´es ´electriques id´eales pour la r´ealisation de ces composants, il est possible de contrˆoler ses caract´eristiques ´electriques localement. Dans la suite de ce document, les ´etapes de fabrication d’un transistor seront d´ecrites.

1.5.4.2 Photolithographie

Les ´etapes du proc´ed´e de photolithographie commencent par l’application d’une pho-tor´esine sous forme d’un film fin sur la surface du substrat (le silicium). Une couche de dioxyde de silicium (SiO2) est ainsi cr´e´ee `a la surface du wafer pour servir d’isolant. Sur celle-ci s’ajoute une couche de nitrure de silicium pour former la grille du transistor puis une d’une r´esine photosensible. Par la suite, suivant le principe du pochoir, un rayonne-ment ultraviolet est projet´e `a travers un masque puis une lentille pour r´eduire la taille du motif du masque (cf fig 1.7). Ainsi, les zones de r´esine directement en contact avec le rayonnement sont insol´ees. L’´etape de d´eveloppement permet de supprimer les r´esines qui ont ´et´e insol´ees `a l’aide d’un solvant.

Figure 1.7 – Photolithographie [10]

La fabrication d’un circuit n´ecessite entre 35 et 40 masques. Le prix d’un masque est g´en´eralement de l’ordre du millier voire des centaines de milliers d’euros [99]. Son prix varie notamment en fonction de sa complexit´e et de sa pr´ecision. D’apr`es [87], le coˆut de d´eveloppement d’une technologie augmente de 30 % par nœud technologique.

Au cours d’une ´etape de photolithographie, le masque d’origine peut ˆetre substitu´e par un autre contenant un CTM. En effet, toute modification du masque entraine une directe r´epercussion sur le circuit achev´e. Il est alors extrˆemement difficile pour le concepteur du circuit d’origine de rep´erer les changements qui ont ´et´e effectu´es `a son insu, mˆeme s’il poss`ede une copie des masques utilis´es.

Cette phase constitue le seul moment o`u l’attaquant b´en´eficie d’un contrˆole quasi total sur la puce. Aussi, cette ´etape critique apparait sur fond rouge sur la figure 1.3.

1.5. Phase d’insertion

1.5.4.3 Gravure et dopage

Un m´elange de gaz (ou un bain d’acide) permet de supprimer les parties non prot´eg´ees par la r´esine, qui servent d’isolant et de grille au transistor, dans le but d’atteindre la couche de silicium. Ainsi disponible, la couche de silicium est dop´ee avec des atomes de phosphore (dopage N, ajout d’´electrons) ou de bore (dopage P, ajout de trous d’´electrons), ce qui permet de modifier les propri´et´es de conductivit´e du silicium.

Pour finir, la couche de r´esine restante au dessus de la grille est supprim´ee en fin de fabrication du transistor. Le transistor ainsi termin´e doit ˆetre isol´e. `A l’aide de masques, des lignes de m´etaux sont cr´e´ees afin de connecter les transistors entre eux (cf figure1.8).

Figure 1.8 – Ajout de couches de m´etal entre les transistors [10]

Cette ´etape ´etant tr`es rigoureuse et peu variable, un attaquant peut difficilement ef-fectuer des modifications. Le d´eni de service peut toutefois ˆetre une option `a envisager. Ajouter des impuret´es au design augmente les chances de ce dernier de ne pas fonctionner convenablement. Cette ´etape pr´esente un r´eel int´erˆet pour l’attaquant.

1.5.4.4 V´erification des wafers

Une fois les circuits termin´es, ils sont tous test´es `a l’aide d’une carte `a pointes, afin d’´eliminer les pi`eces non fonctionnelles et celles ayant subi des dommages durant le proc´ed´e de fabrication. Pour ce faire, les circuits sont tous soumis `a des vecteurs de tests et leurs comportements analys´es (tests param´etriques et fonctionnels).

Dans la mesure o`u de nouvelles modifications au sein du circuit n’ont pas lieu, il n’est pas envisageable d’ins´erer des CTM ici. N´eanmoins si les tests de v´erification sont en dehors de l’unit´e de fabrication, il est possible d’´echanger volontairement un wafer non infect´e par un wafer ne contenant que des puces ayant subi des modifications malicieuses.

Il est aussi envisageable qu’un lot complet de wafers non corrompus soient remplac´es. En r`egle g´en´erale, les vecteurs de tests utilis´es sont fiables, et cette ´etape est g´en´ era-lement r´ealis´ee en interne. Ils sont pr´epar´es pendant la phase de conception. Cette ´etape est donc repr´esent´ee avec un fond vert sur la figure 1.3.

1.5.5 Encapsulation et assemblage

`

A l’issue des tests, les wafers sont sci´es afin d’isoler les puces. Puis les circuits sont connect´es `a des boitiers. Ici un attaquant peut ins´erer, en plus du circuit initial, un circuit suppl´ementaire en guise de CTM. Cet ensemble est ainsi encapsul´e, pour ne former qu’une entit´e.

Bien que les ´equipements n´ecessaires `a l’encapsulation sont ´egalement coˆuteux, des entreprises d´ecident toutefois d’investir au moins dans ces installations pour r´ealiser elle-mˆeme cette ´etape.

1.5.6 Tests

D`es que les circuits sont fabriqu´es et encapsul´es, une nouvelle s´erie de tests est men´ee pour s’assurer de leur bon fonctionnement. Plus la complexit´e de la puce est ´elev´ee, plus la v´erification de leur comportement est compliqu´ee. Tous ces tests peuvent ˆetre coˆuteux et requ´erir beaucoup de temps de mise en œuvre. Dans [67], une vue assez g´en´erale des diff´erents types de tests sur circuits int´egr´es sont abord´es. Repr´esentant environ 40 % du coˆut total de production d’une puce, ces tests sont souvent r´ealis´es par un tiers [52]. Dans cette phase, peu d’informations de la puce sont disponibles (emplacement pr´ecis des portes logiques par exemple). N´eanmoins, les tests peuvent ˆetre volontairement n´eglig´es afin de mettre sur le march´e des circuits infect´es.

1.6 Caract´

eristiques physiques

Les caract´eristiques physiques d’un CTM permettent de d´efinir son ´etat g´en´eral `a l’int´erieur de la puce. On distingue :

– la distribution : un CTM peut ˆetre impl´ement´e de diverses fa¸cons sur une puce. La distribution permet de pr´eciser s’il occupe une r´egion bien d´etermin´ee sur la puce ou si, au contraire, il est dispers´e.

– la taille : cet ´el´ement permet de d´efinir la place occup´ee par le CTM dans la puce, ainsi que le nombre de composants n´ecessaires `a sa cr´eation.

– le type : il peut ˆetre fonctionnel ou param´etrique. Un CTM sera dit fonctionnel si son auteur ajoute ou supprime des transistors, des fils ou des portes logiques `a la puce initiale. Sinon, il sera qualifi´e de param´etrique. Dans ce cas, cela peut entraˆıner

1.7. Effets

une modification de la circuiterie par amincissement de fils, par affaiblissement des bascules ou des transistors voire par soumission de la puce `a des radiations.

– la structure : cette caract´eristique indique si les dimensions de la puce ont ´et´e mo-difi´ees, et s’il y a eu du changement dans le placement des composants de la puce originale. On parle de modification du layout.

1.7 Effets

Les effets d’un CTM peuvent modifier les propri´et´es param´etriques de la puce, changer sa fonctionnalit´e, ou mˆeme activer `a un moment choisi un d´eni de service. Des informations confidentielles peuvent ainsi ˆetre transmises.

Une d´efinition suppl´ementaire de la partie active du CTM est introduite dans [61]. On y diff´erencie les charges actives implicites des charges actives explicites.

Une charge active est explicite si elle modifie la valeur des signaux internes en cas d’activation. La puce peut alors avoir un comportement anormal, voire transmettre des informations secr`etes via les ports de communication.

Une charge active est implicite si elle induit une activit´e n’ayant pas d’influence directe sur les signaux internes du circuit. Elle peut provoquer des ´emissions d’ondes radio qui contiennent des informations critiques ou encore la destruction compl`ete du circuit infect´e. Dans [70], les auteurs pr´esentent un CTM bas´e sur des fuites d’informations secr`etes via des canaux auxiliaires tels que la consommation de courant.

1.8 M´

ecanisme d’activation

Le m´ecanisme d’activation va permettre le d´eclenchement du CTM. On parle du d´ e-clencheur ou de la gˆachette, ´egalement commun´ement appel´e le trigger. Un CTM peut en avoir plusieurs.

L’activation d’un CTM peut se faire grˆace une comparaison entre un ´etat du syst`eme et un ´etat d´efinit par l’attaquant. Dans la majeure partie des cas, le CTM s’active selon une condition bas´ee sur un ou plusieurs signaux internes de la puce. Il peut s’agir d’´etats logiques, d’une entr´ee sp´ecifique, de la valeur atteinte par un compteur, etc.

Il existe d’autres fa¸cons de d´eclencher le trigger. Par exemple, un CTM peut ˆetre ´egalement activ´e de fa¸con externe : il attendra un signal logique fourni par un m´ecanisme ajout´e par l’attaquant. On peut ´egalement retrouver des syst`emes de d´eclenchement `a distance.

Comme expliqu´e dans [11] et [61], on distingue les CTM dit s´equentiels de ceux dit combinatoires :

– un CTM s´equentiel est contrˆol´e par une machine d’´etat sensible `a un certain nombre de signaux internes et d´eclenche la partie active du CTM apr`es une succession de s´equences sp´ecifiques. Dans [98], les auteurs pr´esentent diff´erents types de CTM s´equentiels.

– un CTM combinatoire se d´eclenche lorsqu’une condition sp´ecifique se produit issue de fonctions logiques entre les signaux internes du syst`eme.

1.9 Niveau d’abstraction

On distingue principalement deux types d’infection des circuits int´egr´es. Dans le cas d’utilisation d’ASIC (Application Specific Integrated Circuit ), l’attaquant qui veut ins´erer un CTM poss`ede deux options d’int´egration :

– insertion au niveau RTL : la description mat´erielle est directement modifi´ee. Dans la mesure o`u la modification a lieu au niveau de l’´etape de conception, les masques cr´ees seront infect´es par le CTM.

– insertion au niveau de la fabrication par modification des masques g´en´er´es par le fichier GDS II ou par ajout de nouveaux masques :

– il peut utiliser les cellules de r´eserve (spare cells). Il sera contraint de refaire les masques d’interconnexions utiles pendant l’´etape de photolithographie (cf section

1.5.4.2). On aura ainsi une nouvelle g´en´eration de masques.

– il peut remplacer les cellules de remplissage (filler cells) par des cellules standards qui permettraient de mod´eliser le CTM voulu. Cette derni`ere approche est tr`es coˆuteuse (surtout en temps) et complexe (analyse du circuit notamment), dans la mesure o`u tous les masques doivent ˆetre chang´es et les interconnexions modifi´ees.

1.10 Emplacement

Un CTM peut ˆetre implant´e `a diff´erents endroits de la puce. Les blocs sensibles `a l’in-sertion de modifications malveillantes et ayant un rˆole majeur dans le bon fonctionnement du circuit sont :

– le processeur, – les m´emoires,

– les entr´ees et les sorties, – l’alimentation ´electrique, – l’arbre d’horloge.

1.11. Conclusion

1.11 Conclusion

Ce premier chapitre montre que pour des raisons ´economiques, le flot de production de circuits int´egr´es implique diff´erents acteurs. Les int´erˆets possiblement divergents de ces derniers mettent en cause la fiabilit´e des produits finaux. Des exemples d’insertion de CTM ont ´et´e soup¸conn´es au cours de cette derni`ere d´ecennie.

Par la suite, ce chapitre a pr´esent´e une taxonomie qui permet de classer les diff´erents types de CTM. Elle sera utilis´ee dans la suite de cette th`ese.

Pour finir, la description des ´etapes de production a montr´e que les phases de concep-tion et de fabricaconcep-tion sont les plus critiques.

Le chapitre suivant dresse l’´etat de l’art des techniques pr´eventives et des m´ethodes de d´etection des CTM une fois le circuit fabriqu´e.

Chapitre

2

M´ethodes de protection contre les CTM

Sommaire

2.1 Protection des circuits int´egr´es . . . 24

2.2 D´efinition de la strat´egie d’approche pour la protection de cir-cuits int´egr´es contre les CTM . . . 25

2.3 Mesures pr´eventives . . . 26

2.3.1 ”Built-In Self-Test ”, BIST . . . 26

2.3.2 Obfuscation . . . 26

2.3.3 Congestion des circuits. . . 27

2.3.4 Technique de chiffrement de logique mat´erielle . . . 27

2.3.5 Encodage des ´etats logiques . . . 27

2.4 Proc´ed´es de d´etection de CTM . . . 28

2.4.1 M´ethodes destructives . . . 29

2.4.2 M´ethodes non destructives . . . 31

2.5 Difficult´es techniques li´ees `a la d´etection de CTM. . . 35

2.5.1 Variabilit´e des proc´ed´es de fabrication . . . 36

2.5.2 Le vieillissement du circuit . . . 36

2.6 Positionnement de la th`ese par rapport `a l’´etat de l’art . . . 38

Dans le chapitre pr´ec´edent, il a ´et´e montr´e que les circuits int´egr´es peuvent ˆetre la cible d’insertion malveillante de CTM. Il est donc n´ecessaire de trouver des m´ethodes pour les d´etecter et tenter d’empˆecher leur insertion.

Ce chapitre d´efinit la notion de protection des circuits int´egr´es. Par la suite, il pr´esente l’´etat de l’art des diverses techniques (moyens pr´eventifs et strat´egie de d´etection) contre les CTM. Les difficult´es techniques li´ees `a la d´etection sont ´egalement d´ecrites.

Pour finir, ces pr´esentations permettent de positionner nos travaux de recherche.

2.1 Protection des circuits int´

egr´

es

D’apr`es [25], la d´efinition premi`ere du terme protection est :

”Protection : action ou fait de soustraire quelque chose (ou quelqu’un) `a un danger, `

a un risque qui pourrait lui nuire”

Dans notre contexte et selon cette d´efinition, l’objectif est de prot´eger le circuit int´egr´e pour garantir son int´egrit´e contre toute insertion de CTM.

Il existe des approches pr´eventives pour limiter l’ajout de CTM. Cependant, malgr´e un nombre important d’initiatives, il est impossible `a ce jour pas de se prot´eger `a 100 % contre l’insertion de CTM compte tenu d’une vari´et´e quasi-infinie de ces derniers. Dans [6], les auteurs mettent en avant la difficult´e de garantir l’int´egrit´e d’une puce car les techniques existantes sont jug´ees trop sp´ecifiques `a la pr´evention d’un certain type de CTM.

Puisque les m´ethodes de pr´evention n’assurent pas une protection totale, il est n´ eces-saire d’ajouter une ´etape de d´etection afin d’augmenter les niveaux de protection. Ces approches de d´etection sont souvent bas´ees sur des m´ethodes d’attaques (actives et pas-sives) synth´etis´ees dans [94]. Une ´etape de tests suppl´ementaires s’impose donc avant la mise sur le march´e de ces circuits. Ainsi, la d´efinition concernant la protection des circuits int´egr´es peut alors ˆetre ´etendue `a :

”et mettre des moyens en œuvre afin de s’assurer que l’´el´ement consid´er´e fonctionne bien et r´epond aux attentes qui lui sont demand´ees quelle que soit la situation.”

La combinaison des m´ethodes de pr´evention et de d´etection devrait permettre de mi-nimiser la quantit´e de puces non fiables sur le march´e.

2.2. D´efinition de la strat´egie d’approche pour la protection de circuits int´egr´es contre les CTM

2.2 D´

efinition de la strat´

egie d’approche pour la protection

de circuits int´

egr´

es contre les CTM

Pour garantir une protection optimale des circuits int´egr´es, la strat´egie d’approche pour la protection de circuits int´egr´es contre CTM peuvent se d´ecomposer en trois parties :

– la premi`ere ´etape d´efinit les moyens et les proc´ed´es de mise en œuvre. Cette phase s’accompagne de recherches bibliographiques sur les approches d´ej`a existantes sur le circuit int´egr´e concern´e. Il est imp´eratif de connaˆıtre l’´el´ement cible vis´e. Cela passe par l’analyse des sp´ecifications techniques ainsi que la conception et les protocoles utilis´es par le circuit (s’ils sont r´ef´erenc´es).

– il est par la suite important de d´ecider d’un protocole exp´erimental. Il faut identifier notamment les entr´ees/sorties disponibles et/ou n´ecessaires ainsi que les simulations et les tests `a effectuer. Selon l’´el´ement ´etudi´e, il peut ˆetre n´ecessaire de pr´eparer l’´echantillon (d´ecapsulation chimique ou m´ecanique par exemple). Ensuite, vient la phase de mesures d´efinie dans le plan d’action. Pour ce faire, un ou plusieurs bancs de mesures peuvent ˆetre requis. On distingue notamment les mesures de consommation, d’´emissions ´electromagn´etiques, de temps de calcul, etc.

– la derni`ere partie est la phase de traitements. Elle peut d´ependre des donn´ees me-sur´ees ou simplement se baser sur l’´etude du fonctionnement du circuit telle que la r´ealisation de tests statistiques pour en comprendre ou v´erifier un bon fonctionne-ment.

En r`egle g´en´erale, qu’il s’agisse de d´etections ou d’attaques envers un circuit int´egr´e, les approches sont assez similaires : il faut mod´eliser la menace afin de d´efinir les protections ad´equates.

La recherche de CTM est consid´er´ee comme une tˆache extrˆemement difficile, comme le soulignent les auteurs dans [94] et [46] qui dressent une vue d’ensemble g´en´erale des moyens de protection propos´es. On distingue d’une part les approches de d´etection de CTM apr`es que le circuit a ´et´e fabriqu´e et d’autre part les mesures pr´eventives qui ont pour but de limiter au maximum l’insertion de CTM. En d´epit de cette complexit´e, de nombreux chercheurs `a travers le monde ( ´Etats-Unis, France, Inde, ...) se sont pench´es et se penchent encore sur ce sujet. T´el´ecom ParisTech `a Paris, le LIRMM `a Montpellier, le CEA/EMSE `a Gardanne sont les principaux laboratoires en France qui travaillent sur cette th´ematique de recherche .

2.3 Mesures pr´

eventives

Les mesures pr´eventives permettent d’anticiper d’´eventuels ajouts de CTM. Le but est de complexifier le circuit au maximum afin qu’un attaquant ne dispose pas de place suffi-sante ou d’informations n´ecessaires et rendre ainsi difficile, voire impossible, l’implantation d’un CTM. Les termes de contrˆolabilit´e et d’observabilit´e sont tr`es souvent utilis´es dans le cadre des mesures pr´eventives :

– La contrˆolabilit´e permet de quantifier la difficult´e de forcer `a ’1’ ou `a ’0’ un nœud interne d’un circuit. Les signaux peu contrˆolables sont des candidats id´eaux pour constituer des d´eclencheurs de CTM. De nombreuses approches tentent de limiter, de dissimuler, voire de supprimer la faible contrˆolabilit´e de ces nœuds. En r`egle g´en´erale, un CTM doit ˆetre discret et doit s’activer selon une condition rare. – L’observabilit´e quantifie la complexit´e de propagation de la valeur interne d’un signal

vers une sortie primaire.

Le terme ”Design for Hardware Trust” regroupe l’ensemble des m´ethodes pr´eventives. Il a pour principe d’ajouter des caract´eristiques suppl´ementaires au circuit pour pr´evenir toute insertion et augmenter les chances de d´etection d’un CTM.

Les principales m´ethodes de pr´evention seront d´ecrites dans les sections suivantes.

2.3.1 ”Built-In Self-Test ”, BIST

Le “Built-In Self-Test ” est un m´ecanisme mat´eriel d’auto-test du composant. Le circuit est ainsi con¸cu int`egre 2 modes : un de fonctionnement normal et un autre de test [49]. Ce diagnostic de test peut ˆetre d´eclench´e par l’outil ou par son utilisateur. Cette m´ethode requiert une grande fiabilit´e.

Dans le cadre de la recherche de CTM, les auteurs de [22] pr´esentent un mode d’op´ era-tion “transparent” du syst`eme. Durant ce mode, une signature chiffr´ee est g´en´er´ee `a l’aide d’une cl´e de l’utilisateur. Ainsi, l’ajout d’un CTM aurait pour cons´equence la g´en´eration d’une signature diff´erente de celle attendue. La pr´esence du CTM sera alors d´etect´ee.

2.3.2 Obfuscation

L’obfuscation est une technique qui consiste `a modifier intentionnellement la structure ou la description d’un circuit int´egr´e. Ces modifications dissimulent les fonctionnalit´es, sans les modifier. Grˆace `a cette approche, la complexit´e du circuit est augment´ee. De plus, les m´ethodes de r´etroconception deviennent moins efficaces et beaucoup plus complexes pour reconstituer les op´erations effectu´ees.

La m´ethode de “BIST ” est compl´et´ee dans [20] par l’ajout d’obfuscation. Selon [20] et [19], le circuit pourrait fonctionner avec un comportement identique dans les deux modes

2.3. Mesures pr´eventives

distincts normal et obfusqu´e. De cette fa¸con, les nœuds du circuit ayant une probabilit´e d’apparition faible sont cach´es, rendant la tˆache d’insertion d’un CTM plus laborieuse pour un attaquant.

2.3.3 Congestion des circuits

Lorsque l’on dispose du layout, on remarque qu’il existe de l’espace non utilis´e sur la puce. Ces surfaces disponibles deviennent donc un refuge parfait pour l’insertion de CTM. Les auteurs de [15] cherchent `a identifier les moyens d’ajouter un CTM sans modifier le Placement et Routage d’un bloc logique cryptographique. Les r´esultats montrent que si la place disponible sur la puce est inf´erieure `a 20 %, alors l’insertion de CTM s’av`ere pratiquement impossible.

R´ecemment, les auteurs de [30] proposent une m´ethode sur FPGA pour pr´evenir l’in-sertion de CTM bas´ee sur le remplissage de cellules inutilis´ees. Le circuit est “rempli” `a l’aide notamment de registres `a d´ecalage et de cellules combinatoires n’ayant aucun effet sur son comportement puis est rout´e `a nouveau.

2.3.4 Technique de chiffrement de logique mat´erielle

Le chiffrement permet de dissimuler la fonctionnalit´e du circuit et d’augmenter la contrˆolabilit´e des signaux pouvant ˆetre consid´er´es comme des potentiels d´eclencheurs de CTM ([46]).

Dans [30], les auteurs ajoutent des portes logiques (ET et OU) `a un AES-128 bits, pour diminuer la quantit´e de signaux peu contrˆolables. Cette implantation requiert 7.3 % d’occupation suppl´ementaire. Une cl´e externe est requise afin d’assurer un fonctionnement normal du circuit. Sans cette cl´e, il est impossible de trouver les signaux pouvant servir de gˆachette au CTM. La contrˆolabilit´e des signaux est ainsi dissimul´ee quelle que soit le mode de fonctionnement de la puce, ce qui rend l’insertion d’un CTM furtif plus difficile.

2.3.5 Encodage des ´etats logiques

Les auteurs de [78] proposent une approche d’encodage de circuit. Elle repose sur la th´eorie des codes (cf [14] et [46]). Selon [80], les registres sont des ´el´ements facilement identifiables dans le layout d’une puce. Par r´etroconception, un attaquant peut utiliser des signaux de ces blocs pour ins´erer un CTM. L’encodage des ´etats logiques permet de masquer l’´etat des registres.

D’une part, la sortie de la logique combinatoire x de k bits est encod´ee `a l’aide d’une matrice afin de passer `a n bits (n > k) (cf figure 2.1). En parall`ele, un code g´en´er´e al´eatoirement sur n − k bits est encod´e pour passer `a n bits. Il est r´egl´e afin de trouver le

Logique Combinatoire Logique Combinatoire Entrées Sorties k k Circuit d’origine Etat d’origine Logique Combinatoire Logique Combinatoire Entrées Sorties k Etat encodé Décodeur J Encodeur G Encodeur aléatoire H Générateur de nombres aléatoires Registre Registre Registre ? Décodeur aléatoire K Décodeur J n n k n-k n n-k Circuit encodé x

Figure 2.1 – M´ethode d’encodage [78]

meilleur compromis entre la r´esistance aux injections de fautes et aux attaques par canaux cach´es (cf section2.4.2.1). Ensuite, une op´eration XOR est effectu´ee (cf section3.4.1) entre la sortie de la logique combinatoire et le code encod´es. Ce r´esultat est ´echantillonn´e dans un registre. De cette fa¸con, un attaquant pourra difficilement identifier la r´eelle fonctionnalit´e des signaux. Les sorties des registres sont ensuite d´ecod´ees avant de passer dans la logique combinatoire. L’op´eration est ensuite r´eit´er´ee. La connaissance de n − k bits (ou moins) sur les ´etats encod´es et masqu´es ne permet pas d’avoir des informations sur x.

D’autre part, un syst`eme d’alarme est mis en place. Si des attaques en faute affectent les valeurs enregistr´ees dans les registres, une alarme est alors d´eclench´ee.

2.4 Proc´

ed´

es de d´

etection de CTM

Plusieurs m´ethodes et suggestions de d´etection de CTM ont ´et´e propos´ees. On distingue cependant deux approches distinctes : l’une bas´ee sur les m´ethodes destructives et l’autre sur les non destructives.

2.4. Proc´ed´es de d´etection de CTM

2.4.1 M´ethodes destructives

Pour les m´ethodes destructives, il est n´ecessaire d’acc´eder physiquement au cœur du circuit `a ´etudier afin de pouvoir effectuer des observations directes. Certaines informations ne sont pas directement accessibles (´etats des m´emoires par exemple). Cela impose d’avoir recours `a des techniques de retrait de couches par proc´ed´es chimiques ou m´ecanique.

Ces techniques peuvent permettre de r´ecup´erer un certain nombre d’informations. On peut ainsi en d´eduire par r´etro-ing´enierie la mani`ere les algorithmes utilis´es ont ´et´e im-plant´es, les m´ecanismes de s´ecurit´e mis en place et/ou des donn´ees sensibles : on parle ainsi de r´etroconception.

La r´etroconception d’une puce est g´en´eralement utilis´ee afin de valider son authen-ticit´e. Cette approche est utilis´ee pour construire des mod`eles de r´ef´erence (on parle de Golden Model en anglais, not´e GM) s’il n’est pas possible d’avoir des puces de test. Le GM permet de valider que les mesures effectu´ees proviennent bien de circuits non corrompus et peut servir de r´ef´erence pour les ´etudes `a venir. Il sera g´en´eralement n´ecessaire d’avoir plusieurs GM de lots diff´erents dans le but de construire une biblioth`eque de r´ef´erences fournie. Dans [4], les auteurs utilisent des GM afin d’´etudier le comportement physique des puces et proc´eder `a des analyses statistiques. Leurs travaux futurs se basent sur une approche qui mod´elise et simule les puces utilis´ees comme GM.

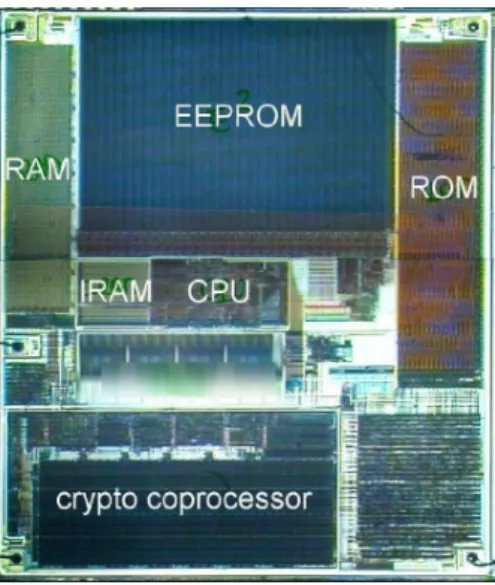

Un premier niveau d’analyse du circuit est effectu´e grˆace `a un microscope optique. Cela permet de trouver les diff´erents blocs comme illustr´e sur la figure 2.2.

![Figure 2.1 – M´ ethode d’encodage [78]](https://thumb-eu.123doks.com/thumbv2/123doknet/11580079.298051/41.892.106.804.162.545/figure-m-ethode-d-encodage.webp)