En vue de l’obtention du

DOCTORAT DE L'UNIVERSITE DE TOULOUSE III

Délivré par l’université Toulouse III - Paul SabatierDiscipline : Mathématiques Appliquées Option : Statistique

___________________________________________________________________________

Présentée et soutenue par : Caroline PACCARD Le : 6 Mai 2008

Titre :

Développement d’outils statistiques

pour la mise en place

de boucles de régulation en microélectronique

___________________________________________________________________________ JURY

M. Alain BACCINI, Président

M. Philippe BESSE, Directeur de Thèse M. René-Louis INGLEBERT, Rapporteur M. Christian LAVERGNE, Rapporteur M. François PASQUALINI, Examinateur

___________________________________________________________________________ Ecole Doctorale : Mathématiques et Applications

Unité de Recherche : : Laboratoire de Statistique et Probabilités U.M.R. CNRS 5583, Université Paul Sabatier, Toulouse III

Remerciements

Je tenais tout d’abord à remercier mon directeur de thèse, Philippe BESSE, qui a accepté d’encadrer ma thèse pendant ces 3 années. Grâces à ces précieux conseils et au temps qu’il m’a consacré, j’ai pu venir à bout de ce travail.

Ensuite, je tiens à remercier mon responsable industriel, François PASQUALINI, qui m’a suivi de manière consciencieuse pendant ma thèse. Je ne veux pas oublier mon responsable industriel par intermittence, Joost VAN HERK, qui m’a beaucoup apporté, mais qui n’a malheureusement pas pu suivre mon travail jusqu’à son terme, suite à son départ pour les Pays-Bas. Je remercie également Vincent TIRARD, qui s’est occupé de ma thèse pendant les 6 derniers mois. Il m’a énormément aidé à valoriser mon travail de thèse. Je voudrais aussi remercier Yves CHANDON qui m’a également beaucoup aidé grâce à ses connaissances en statistiques appliquées à l’industrie du semi-conducteur.

Je tiens aussi à remercier Christian LAVERGNE et René-Louis INGLEBERT pour avoir accepté d’être les rapporteurs de cette thèse. Grâce à leur relecture attentive et à leurs remarques pertinentes, j’ai pu grandement amélioré mon travail.

Je voudrais également remercier Alain BACCINI qui a accepté de faire partie de mon jury et qui a relu mon manuscrit avec attention.

Je veux aussi remercier toute l’équipe du groupe Contrôle des Procédés de STMicroelectronics : Arthur, Cyril, Séverine, Guillaume, Aymen, Marjorie, Stéphane, Stéphane, Yves, François, Vincent, Samuel, Hervé. Ils m’ont toujours aidé lorsque j’en ai eu besoin pendant ma thèse. Grâce à eux, j’ai pu passer 3 années instructives et agréables. Je veux également remercier les différents stagiaires qui ont contribué à la bonne ambiance du groupe : Benjamin et Stéphane.

Je tiens aussi à remercier tous mes amis qui m’ont soutenu pendant ces 3 années de thèse.

Je remercie du fond du cœur ma famille qui a toujours été là pour moi : mes parents et ma sœur, Véronique.

Enfin, je remercie Pierre-Matthieu pour ces nombreuses relectures attentives de ma thèse et pour tout ce qu’il m’ a apporté et m’apporte encore.

TABLE DES MATIERES

REMERCIEMENTS ...4

TABLE DES MATIERES ...5

LISTE DES ABREVIATIONS ...9

LISTE DES FIGURES ...13

INTRODUCTION GENERALE...18

CHAPITRE 1 : PROBLEMATIQUE ET CONTEXTE INDUSTRIEL...21

1 Présentation de la microélectronique ...21

1.1 Introduction ...21

1.2 Présentation générale...21

1.3 Définition d’un transistor ...21

1.4 Définition d’un circuit intégré ...22

1.5 Fabrication des circuits intégrés ...24

1.5.1 Etapes de fabrication...24

1.5.2 Empilement...25

1.5.3 Fin du procédé de fabrication ...26

1.5.4 Salle blanche...27

1.6 Industrie du semi-conducteur ...28

1.6.1 Application des circuits intégrés...28

1.6.2 Entreprises du semi-conducteur...28

1.7 Nouveaux enjeux de la microélectronique ...29

2 Le contrôle des procédés en microélectronique : état de l’art au début de la thèse ...30

2.1 Introduction ...30

2.2 Contrôle statistique des procédés (SPC)...30

2.2.1 Introduction ...30

2.2.2 Echantillonnage de la mesure ...31

2.2.3 Calcul des indicateurs ...32

2.2.4 Cartes de contrôle ...34

2.2.5 Calcul de la capabilité d’un procédé...37

2.3 Contrôle statistique des équipements de procédé (FDC)...41

2.3.1 Introduction ...42

2.3.2 Mise en place d’indicateurs et de limites de contrôle ...42

2.3.3 Exemple de contrôle FDC ...44

3 Présentation des boucles de régulation...46

3.1 Introduction ...46

3.2 Niveaux d’ajustement d’une boucle de régulation ...46

3.3 Le modèle du procédé ...50

3.4 Les différents types de boucles de régulation...50

3.4.1 Boucle feedback ...50

3.4.2 Boucle feedforward ...52

3.4.3 Boucle basée sur les paramètres des équipements ...52

3.5.1 EWMA ...54

3.5.2 Le contrôleur prédicteur correcteur ...55

3.5.3 Double EWMA...56

3.5.4 Double EWMA basée sur le temps ...56

3.5.5 Filtre de Kalman ...57 3.5.6 Prédiction non-paramétrique...58 3.5.7 Autres méthodes ...60 4 Problématique de la thèse...62 4.1 Introduction ...62 4.2 Méthodologie...62 4.2.1 Motivations...62 4.2.2 Etudes préliminaires ...63 4.2.3 Modélisation du procédé...63

4.2.4 Choix de l’algorithme de régulation ...64

4.2.5 Description des scénarios opérationnels ...64

4.2.6 Implémentation de la boucle dans ProcessWORKS ...64

4.2.7 Diagnostic de la boucle...65

4.3 Etat de l’art des boucles de régulation...65

4.3.1 A Crolles2...65

4.3.2 Dans la littérature en microélectronique ...66

4.4 Apport de la thèse...66

CHAPITRE 2 : LA MESURE EN MICROELECTRONIQUE ...68

1 Provenance des différentes mesures ...68

1.1 Introduction ...68

1.2 Mesures en ligne...68

1.2.1 Définition...68

1.2.2 Echantillonnage des mesures ...70

1.2.3 Equipements de métrologie ...72

1.2.4 Contrôle des mesures...74

1.3 Mesures électriques ...74

1.3.1 Définition...74

1.3.2 Echantillonnage ...74

1.3.3 Equipements de métrologie ...74

1.4 Mesures sur les équipements de procédé...75

1.4.1 Définition...75

1.4.2 Echantillonnage ...75

1.4.3 Contrôles de mesures...76

1.5 Les autres mesures...76

2 Qualité de la mesure ...77

2.1 Introduction ...77

2.2 Généralités...77

2.3 Capabilité d’un équipement de métrologie...77

2.3.1 Définition...77

2.3.2 Procédure standard de calcul ...78

2.3.3 Limites de la procédure classique...78

2.3.4 Nouvelle procédure proposée ...79

2.3.5 Prise en compte de mesures non-indépendantes ...79

2.3.6 Calcul de la capabilité de plusieurs d’équipements de métrologie ...86

2.3.7 Calcul de la capabilité dans le cas d’une mesure évolutive ...89

2.4 Contrôle Statistiques de Procédés des équipements de métrologie ...91

2.5 Autres indicateurs de qualité ...92

2.6 Problématiques opérationnelles du calcul de la capabilité ...93

2.6.1 Problématique...93

CHAPITRE 3 : METHODOLOGIE POUR LA MISE EN PLACE DE

BOUCLES DE REGULATION...95

1 Motivations pour la mise en place d’une boucle de régulation ...96

1.1 Introduction ...96

1.2 Diminution de la variabilité d’un paramètre du procédé ...96

1.3 Diminution de la variabilité d’un paramètre secondaire lié au paramètre du procédé...97

2 Description du procédé à réguler...100

2.1 Introduction ...100

2.2 Description de l’atelier ...100

2.3 Description du procédé de fabrication...103

2.4 Description de l’équipement de procédé ...105

2.5 Description du plan de contrôle...105

2.5.1 Description du plan de contrôle SPC...105

2.5.2 Description du plan de contrôle FDC ...107

2.6 Description de la boucle de régulation existante ...107

3 Etudes préliminaires sur les données ...112

3.1 Introduction ...112

3.2 Modélisation macroscopique du procédé ...112

3.3 Etude sur les paramètres du modèle ...113

3.3.1 Etude de l’épaisseur de PSG avant polissage...113

3.3.2 Etudes de l’épaisseur de PSG après polissage ...118

3.3.3 Etude du profil de l’épaisseur polie ...123

3.3.4 Etude du temps de polissage...125

3.3.5 Etude de l’usure du pad ...126

3.4 Etude des paramètres clés corrélés au paramètre à réguler...127

3.5 Equipements de métrologie et fiabilité pour les mesures des paramètres du modèle ...131

3.5.1 Epaisseur de PSG avant polissage ...131

3.5.2 Epaisseur de PSG après polissage ...132

3.6 Equipements de procédé reliés aux paramètres du modèle ...133

3.6.1 Epaisseur de PSG avant polissage ...133

3.6.2 Epaisseur de PSG après polissage ...133

3.7 Tableau récapitulatif...133

4 Modélisation statistique du procédé ...135

4.1 Introduction ...135

4.2 Choix du paramètre à modéliser...135

4.2.1 Première définition de la vitesse de polissage ...135

4.2.2 Définition de la quantité de matière polie...136

4.2.3 Définition d’une vitesse de polissage basée sur la Quantité de Matière Polie ...139

4.3 Revue des modèles envisagés...145

4.4 Test des différents modèles ...146

4.4.1 Données utilisées pour la modélisation...146

4.4.2 Critères graphiques d’évaluation des modèles...146

4.4.3 Modélisation linéaire indépendante du numéro du pad ...147

4.4.4 Modélisation linéaire dépendant du numéro du pad ...149

4.4.5 Modélisation non-linéaire dépendant du numéro du pad...152

4.4.6 Choix du modèle...155

5 Optimisation de la boucle de régulation...156

5.1 Introduction ...156

5.2 Contexte de la régulation...157

5.2.1 Paramètres à réguler et à ajuster ...157

5.3 Simulation du procédé de fabrication ...162

5.3.1 Principe de la simulation ...162

5.3.2 Limites de la simulation du procédé de polissage...166

5.3.3 Améliorations envisageables de la simulation ...170

5.4 Simulation d’une boucle de régulation ...171

5.4.1 Simulation d’une régulation lot à lot ...171

5.4.2 Simulation d’une régulation à l’intérieur des lots...172

5.5 Comparaison des algorithmes pour la régulation lot à lot ...173

5.5.1 Optimisation des algorithmes de régulation...173

5.5.2 Utilisation des données de l’échantillon de test ...180

5.5.3 Utilisation des données d’une autre tête de polissage...181

5.5.4 Sensibilité des algorithmes aux valeurs manquantes ...182

5.5.5 Sensibilité des paramètres des algorithmes...184

5.5.6 Facilité de mise en œuvre des algorithmes ...190

5.5.7 Conclusion ...191

5.6 Optimisation de l’algorithme pour la régulation à l’intérieur des lots...193

5.7 Description et gain de la boucle de régulation choisie ...194

6 Conclusion ...198

CONCLUSIONS ET PERSPECTIVES ...199

BIBLIOGRAPHIE ...201

ANNEXES...205

Annexe A : Utilisation du logiciel CpMArt pour le calcul de la capabilité d’une mesure évolutive ...205

Annexe B : Industrialisation d’une boucle de régulation...228

Annexe C : Article soumis au Journal of Quality Technology « Gage R&R study for several Measurement Systems with non-independent Measured Objects ›› ...232

Annexe D : Présentation d’un poster à la conférence AEC/APC à Indian Wells «Run-to-Run Control of CMP Copper Process »...252

Liste des abréviations

ACPAnalyse en Composantes Principales ou Principal Components Analysis (PCA)

BE Back-End

CD Dimension Critique ou Critical Dimension

CMP Polissage Mécano-Chimique ou Chemical Mechanical Polishing Cpk Capabilité d’un procédé

Cpm Capabilité d’une mesure CPMD Capacité PMD

CpmG Capabilité globale de la mesure DEF Défectivité

EPD End Point Detection

EWMA Exponentially Weighted Moving Average FDC Fault Detection and Classification

FE Front-End

FOUP Front Opening Unified Pod

IMA Moyenne mobile intégrée ou Integrated Moving Average IMM Integrated Metrology Module

ITRS International Technology Roadmap for Semiconductors LCL Lower Control Limit

LSL Lower Specification Limit

LSP Laboratoire de Statistique et Probabilités de Toulouse

MEB Microscope à balayage électronique ou Scanning Electron Microscopy (SEM) MOS Metal Oxide Semiconductor

MSE Erreur moyenne quadratique ou Mean Square Error

nm Nanomètre

NMOS Negative Metal Oxide Semiconductor NPW Non Production Wafer ou wafer témoin

OV Décalage ou Overlay

PCC Contrôleur Prédicteur Correcteur ou Predictor Corrector Controller PMD Pré-métal diélectrique

PMOS Positive Metal Oxide Semiconductor ppm Partie par million

PSG Phosphorus-doped Silicon Glass PT Test Electrique ou Parametric Test R2R Run-to-run ou boucle de régulation

SA Stand-Alone

Scribe

Lines Zones de découpe

SH Hauteur de marche ou Step Height Slurry Composé chimique facilitant le polissage

TH Epaisseur ou Thickness TPMD Thickness PMD

UCL Limite de Contrôle Haute ou Upper Control Limit

USL Limite de Spécification Haute ou Upper Specification Limit Wafer Plaque de silicium vierge

Liste des tableaux

Tableau 1 : Echantillonnage des mesures ...32

Tableau 2: Correspondance Cpk / ppm...41

Tableau 3: Echantillonnage des mesures en fonction du type d’équipement de métrologie. ...70

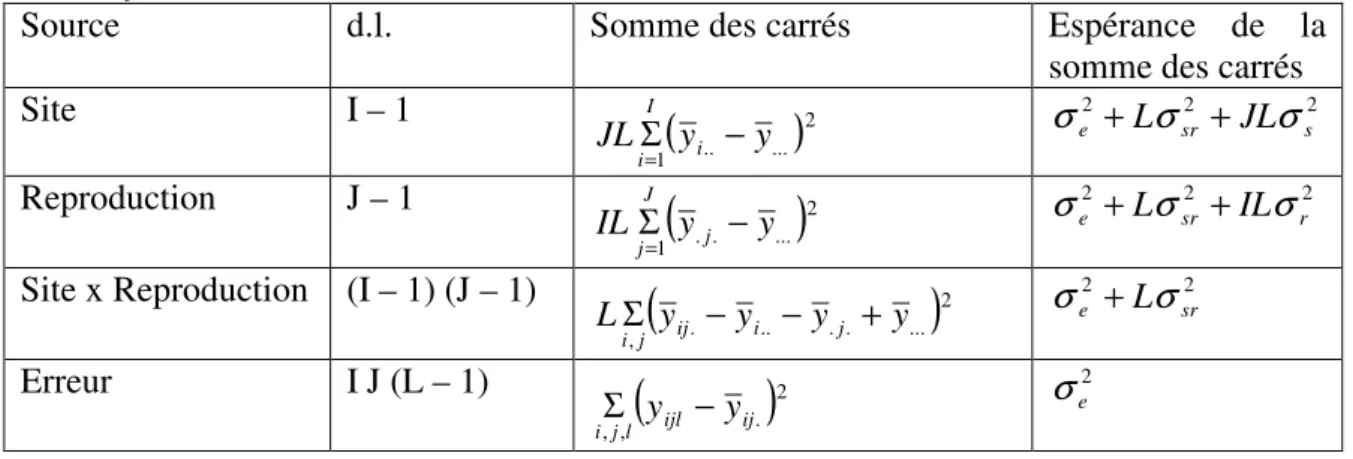

Tableau 4 : Table d’analyse de variance pour une modélisation de la mesure avec plusieurs wafers ...81

Tableau 5 : Table d’analyse de variance pour une modélisation de la mesure avec un seul wafer ...81

Tableau 6: Table d’analyse de variance pour une modélisation de la mesure avec plusieurs wafers sans prise en compte de l’effet wafer...84

Tableau 7: Exemple de table de mesures pour le calcul de la capabilité...93

Tableau 8: Limites de spécification pour l’épaisseur de PSG avant polissage...113

Tableau 9: Limites de spécification pour l’épaisseur de PSG après polissage ...118

Tableau 10: Estimation de l’effet des sites de mesure sur l’épaisseur polie...123

Tableau 11: Limites de spécification pour la capacité électrique PMD ...127

Tableau 12: Equipements de métrologie utilisés pour la mesure de l’épaisseur de PSG avant polissage ...131

Tableau 13: Capabilité et utilisation des équipements de métrologie utilisés pour la mesure de l’épaisseur de PSG avant polissage ...132

Tableau 14: Equipements de métrologie utilisés pour la mesure de l’épaisseur de PSG après polissage ...132

Tableau 15: Capabilité et utilisation des équipements de métrologie utilisés pour la mesure de l’épaisseur de PSG après polissage ...132

Tableau 16: Equipements de procédés et chambres utilisés pour le dépôt du PSG...133

Tableau 17: Equipements de procédés utilisés pour le polissage du PSG...133

Tableau 18: Tableau récapitulatif de la boucle de régulation de polissage PMD...134

Tableau 19: Hauteur de marche pour les différentes technologies ...141

Tableau 20: Variables utilisées pour l’estimation de δ et γ ...142

Tableau 21: Estimation de δ et γ pour les 4 têtes de polissage avec p-values associées ...142

Tableau 22: Estimation des coefficients du Modèle ...147

Tableau 23: Estimation des effets fixes du Modèle 2 ...150

Tableau 24: Estimation des effets aléatoires du Modèle 2 ...150

Tableau 25: Estimation des effets fixes du Modèle 3 ...153

Tableau 26: Estimation des effets aléatoires du Modèle 3 ...153

Tableau 27: Résultats des algorithmes pour l’erreur quadratique avec l’échantillon d’apprentissage ...179

Tableau 28: Système de notation pour l’évaluation des différents critères ...180

Tableau 29: Performance des algorithmes pour l’erreur quadratique de l’échantillon d’apprentissage ...180

Tableau 30: Résultats des algorithmes pour l’erreur quadratique de l’échantillon de test ...180

Tableau 31: Performance des algorithmes pour l’erreur quadratique de l’échantillon de test ...181

Tableau 32: Résultats des algorithmes pour l’erreur quadratique sur les données de la 3ème tête de polissage...181

Tableau 33: Performance des algorithmes pour l’erreur quadratique sur une nouvelle

tête de polissage ...182

Tableau 34: Performance des algorithmes pour la sensibilité aux valeurs manquantes ...183

Tableau 35: Performance des algorithmes pour la sensibilité de leurs paramètres ...190

Tableau 36: Performance des algorithmes pour leur facilité de mise en œuvre ...191

Tableau 37: Performance des algorithmes selon différents critères ...192

Tableau 38: Gain en terme d’erreur quadratique à l’aide de l’algorithme EWMA optimisée ...193

Tableau 39: Moyenne, écart-type et erreur quadratique de la distribution des épaisseurs en production et de la distribution simulée avec la régulation proposée ...195

Tableau 40: Moyenne, écart-type et erreurs quadratiques des distributions d’épaisseur avant et après régulation ...197

Tableau 41: Format du fichier des mesures ...210

Tableau 42: Format du fichier de la mesure du CD grille après gravure...210

Tableau 43: Format du fichier du wafer de matching...211

Tableau 44: Fichier du wafer de matching pour la mesure du CD grille...211

Tableau 45: Exemple de format de fichier pour les limites de spécifications, technologies et unités...211

Tableau 46: Limites de spécifications, technologie et unité pour la mesure du CD grille ...212

Liste des figures

Figure 1: Schéma d’un transistorNMOS...22

Figure 2: Fonctionnement d’un transistor NMOS mis sous tension...22

Figure 3: Circuit intégré...23

Figure 4: Evolution du nombre de transistors par puce dans le temps ...24

Figure 5: Empilement d’un circuit intégré...26

Figure 6 : Vu de coupe d’un wafer au MEB...26

Figure 7 : Wafer en fin de procédé de fabrication ...27

Figure 8 : Détail de puces en fin de procédé de fabrication...27

Figure 9 : Puce mise en boîtier ...27

Figure 10: Schéma de la salle blanche...28

Figure 11: Chiffre d’affaire en millions de dollars des 11 entreprises les plus importantes du semiconducteur en 2006...28

Figure 12: Une étape de mesure suivant une étape de procédé ...30

Figure 13 : Résumé du fonctionnement du SPC...31

Figure 14: Lot, wafer, sites de mesure...32

Figure 15 : Décroissance des poids exponentiels pour différentes valeurs de λ...33

Figure 16: Lissage des mesures par lot avec l’EWMA...34

Figure 17: Fonctionnement du filtre itératif pour le calcul des limites de contrôle...36

Figure 18: Exemple de carte de contrôle pour la moyenne et l’EWMA...37

Figure 19: Définition du Cp pour une distribution normale ...38

Figure 20: Définition du Cp pour une distribution non-normale...39

Figure 21: Définition du Cpk pour une distribution normale ...40

Figure 22: Définition du Cpk pour une distribution non-normale...40

Figure 23: Plan d’action pour les Cpk d’un paramètre clé ...41

Figure 24: Résumé du fonctionnement de la FDC...42

Figure 25: Différence entre limites équipement, limite de rejet et limite FDC ...44

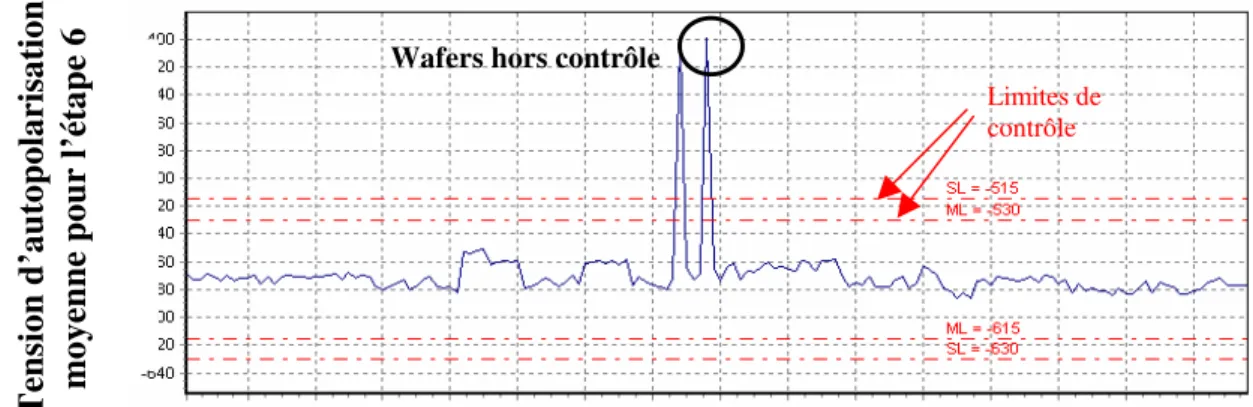

Figure 26: Représentations temporelle de la tension d’autopolarisation pendant un procédé de gravure sèche ...44

Figure 27: Moyenne de la tension d’autopolarisation pendant un procédé de gravure sèche...45

Figure 28: Variabilité du procédé site à site ...48

Figure 29: Variabilité du procédé wafer à wafer ...48

Figure 30: Variabilité du procédé lot à lot ...49

Figure 31: Fonctionnement d’une boucle de régulation de type feedback ...51

Figure 32: Fonctionnement d’une boucle de régulation de type feedforward ...52

Figure 33: Fonctionnement d’une boucle de régulation basée sur des paramètres équipements ...53

Figure 34: Fonctionnement d’une boucle de régulation feedback/feedforward ...53

Figure 35: Illustration du principe de la prédiction non-paramétrique ...60

Figure 36: Variables d’entrée et de sortie d’un procédé de fabrication...62

Figure 37: Principe de l’atelier de photolithographie ...65

Figure 38: Epaisseur et hauteur de marche (coupe d’un wafer) ...69

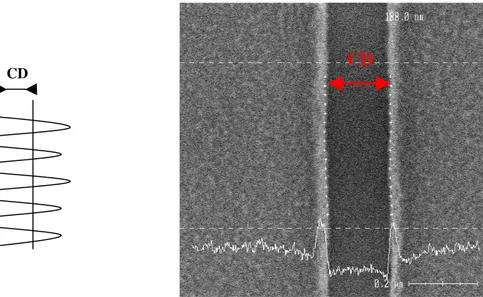

Figure 39: Dimension critique (coupe d’un wafer)...69

Figure 40: Nombre de particules (wafer vu de dessus)...69

Figure 41: Définition de l’overlay au niveau d’une puce ...69

Figure 42: Principe de l’échantillonnage des mesures...70

Figure 45: Balayage de la zone à mesurer et signal obtenu en sortie ...72

Figure 46: Motifs de mesure dense et isolé ...73

Figure 47: Principe de la scatterométrie ...73

Figure 48: Grandeurs mesurées en scatterométrie ...74

Figure 49: Evolution dans le temps de la pression sur la zone 1 d’un wafer...75

Figure 50: Evolution dans le temps de la pression sur la zone 2 d’un wafer...75

Figure 51: Evolution dans le temps de la pression sur la zone 3 d’un wafer...75

Figure 52: Profils des wafers d’un même lot ...79

Figure 53: Plan d’expérience mis en place pour le calcul de la capabilité d’un équipement de mesure...80

Figure 54: Moyenne des estimateurs de la variance du procédé ...85

Figure 55: Méthodologie suivie pour le calcul d’un Cpm global pour plusieurs équipements de métrologie ...87

Figure 56: Erreurs individuels et erreur globale pour plusieurs équipements de métrologie ...89

Figure 57: Mesures du CD en 17 sites d’un wafer en fonction du numéro de la mesure ...91

Figure 58: Mesure d’un équipement en fonction de la valeur réelle (non-linéarité) ...92

Figure 59: Schéma d’une boucle de régulation...95

Figure 60: Procédé stable et procédé à réguler ...96

Figure 61: Evolution hebdomadaire du Cpk pour l’épaisseur de PSG après polissage ...97

Figure 62: Relation entre épaisseur électrique et capacité électrique ...98

Figure 63: Corrélation entre l’épaisseur de PSG et la capacité au niveau site ...98

Figure 64: Evolution hebdomadaire de la distribution du paramètre électrique TPMD ...99

Figure 65: Evolution hebdomadaire du Cpk du paramètre électrique TPMD ...99

Figure 66: Dépôt de la résine ...100

Figure 67: Insolation de la résine à travers un masque...101

Figure 68: Développement de la résine sur une surface non-plane ...101

Figure 69: Développement de la résine sur une surface plane...102

Figure 70: Equipement de polissage vu de dessus...102

Figure 71: Principe du polissage d’un wafer ...103

Figure 72: Empilement avant le polissage PMD ...103

Figure 73: Empilement après le polissage PMD...104

Figure 74: Etape de contact tungstène ...104

Figure 75: Etape de déposition de cuivre...104

Figure 76: Cartes de contrôle associées à l’épaisseur après polissage PMD...105

Figure 77: Cartes de contrôle associées au temps de polissage PMD ...106

Figure 78: Carte de contrôle NPW sur la vitesse de polissage ...106

Figure 79: Carte de contrôle NPW sur la contamination...107

Figure 80: Empilement avant le dépôt PSG...108

Figure 81: Définition de l’épaisseur de PSG avant et après polissage ...109

Figure 82: Epaisseur polie ...110

Figure 83 : Empilement avant et après polissage...112

Figure 84: Modélisation macroscopique du procédé de polissage ...113

Figure 85: Densité de l’épaisseur de PSG avant polissage au niveau site ...114

Figure 86: Illustration du « chapeau mexicain » au niveau du dépôt PSG ...114 Figure 87: Evolution hebdomadaire et mensuelle des boxplots de l’épaisseur de PSG

polissage...115

Figure 89: Part de la variance site, wafer et lot par rapport à la variance totale pour l’épaisseur de PSG avant polissage...116

Figure 90: Profils de wafers avant polissage, forme de « chapeaux mexicains »...118

Figure 91: Profils de wafers avant polissage, forme de « cuvettes »...118

Figure 92: Densité de la mesure au niveau site de l’épaisseur de PSG après polissage ...119

Figure 93: Zones de pression variables sur l’équipement de polissage ...119

Figure 94: Evolution hebdomadaire et mensuelle des boxplots de l’épaisseur de PSG après polissage ...120

Figure 95: Evolution hebdomadaire et mensuelle du Cpk de l’épaisseur de PSG après polissage...120

Figure 96: Part de la variance site, wafer et lot par rapport à la variance totale pour l’épaisseur de PSG après polissage...121

Figure 97: Zones de pressions variables sur l’équipement de polissage ...121

Figure 98: Mapping 17 points standard ...121

Figure 99: Profils de wafers après polissage, forme de « chapeaux mexicains »...122

Figure 100: Profils de wafers après polissage, forme de « cuvettes » ...122

Figure 101: Profil atypique d’un wafer après polissage ...122

Figure 102: Epaisseur polie en fonction du numéro du site...123

Figure 103: Epaisseur polie en fonction de la distance au centre du wafer...124

Figure 104: Profils typiques de l’épaisseur de PSG polie (quelques exemples)...125

Figure 105: Variation du temps de polissage en cours de la vie d’un pad...126

Figure 106: Variation du temps de polissage au sein d’un lot...126

Figure 107: Histogramme du nombre de wafers polis par pad...127

Figure 108: Corrélation entre le paramètre électrique de capacité et l’épaisseur de PSG après polissage...127

Figure 109: Densité de la capacité électrique PMD au niveau site...128

Figure 110: Interface PSG/Cuivre ...128

Figure 111: Evolution hebdomadaire et mensuelle des boxplots de la capacité PMD ...129

Figure 112: Evolution par semaine et par mois du Cpk de la capacité PMD ...129

Figure 113: Part de la variance site, wafer et lot par rapport à la variance totale pour la capacité électrique PMD ...130

Figure 114: Profils de wafers pour l’épaisseur électrique PMD...131

Figure 115: Modélisation macroscopique du procédé de polissage ...135

Figure 116: Quantité de matière polie ...135

Figure 117: Evolution de l’épaisseur polie en fonction du temps de polissage pour un wafer ...136

Figure 118: Profil d’un wafer avant polissage PMD ...137

Figure 119: Schéma de la quantité de matière polie ...137

Figure 120: Quantité de matière des bosses...138

Figure 121: Quantité de matière polie lorsque γ = 1...138

Figure 122: Quantité de matière plane...138

Figure 123: Evolution de la quantité de matière polie en fonction du temps de polissage pour un wafer ...140

Figure 124: Wafer vierge avec une couche de PSG déposée...140

Figure 125: Relation entre vitesse de polissage et usure du pad pour 4 pads différents ...143

Figure 126: Relation entre vitesse de polissage (qui ne prend pas en compte les

bosses) et usure du pad pour 4 pads différents ...144

Figure 127: Graphiques de diagnostics du Modèle1...148

Figure 128: Vitesse de polissage en fonction de l’usure du pad pour différents pads ...149

Figure 129: Graphiques de diagnostic du Modèle 2 ...151

Figure 130: Vitesse de polissage en fonction de l’usure du pad pour différents pads ...151

Figure 131: Vitesse de polissage en fonction de l’usure du pad pour différents pads ...152

Figure 132: Maximum de vraisemblance en fonction de la valeur de la constante du modèle...153

Figure 133: Graphiques de diagnostic du Modèle 3 ...154

Figure 134: Vitesse de polissage en fonction de l’usure du pad pour différents pads ...155

Figure 135: Schéma de la régulation à l’intérieur des lots pour le Lot t...158

Figure 136: Schéma de la régulation lot à lot ...159

Figure 137: Schéma de la boucle de régulation feedback/feedforward...159

Figure 138: Connaissance de F à l’aide des données de production...163

Figure 139: Quantité de matière polie ...163

Figure 140: Hypothèse sur le comportement de F ...164

Figure 141: Comportement du procédé de polissage F ...166

Figure 142: Ecart-type de l’erreur sur l’épaisseur simulée en fonction du taux d’ouverture et du rapport Temps2 sur Temps...169

Figure 143: Densité d’erreur sur l’épaisseur simulée ...170

Figure 144: Optimisation du poids de la régulation pour l’algorithme EWMA sans remise à zéro ...174

Figure 145: Optimisation du poids de la régulation pour l’algorithme EWMA...175

Figure 146: Erreurs quadratiques pour les différents algorithmes en fonction du pourcentage de données manquantes aléatoires...183

Figure 147: Erreurs quadratiques pour les différents algorithmes en fonction du pourcentage de données manquantes consécutives...183

Figure 148: Variation de l’erreur quadratique en fonction de ω pour la méthode EWMA...184

Figure 149: Variations de l’erreur quadratique en fonction de ω1 et ω2 pour la méthode PCC ...185

Figure 150: Variations de l’erreur quadratique en fonction de ω1 et ω2 pour la méthode double EWMA ...185

Figure 151: Variations de l’erreur quadratique en fonction de ω1 et ω2 pour la méthode EWMA basée sur l’usure ...186

Figure 152: Variations de l’erreur quadratique en fonction de R pour le filtre de Kalman...187

Figure 153: Variations de l’erreur quadratique en fonction de Q pour le filtre de Kalman...187

Figure 154: Variations de l’erreur quadratique en fonction de P0 pour le filtre de Kalman...188

Figure 155: Variations de l’erreur quadratique en fonction de

θ

0 pour le filtre de Kalman...189EWMA...193

Figure 158: Fonctionnement de la boucle de régulation du polissage PMD ...194

Figure 159: Comparaison des densités de l’épaisseur des données de production et l’épaisseur simulée avec la régulation proposée...195

Figure 160: Empilement avant et après polissage cuivre...196

Figure 161: Distribution des mesures d’épaisseur TEOS avant et après régulation..196

Figure 162: Autocorrélation avant et après régulation ...197

Figure 163: Principe de la photolithographie et de la gravure...205

Figure 164: Mesure du CD grille après l’étape gravure ...205

Figure 165 : Croissance de carbone due à la mesure SEM...206

Figure 166: Evolution de la mesure du CD après gravure avec un SEM ...207

Figure 167: Evolution de la mesure de 17 sites avec l’équipement QS93001...208

Figure 168: Evolution de la mesure de 17 sites avec l’équipement QS93005...209

Figure 169: Evolution de la mesure de 17 sites avec l’équipement QS93007...209

Figure 170: Evolution de la mesure de 17 sites avec l’équipement QS93009...210

Figure 171: Accès aux différents rapports dans CpMArt ...222

Figure 172: Rapport en .csv du logiciel CpMArt ...222

Figure 173: Rapport Excel (1/2) du logiciel CpMArt...223

Figure 174: Rapport Excel (2/2) du logiciel CpMArt...223

Figure 175: Evolution de la mesure du CD en fonction de la numéro de la répétition et de la reproduction pour chaque site ...224

Figure 176: Evolution de la mesure en fonction du numéro du site et du numéro du de la reproduction ...225

Figure 177: Densité d’erreur pour chaque équipement de mesure et densité d’erreur pour l’ensemble des équipements ...226

Figure 178: Accès aux graphiques dans CpMArt ...227

Figure 179: Fonctionnement de la boucle de régulation du polissage PMD ...230

Figure 180: Communication de ProcessWorks avec les équipements...230

Figure 181: Communication avec ProcessWorks dans le cadre de la régulation CMP PMD...231

Introduction Générale

Contexte

Ma thèse a été effectuée dans le cadre d’une convention CIFRE (Conventions Industrielles de Formation par la Recherche), qui consiste en une collaboration entre un laboratoire et une entreprise. Elle s’est déroulée au sein de l'entreprise STMicroelectronics à Crolles en collaboration avec le Laboratoire de Statistique et Probabilité (LSP) de Toulouse.

En 1992, l’entreprise STMicroelectronics a construit un site de fabrication de puces à Crolles, baptisé Crolles1. Ces puces sont fabriquées sur des tranches de silicium de 200mm. Le 12 avril 2002, NXP (ex Philips Semiconductor) et Freescale (ex Motorola Semiconductor) ont rejoint STMicroelectronics sur le site de Crolles, pour mettre au point des technologies de fabrication de puces de 90 à 45 nanomètres sur des tranches de silicium de 300mm. Ce nouveau centre de R&D, qui a nécessité un investissement de plusieurs milliards de dollards, a été baptisé Crolles2 Alliance et se situe à coté de Crolles1.

Ma thèse s'est déroulée au sein de l’Alliance Crolles2 dans le département Contrôle des Procédés (Process Control).

Enjeux et objectifs

L'Alliance Crolles2 a pour objectif la fabrication de puces pour des technologies avancées tels que le C065 ou C045 sur des plaques de 300mm.

Pour de telles technologies, le contrôle de la fabrication des puces doit être irréprochable. La fabrication des puces dure environ 2 mois et est constituée de plusieurs dizaines d'étapes. Chacune de ces étapes doit être contrôlée avec précision pour obtenir des puces dans des spécifications de plus en plus serrées et éviter les rebuts. En effet, le coût d’une plaque 300 mm finalisée est beaucoup plus important que celui d’une plaque 200 mm, du fait du plus grand nombre de puces.

Jusqu'à présent, le contrôle des procédés consistait à effectuer des mesures sur les wafers pour les étapes critiques et à arrêter les équipements en cas de dérive. Malheureusement, ce type de contrôle simple de chacune des étapes de procédé ne suffit pas forcément pour avoir des puces dans les spécifications.

En effet, les différentes sources de variabilité, qui étaient auparavant négligeables, deviennent critiques pour les nouvelles technologies aux spécifications plus resserrées. Le procédé doit s'adapter à ces sources de variabilités incontrôlables. Pour cela, on utilise des boucles de régulation. Cela consiste à ajuster la recette ( consigne telle qu'une température ou une pression) d'un équipement de procédé en fonction des perturbations extérieures. L’ajustement est paramétré en fonction des erreurs commises sur les wafers passés précédemment sur l’équipement ou en fonction de mesures effectuées au préalable. Les boucles de régulation, nécessaires à la fabrication des technologies avancées, sont ainsi appelées à se généraliser. C’est

Cette thèse propose ainsi la création et la mise en pratique d'une méthodologie pour la mise en place de boucles de régulation en microélectronique. Cette méthodologie reste générale et peut se transposer aisément à d'autres domaines industriels.

La thèse CIFRE se situe dans un contexte industriel. Un objectif important est ainsi l'obtention de résultats opérationnels. Un autre enjeu de la thèse est l'utilisation d'outils théoriques dans un contexte industriel. Il a fallu obtenir des résultats facilement applicables, tout en proposant des résultats théoriques intéressants. C'est le défi et l'intérêt d'une thèse CIFRE.

Plan de la thèse

Le premier chapitre aborde la problématique de la thèse et le contexte industriel. Après une présentation de la microélectronique, un état de l'art du contrôle des procédés dans cette industrie est effectué. Les boucles de régulation sont ensuite présentées et les différents algorithmes existants sont détaillés. Enfin, la problématique de la thèse est introduite.

Le second chapitre de la thèse traite de la mesure en microélectronique. En effet, le contrôle de procédés et les boucles de régulation ont pour base la mesure. Il est primordial de vérifier la qualité des mesures utilisées dans une boucle, sous peine de dégrader le procédé. Une liste des différentes mesures effectuées en microélectronique pendant la fabrication des puces est dressée. Les indicateurs de qualité de ces mesures sont ensuite abordés. On s’intéresse particulièrement à l'indice de capabilité de mesure (Cpm), qui estime la variabilité d'un équipement de mesure. Un poster a été présenté sur un calcul de capabilité pour plusieurs équipements de mesure « A Global Indicator for metrology tool set measurement error estimation » à la conférence AEC/APC (Advanced Equipment Control/Advanced Process Control) d'Aix-en-Provence en mars 2006. De plus, un article s’intitulant « Gage R&R study for several Measurement Systems with non-independent Measured Objects » a été soumis en septembre 2007 au Journal of Quality Technology. Cet article est proposé en annexe de la thèse. Un aspect plus pratique de la capabilité a été abordé avec la création d’une interface graphique implémentée en R [R DEVELOPMENT CORE TEAM 2007].

Le troisième chapitre aborde la mise en place de la méthodologie et son application à l'atelier de polissage en microélectronique. Ce chapitre a fait l'objet de 2 présentations orales :

• « Mise en place d’une boucle de régulation pour le polissage de la couche de PMD » aux Journées Nationales du Réseau des Doctorants en Microélectronique (JNRDM) en mai 2007

• « Mise en place d’une boucle de régulation dans un atelier de polissage en microélectronique » aux Journées de Statistique à Angers en juin 2007 :

Ce chapitre a également fait l'objet d'un poster à la conférence AEC/APC d'Indian Wells en septembre 2007 « Run-to-run control of CMP Copper Process », présenté en annexe.

Les premières étapes de la méthodologie sont descriptives. On aborde dans un premier temps les motivations pour la mise en place d'une boucle. Puis, une description du procédé à réguler est effectuée. On propose enfin une série d'études statistiques à effectuer sur les paramètres impliqués dans la boucle de régulation :

• Analyses temporelles • Analyses spatiales • Analyses de variance

• Analyse de capabilité de procédé • Analyse de capabilité de mesure • Plan de contrôle

Ces études permettent de faire un premier bilan sur la boucle de régulation à mettre en place, son gain potentiel et sa faisabilité. Un tableau générique (Tableau 18), situé en fin de chapitre, résume les conclusions importantes effectuées à la suite de ces études.

L'étape suivante de la méthodologie est la modélisation du procédé de fabrication, nécessaire à la mise en place d’une boucle. Les différentes étapes pour effectuer cette modélisation sont définies et appliquées au procédé de polissage pour obtenir une modélisation originale à l'aide d'un modèle linéaire mixte.

La dernière étape de la méthodologie est l'optimisation de la boucle de régulation. En effet, il existe beaucoup d'algorithmes de régulation différents. Tous ces algorithmes ne peuvent pas être testé en production pour des raisons de temps et de coûts. On choisit donc de prédire leur comportement en production. Pour cela, la sortie du procédé de fabrication doit être estimée pour des consignes particulières. On se sert ainsi des données de production, qui nous indique la sortie pour une consigne particulière, pour simuler la sortie pour d’autres consignes. Cette simulation nous permet d'optimiser et de comparer tous les algorithmes. On calcule ainsi un gain de la boucle de régulation par rapport aux données de production. Des diagnostics possibles pour une boucle de régulation en production sont succinctement abordés.

Chapitre 1 : Problématique et contexte industriel

Le chapitre 1 présente tout d’abord la microélectronique, qui est un environnement vaste et complexe. Ensuite, un état de l’art du contrôle des procédés en microélectronique est effectué : le fonctionnement du SPC (Statistical Process Control) et de la FDC (Fault Detection and Classification) est ainsi détaillé. Les boucles de régulation sont ensuite abordées dans le détail. Pour finir, la problématique de la thèse est introduite.

1 Présentation de la microélectronique

1.1 Introduction

Cette partie propose une présentation générale de la microélectronique. Elle donne une définition des circuits intégrés et détaille les différentes étapes de leur fabrication. Les entreprises majeures de la microélectronique, ainsi que les nouveaux enjeux de cette discipline sont également abordés.

1.2 Présentation générale

La microélectronique est une spécialité du domaine de l'électronique. Tel que son nom l’indique, la microélectronique s'intéresse à l'étude et à la fabrication de composants électroniques à l'échelle du micromètre (= 10-6 mètre). Ces composants électroniques sont majoritairement des transistors, ainsi que des résistances, des capacités, des inductances, qui, mis ensemble, forment des circuits intégrés.

1.3 Définition d’un transistor

Le transistor (contraction de transfer resistor, en français résistance de transfert) est un composant électronique semi-conducteur, possédant 3 électrodes, capable de modifier le courant qui le traverse à l’aide d’une de ses électrodes (appelée électrode de commande). En microélectronique, le composant électronique élémentaire est le transistor MOS (Métal-Oxyde-Semiconducteur ouMetal Oxide Semiconductor).

Le transistor MOS est le type de transistor majoritairement utilisé pour la conception de circuits intégrés. Il existe deux types de transistors MOS : le transistor NMOS (Negative Metal Oxide Semiconductor) et le transistor PMOS (Positive Metal

Oxide Semiconductor). Le transistor NMOS est composé de deux zones chargées négativement, appelées respectivement source (possédant un potentiel quasi-nul) et drain (possédant un potentiel non nul), séparées par une région chargée positivement, appelée substrat (en anglais substrate). Le substrat est surmonté d'une électrode de commande, appelée grille (en anglais gate), permettant d'appliquer une tension sur le substrat. La Figure 1 représente le schéma d’un transistor NMOS.

La combinaison de transistors NMOS et PMOS sur un même circuit, appelé CMOS (Complementary Metal on Oxide), offre une faible consommation énergétique pour des applications associant rapidité et densité d'intégration. Ainsi les CMOS sont utilisés pour la fabrication des mémoires.

Figure 1: Schéma d’un transistorNMOS

Lorsqu’ aucune tension n'est appliquée à l'électrode de commande, le substrat, chargé positivement, agit telle une barrière et empêche les électrons d'aller de la source vers le drain. En revanche, lorsqu'une tension est appliquée à la porte, les charges positives du substrat sont repoussées et il s'établit un canal de communication, chargé négativement, reliant la source au drain. La Figure 2 illustre le fonctionnement d’un transistor NMOS mis sous tension.

Figure 2: Fonctionnement d’un transistor NMOS mis sous tension

Le transistor PMOS agit de façon similaire, les charges positives étant remplacées par des charges négatives et inversement. Le transistor agit donc globalement comme un interrupteur programmable grâce à l'électrode de commande. Lorsqu'une tension est appliquée à l'électrode de commande, il agit comme un interrupteur fermé, dans le cas contraire comme un interrupteur ouvert.

1.4 Définition d’un circuit intégré

Assemblés, les transistors peuvent constituer des circuits logiques, qui, assemblés à leur tour, constituent des circuit intégrés. Le premier circuit intégré date de 1958 et a été mis au point par la société Texas Instruments.

Les transistors MOS sont ainsi réalisés sur des plaques de silicium vierge (appelées wafers), obtenues après une succession de différents traitements. Ces

placés dans des boîtiers comportant des connecteurs d'entrée-sortie, le tout constituant un « circuit intégré ».

Dans la mesure où le boîtier rectangulaire possède des broches d'entrée-sortie ressemblant à des pattes, le terme de « puce électronique » est couramment employé pour désigner les circuits intégrés. La Figure 3 représente un circuit intégré.

Figure 3: Circuit intégré

Il peut exister jusqu'à plusieurs millions de transistors sur une seule puce. Ce nombre est d’autant plus élevé que la largeur de la grille d’un transistor est faible. Pour être plus précis, il s’agit de la largeur de la connexion électrique faite sur la grille. Ainsi, la technologie d’une puce est représentée par la largeur de grille de ses transistors, cette largeur étant la plus petite dimension caractéristique de la puce. Les transistors actuellement fabriqués ont des largeurs de grilles de 120nm, 110nm, 90nm et 65nm. Les technologies en développement sont le 45nm et le 32nm. La technologie nommée C090 correspond à des puces composées de transistors d’une largeur de grille de 90nm. De même, les autres technologies se nomment C120, C110, C065, C045 et C032.

La loi de Moore, édictée en 1965 par Gordon E. Moore, cofondateur de la société Intel, prévoyait que les performances des puces (par extension le nombre de transistors intégrés sur silicium) doubleraient tous les 12 mois. Cette loi a été révisée en 1975, portant le nombre de mois à 18. La loi de Moore s'applique toujours aujourd'hui.

Chaque année, la SIA (Semiconductor Industry Association) publie l’ITRS (International Technology Roadmap for Semiconductors) qui rassemble l’ensemble des spécifications prévues pour les technologies futures. La Figure 4 montre l’évolution des technologies prévue pour les années futures.

Figure 4: Evolution du nombre de transistors par puce dans le temps

1.5 Fabrication des circuits intégrés

Les circuits intégrés sont fabriqués sur des plaques de silicium vierge, appelées wafers. Le procédé de fabrication consiste en l’enchaînement de centaines d’étapes élémentaires. La durée du procédé, appelée temps de cycle, est d’environ 2 mois jusqu’à la mise en boîtier. Il peut être divisé en 2 parties :

• Les étapes dites de front-end (FE), qui rassemblent les étapes de fabrication du transistor proprement dit.

• Les étapes dites de back-end (BE), qui concernent les étapes d’interconnexion des transistors.

1.5.1 Etapes de fabrication

Les étapes de fabrication peuvent être subdivisées en 7 grands groupes, appelés ateliers : nettoyage, traitement thermique, dépôt, photolithographie, gravure, polissage, implantation ionique.

Nettoyage

Le nettoyage de la surface des wafers est effectué en utilisant des bains acides (étape dite humide) ou des plasmas d’oxygène (étape dite sèche).

Traitement thermique

Cette étape consiste à chauffer les wafers dans des fours thermiques. Ceci permet d’oxyder le silicium, d’effectuer des recuits après dépôt ou d’homogénéiser des concentrations de dopants.

Cette étape consiste à déposer une couche de matériau sur le wafer. Ce matériau peut être un métal (Al, Cu, W), un isolant (SiO2) ou un semi-conducteur.

Photolithographie

Cette étape consiste à déposer une résine photosensible sur un wafer, puis à l’insoler au travers d’un masque afin de reproduire un motif dans un matériau. Ce motif est transféré ensuite dans le matériau grâce à la gravure.

Gravure

Cette étape intervient après la photolithographie, elle consiste à enlever une couche de matériau dans les zones non protégées par le masque de résine à l’aide de 2 méthodes : la gravure humide et la gravure sèche.

• Gravure humide : trempage dans un bain

• Gravure sèche : attaque plasma, qui est une combinaison d’une attaque chimique et d’une pulvérisation physique. Ce principe permet d’augmenter énormément la vitesse de gravure.

Polissage

Cette étape consiste à planariser des dépôts de matériau. Pour cela, les wafers sont polis entre une tête de polissage et un pad qui tourne en sens contraire. De plus, un composé chimique (slurry) est introduit pour faciliter le polissage. Cet atelier s’appelle ainsi le CMP (Chemical Mechanical Polishing) car le procédé comporte aussi bien un aspect mécanique que chimique.

Implantation ionique

Cette étape permet de doper le silicium et ainsi d’ajuster les caractéristiques électriques des transistors. Des caissons dopés positivement sont réalisés en implantant du bore ou de l’indium, et des caissons dopés négativement en implantant du phosphore ou de l’arsenic.

1.5.2 Empilement

La fabrication des puces consiste ainsi à enchaîner ces différentes étapes dans un ordre précis : dépôt de matériau, gravure, polissage, implantation… On obtient ainsi un empilement qui forme des transistors reliés par des connexions de métal. Plusieurs couches de métal sont empilées pour permettre des interconnexions plus ou moins complexes des transistors. Actuellement, il peut y avoir jusqu’à 7 lignes de métal. La Figure 5 montre l’empilement d’un circuit intégré jusqu’aux couches de métal.

Figure 5: Empilement d’un circuit intégré

La Figure 6 montre la coupe d’un wafer en fin de procédé de fabrication vu par un

MEB (microscope à balayage électronique). On voit ainsi les transistors et les lignes de métal connectant les transistors entre eux.

Figure 6 : Vu de coupe d’un wafer au MEB

1.5.3 Fin du procédé de fabrication

A la fin du procédé de fabrication, un wafer, constitué en moyenne d’un millier de puces, est obtenu. Les Figure 7, Figure 8 et Figure 9 montrent un wafer de 300mm en fin de procédé de fabrication, le détail de puces sur un wafer et finalement des puces mises en boîtier après découpage.

N-well P-well P-well

GO2 Métal N-well GO2 N-iso Transistors P-substrate Contact Transistor Lignes de métal Contact

Figure 7 : Wafer en fin de

procédé de fabrication Figure 8 : Détail de puces en fin de procédé de fabrication Figure 9 : Puce mise en boîtier

1.5.4 Salle blanche

Tout le procédé de fabrication s’effectue dans un environnement propre, c’est-à-dire avec le moins de particules possibles, appelé salle blanche (en anglais, clean room). En effet, durant la fabrication, si une particule se dépose sur le wafer, cela peut causer des dommages irrémédiables au bon fonctionnement des puces.

N’importe quel objet ou personne génère des particules, les particules sont donc présentes en permanence dans l’air. Ainsi en salle blanche, tout va être fait pour minimiser la présence des particules :

• Les équipements de procédés sont fabriqués avec des matériaux peu contaminants.

• Les opérateurs en salle sont équipés d’une combinaison.

• Un flux laminaire d’air parcours la salle blanche du haut vers le bas pour évacuer les particules vers le bas et les empêcher de rentrer lors de l’ouverture des portes.

• Les wafers sont regroupés dans boîtes appelées FOUP (Front Opening Unified

Pod). Ceci crée un mini-environnement qui protège les wafers des particules extérieures.

La classe d’un environnement est définie par le nombre de particule par pied (environ 30 litres). La classe 1 ( = doigt blanc) correspond à moins de 1 particule par pied cube, la classe 10 ( = doigt gris) à moins de 10 particules et la classe 100 à moins de 100 particules. La Figure 10 représente un schéma de la salle blanche avec les différentes classes présentes. A Crolles 2, la salle blanche est de classe 10, tandis que les équipements sont en classe 1.

Figure 10: Schéma de la salle blanche

1.6 Industrie du semi-conducteur

1.6.1 Application des circuits intégrés

Les circuits intégrés numériques les plus simples sont des portes logiques (et, ou, non), les plus complexes sont les microprocesseurs et les plus denses sont les mémoires. On trouve de nombreux circuits intégrés dédiés à des applications spécifiques (ASIC pour Application Specific Integrated Circuit), notamment pour le traitement du signal (traitement d'image, compression vidéo...), on parle alors de DSP (pour Digital Signal Processor). Une famille importante de circuits intégrés est celle des composants de logique programmable. Ces composants sont amenés à remplacer les portes logiques simples en raison de leur grande densité d'intégration.

1.6.2 Entreprises du semi-conducteur

Les 11 entreprises du semi-conducteur ayant effectuées le chiffre d’affaire le plus important au cours de l’année 2006 sont les suivantes : Intel, Samsung, Texas Instruments, Toshiba, STMicroelectronics, Renesas, Hynix, AMD, Freescale, NXP et Nec Electronics. La Figure 11 montre les chiffres d’affaires de ces différentes entreprises pour l’année 2006.

Figure 11: Chiffre d’affaire en millions de dollars des 11 entreprises les plus

1.7 Nouveaux enjeux de la microélectronique

Le challenge actuel de la microélectronique est la réduction de la taille des circuits qui permet d’accroître la densité d’intégration des transistors et d’augmenter la vitesse des circuits. La précision nécessaire pour les différents procédés de fabrication est donc de plus en plus importante. Le contrôle du procédé de fabrication des puces devient donc crucial pour les nouvelles technologies. La partie suivante introduit ainsi les contrôles présents tout au long de la fabrication des circuits intégrés.

2 Le contrôle des procédés en microélectronique : état de

l’art au début de la thèse

2.1 Introduction

Le procédé de fabrication des puces compte plus d’une centaine d’étapes pour environ 2 mois de temps de cycle. La fabrication de circuits extrêmement petits requiert également une très grande précision sur chacune des opérations. Il est donc indispensable d’effectuer des contrôles réguliers des étapes critiques.

Pour cela, on réalise différents types de mesures, qui, résumés en indicateurs, permettent de s’assurer en temps réel, de la stabilité du procédé et des équipements :

• Les mesures effectuées sur les wafers après une étape du procédé de fabrication, appelé contrôle statistique des procédés (Statistical Process Control = SPC).

• Les mesures effectuées sur les paramètres hardware de l’équipement de procédé lui-même, appelé Fault Detection and Classification (FDC).

Les wafers sont généralement traités par lot de 25 dans les équipements de procédé. Pour cela, les wafers sont regroupés dans des boîtes appelées FOUP (Front

Opening Unified Pod). Pour des procédés relativement longs (traitement thermique ou nettoyage), plusieurs lots peuvent être traités en même temps. Après certaines étapes de procédés, considérées comme critiques, les lots sont chargés sur des équipements de métrologie, où certains wafers sont mesurés. La Figure 12 schématise une étape de procédé suivi d’une étape de métrologie.

Figure 12: Une étape de mesure suivant une étape de procédé

Les paragraphes suivants proposent une description détaillée du fonctionnement du

SPC et de la FDC.

2.2 Contrôle statistique des procédés (SPC)

2.2.1 Introduction

Cette étape clé consiste à contrôler, grâce à des outils statistiques, la stabilité et les performances des procédés. Ainsi pour certaines étapes de fabrication jugées critiques (dépôt de matériau, gravure…), un échantillon de wafers par lot est mesuré automatiquement juste après l’étape de fabrication pour vérifier la conformité des

sont appelées mesures en ligne. A partir de l’échantillon de mesures, des indicateurs sont calculés. Ces indicateurs sont suivis dans le temps pour contrôler une éventuelle dérive de l’équipement. Ainsi, lorsque les indicateurs sortent de certaines limites, appelées limites de contrôle, l’équipement est arrêté. La Figure 13 résume le fonctionnement du SPC.

Le SPC est un outil indispensable pour réaliser un pilotage rationnel du procédé de fabrication [MONTGOMERY 1996], [PILLET 2005]. De nos jours, il est la base de surveillance de la ligne de production [KOHLI 2002].

Les paragraphes suivants abordent plus précisément l’échantillonnage des mesures, le calcul des indicateurs et le suivi de ces indicateurs au travers des cartes de contrôle.

Figure 13 : Résumé du fonctionnement du SPC

2.2.2 Echantillonnage de la mesure

Les wafers sont constitués de plusieurs centaines de puces et ils sont regroupés par lot de 25. Pour des questions de coût, toutes les puces d’un lot ne peuvent pas être mesurées. En effet, ceci induirait un parc d’équipements de métrologie très important et le coût de la mesure deviendrait trop élevé. De plus, la mesure de toutes les puces de tous les wafers conduirait à un temps de cycle bien trop important au vu du gain potentiel sur le rendement.

Un échantillonnage est donc effectué basée sur 3 notions : le lot, le wafer et le site. Tous les lots sont mesurés, mais seuls certains wafers dans le lot sont mesurés. Les wafers mesurés ne le sont qu’en quelques points appelés sites de mesure. L’échantillonnage dépend de la criticité de l’étape du procédé et du type de métrologie (stand-alone ou intégrée). La métrologie est dite stand-alone (SA) lorsque l’équipement de métrologie est distinct de l’équipement de procédé, contrairement à la métrologie intégrée (Integrated Metrology Module = IMM) où l’équipement de métrologie est situé à l’intérieur de l’équipement de procédé.

Ainsi, dans le cas de la métrologie stand-alone, 1 à 4 wafers sont mesurés dans le lot. Pour la métrologie intégrée, les 25 wafers sont le plus souvent tous mesurés. Les mesures d’un wafer sont effectuées en 17 points et parfois en 9 points, sous-ensemble des 17 points. Ils sont répartis selon une certaine configuration appelée mapping de

mesure. Les points peuvent être répartis de façons légèrement différentes en fonction du produit, les puces ayant des tailles différentes. La Figure 14 montre les 3 niveaux d’échantillonnage en microélectronique : le niveau lot, le niveau wafer et le niveau

site. Le Tableau 1 résume l’échantillonnage des mesures effectuées en microélectronique.

La mesure s’effectue sur des wafers de production mais également sur des wafers témoins, appelés également Non Production Wafer (NPW). Ces wafers témoins ont seulement subi l’étape de procédé que l’on veut contrôler.

Figure 14: Lot, wafer, sites de mesure

Tableau 1 : Echantillonnage des mesures

Echantillonnage Lot Tous les lots

Wafer Métrologie stand-alone : 1 à 4 wafers

IMM : 25 wafers Site 17 sites

2.2.3 Calcul des indicateurs

Pour un lot i, J wafers sont mesurés en K sites. xijk correspond à la mesure du

paramètre considéré pour le wafer j et le site k du lot i. A partir de cet échantillon de mesures, différents indicateurs sont calculés pour chaque lot i.

• La moyenne de tous les wafers du lot i : ijk k j i i x JK x , 1 Σ = = µ .

• L’écart maximum entre la moyenne de chaque wafer :

(

)

Σ − Σ = > = k ijk k ijk j j J j i x x K r ' '1.. 1 max .• L’écart-type maximum par wafer :

(

)

− − Σ = 1 max 2 max K x xijk i k j i σ .(

1)

et 0 1 1 1 = + + − < < + λµi λ i λ i EWMA EWMAavec EWMA = Exponentially Weighted Moving Average.

L’EWMA consiste à faire une moyenne des µi en donnant un poids

exponentiellement décroissant à chaque µi.

(

)

(

)

0 1 0 1 1 EWMA EWMA n n i i n i n =λ∑

−λ µ + −λ − = − .La Figure 15 montre les pondérations des µi en fonction des valeurs de λ.

Figure 15 : Décroissance des poids exponentiels pour différentes valeurs de λ

Ainsi plus λ est important, plus le passé proche a un poids important par rapport au passé lointain. L’EWMA permet ainsi de lisser les données des mesures moyennes par lot. Plus λ est faible, plus le lissage est important. La Figure 16 illustre ce lissage des données.

Figure 16: Lissage des mesures par lot avec l’EWMA

2.2.4 Cartes de contrôle

La carte de contrôle et le calcul des limites associé sont l’œuvre de Walter Andrew Shewhart. Pour la première fois, en 1931, des cartes de contrôle sont mises en place au Bell Telephone Laboratory de la Western Electric. Ces cartes sont basées sur le travail du statisticien anglais Sir Ronald Aylmer Fisher dans son ouvrage “Statistical Methods for Research Workers” datant de 1925.

Limites de spécification

Pour chaque paramètre mesuré, il existe des limites de spécification, à ne pas franchir, sous peine d’obtenir un dysfonctionnement du circuit. Ces limites sont appliquées à chaque valeur individuelle mesurée (9 ou 17 sites par wafer). Elles sont définis au moment du design du produit et garantissent le bon fonctionnement des circuits. Ainsi, on s’assure qu’aucune valeur xijk ne sorte des limites de spécification.

Lorsqu’un lot a des mesures hors-spécifications, il est immédiatement arrêté pour effectuer des analyses complémentaires. Les limites de spécification haute et basse sont notées USL pour Upper Specification Limit et LSL pour Lower Specification Limit.

Limites de contrôle

Pour chacun des indicateurs statistiques vus dans la section 2.2.3, des limites de contrôle hautes et basses sont calculées. Ces limites sont calculées sur une période de production stable, fixées par les ingénieurs et validées par le groupe SPC. Les indicateurs devront toujours se trouver à l’intérieur de ces limites, ce qui validera que le procédé est stable. Les limites de contrôle hautes et basses sont notées respectivement UCL pour Upper Control Limit et LCL pour Lower Control Limit.

Calcul des limites de contrôle

Nous allons détailler le calcul des limites de contrôle pour la moyenne des mesures par lot. Nous disposons de la mesure de J wafers en K sites pour I lots. xijk

correspond à la mesure du paramètre considéré pour le wafer j et le site k du lot i. Méthode de Shewhart

Le calcul des limites de contrôle, préconisé par Shewhart, suppose que les mesures des « échantillons » sont indépendantes, un « échantillon » correspondant ici à un lot [MONTGOMERY 1996].

Les limites de contrôle hautes et basses sont égales à :

R A x LCL R A x UCL 2 2 − = + = avec =

∑

k j i ijk x IJK x , , 1moyenne de tous les échantillons

et

( )

( )

− Σ = = jk ijk jk ijk i I x x I R , , 1 max min 1étendue moyenne par échantillon.

A2 est calculé en fonction de la taille des échantillons. Plus cette taille est importante,

plus A2 est faible, donc plus les limites de contrôle sont resserrées.

En microélectronique, les mesures d’un même échantillon ne sont pas indépendantes. Les mesures d’un même lot sont forcément corrélées. Les lots sont composés de wafers qui passent sur la machine de procédé de manière séquentielle. De plus, les wafers sont mesurées en des sites fixes sur le wafer. Toute cette structure empêche l’indépendance des mesures d’un lot. Les tailles des échantillons sont relativement importantes (17 ou 34 points de mesures pas lot), ainsi les limites de contrôle calculées à l’aide de cette approche classique, de type Shewhart, sont beaucoup trop serrées et donc inapplicables à la microélectronique.

Méthode appliquée à Crolles 2

La méthode dite de Shewhart étant inapplicable à la microélectronique, une méthode spécifique a été développée à Crolles2. Tout d’abord, avant d’effectuer le calcul des limites de contrôle, un filtre est appliqué sur les mesures xijk. Ce filtre

permet d’enlever les valeurs extrêmes du calcul. Ainsi, on considère seulement les mesures telles que :

(

USL LSL)

x USL(

USL LSL)

LSL−2× − ≤ ijk ≤ +2× − .

Des limites de contrôle hautes et basses initiales sont alors calculées :

σ

σ

3 3 0 0 − = + = x LCL x UCLavec ijk k j i x IJK x , , 1 Σ

= moyenne de toutes les mesures

et

(

)

− − Σ = 1 2 , , IJK x xijk k j iσ

estimation de l’écart-type de l’ensemble des mesures.Dans le cas où la distribution des mesures n’est pas normale, d’autres indicateurs sont utilisés.

Un filtre itératif est alors appliqué pour le calcul des limites de contrôle finales UCLf et LCLf. La valeur extrême de l’échantillon est filtrée et un nouveau calcul des

limites de contrôle est effectué. Ce procédé est itéré jusqu’à ce que 5% des mesures aient été filtrés ou que toutes les mesures non-filtrées soient à l’intérieur des limites de contrôle. La Figure 17 résume le fonctionnement du filtre itératif.

Figure 17: Fonctionnement du filtre itératif pour le calcul des limites de contrôle Les ingénieurs s’appuient sur les limites calculées par le filtre itératif et sur leur expérience pour mettre en place des limites de contrôle pour leur procédé.

Suivi des indicateurs

Les indicateurs, ainsi que leurs limites associées, sont représentés sur des cartes appelées cartes de contrôle. Il existe 2 types de cartes :

• Les cartes pour les wafers de production • Les cartes pour les wafers témoins

Calcul de UCL

et LCL Une mesure est

en dehors des limites de

contrôle Toutes les mesures sont dans les limites

Plus de 5% des mesures ont été

filtrées

Moins de 5% des mesures ont

été filtrées STOP Filtre de la mesure extrême STOP