HAL Id: tel-00002936

https://tel.archives-ouvertes.fr/tel-00002936

Submitted on 3 Jun 2003HAL is a multi-disciplinary open access archive for the deposit and dissemination of

sci-L’archive ouverte pluridisciplinaire HAL, est destinée au dépôt et à la diffusion de documents

structurel des microsystèmes

B. Charlot

To cite this version:

B. Charlot. Modélisation de fautes et conception en vue du test structurel des microsystèmes. Autre [cs.OH]. Institut National Polytechnique de Grenoble - INPG, 2001. Français. �tel-00002936�

N° attribué par la bibliothèque

|__|__|__|__|__|__|__|__|__|__|

T H E S E

pour obtenir le grade de DOCTEUR DE L’INPG

Spécialité : MICROELECTRONIQUE

préparée au laboratoire TIMA dans le cadre de l’Ecole Doctorale

ELECTRONIQUE, ELECTROTECHNIQUE, AUTOMATIQUE, TELECOMMUNICATIONS, SIGNAL

présentée et soutenue publiquement

par

Benoît CHARLOT

le 12 mars 2001Titre :

Modélisation de fautes et conception en vue du test structurel des microsystèmes

_______Directeur de thèse :

Docteur Bernard COURTOIS Professeur Alain CHOVET

_______ JURY

M. Pierre GENTIL , Président

M. Michel DE LABACHELERIE , Rapporteur

M. Christian DUFAZA , Rapporteur

M. Bernard COURTOIS , Directeur de thèse

M. Alain CHOVET , Co-encadrant

remerciements

Je tiens tout d'abord à remercier M. Bernard COURTOIS, le directeur du TIMA et du CMP pour m'avoir accueilli au sein du groupe microsystèmes, pour m'avoir donné la possibilité d'entreprendre de nombreux projets et pour toutes les responsabilités qu'il m'a offertes, notamment au CMP.

Je remercie particulièrement M. Salvador MIR pour toute l'aide qu'il m'a fournie durant ces trois années de thèse.

Je tiens aussi à remercier M. Alain CHOVET, mon co-encadrant, pour son aide tout au long de cette thèse et pour m'avoir fait profiter des équipements de mesure du LPCS. Ces remerciements vont également aux gens du LPCS, Laurence MICHELUTTI, Nathalie MATHIEU, Youla MORFOULI et Jumana BOUSSEY pour leur gentillesse et leurs précieux conseils.

Je remercie les membres de mon jury, Messieurs Michel De LABACHELLERIE et Christian DUFAZA pour avoir jugé mon travail, M. Pierre GENTIL pour avoir accepté de présider ma thèse et M. Tom WILLIAMS pour m'avoir fait l'honneur d'y assister.

Je tiens à remercier mes collègues, Messieurs Damien VEYCHARD et Fabien PARRAIN pour leur précieuse compagnie.

Je remercie messieurs Hubert DELORI et Alexandre CHAGOYA pour leur humour, leur gaieté, et leur sympathie si communicative.

Je remercie toute l'équipe du CMP et notamment M. Kholdoun TORKI et pour les longues discussions techniques que nous avons eues ensemble.

Je remercie toute l'équipe du CIME, aussi bien l'équipe conception et salle blanche que l'atelier de test.

Je remercie chaleureusement toute l'équipe du groupe microsystèmes : Sergio, Libor, Jérome, Slava, Zein, Renato, Filipe, Hicham, et également ceux qui n'ont pas la chance d'appartenir au groupe microsystèmes : Pascal, Fabiano, Wander, Zoltan, Philippe, Gilles, Laurent, Alain, Paul, Jean-Baptiste et tous les autres.

Je remercie toute l'équipe des secrétaires du TIMA et du CMP pour la bonne ambiance générale qu'elles ont su imposer au laboratoire.

Surtout, je remercie Gaëlle qui a été à mes cotés pendant toutes ces années et qui va bientôt faire de moi le plus heureux des pères.

Table des matières

1

Introduction __________________________________________________________ 11

1.1 Les microsystèmes ________________________________________________________11

1.2 Historique des microsystèmes _______________________________________________12

1.3 Marché et applications industrielles __________________________________________12

1.4 Le test des microsystèmes __________________________________________________12

1.5 Structure de la thèse _______________________________________________________14

2

Technologies et applications microsystèmes ________________________________ 17

2.1 Les technologies microsystèmes______________________________________________17 2.1.1 Le micro-usinage en volume ____________________________________________________ 17

2.1.2 Le micro-usinage en surface ____________________________________________________ 24

2.1.3 D'autres technologies _________________________________________________________ 29

2.2 Les applications des microsystèmes __________________________________________32 2.2.1 Les domaines d’applications ____________________________________________________ 33

2.2.2 Exemple d’application microsystèmes : les micro-résonateurs électrostatiques en peignes ____ 41

2.3 Conclusion _______________________________________________________________45

3

Fiabilité et défaillance des microsystèmes __________________________________ 49

3.1 La question de la fiabilité des microsystèmes___________________________________49 3.1.1 L’analyse de fiabilité__________________________________________________________ 49

3.2 Les mécanismes de défaillances et les défauts des microsystèmes __________________50 3.2.1 Travaux précédents ___________________________________________________________ 50

3.2.2 Mécanismes de défaillance et défauts des microsystèmes fabriqués à partir des technologies compatibles microélectronique__________________________________________________________ 51

3.2.3 Mécanismes de défaillance et défauts des microsystèmes fabriqués à partir des technologies spécifiques de micro usinage en surface. __________________________________________________ 61

3.3 Conclusion _______________________________________________________________69

4

Le test des circuits intégrés. _____________________________________________ 73

4.1 Introduction _____________________________________________________________73 4.1.1 La fonction du test____________________________________________________________ 73

4.1.2 Les différentes phases de validation et de test_______________________________________ 73

4.2 Le test des circuits numériques ______________________________________________74 4.2.1 Principe ____________________________________________________________________ 74

4.2.2 Test fonctionnel et test structurel ________________________________________________ 75

4.2.3 Tests structurels basés sur la simulation de fautes ___________________________________ 75

4.2.4 La conception en vue du test : Design For Test (DFT) ________________________________ 77

4.2.5 Le test Iddq _________________________________________________________________ 80

4.3 Le test des circuits intégrés analogiques et mixtes_______________________________81 4.3.1 Introduction : la problématique du test analogique ___________________________________ 81

4.3.2 Le test fonctionnel des circuits analogiques ________________________________________ 82

4.3.3 Les techniques de test structurel (test basé sur les fautes)______________________________ 82

4.3.4 Le test de circuits analogiques particuliers _________________________________________ 85

4.3.5 Le design for test analogique____________________________________________________ 86

4.4 Le test des Systèmes sur une puce (SoC) ______________________________________88

5.1 Méthodologie du test structurel basé sur la simulation de fautes __________________96 5.1.1 Problématique de la simulation de fautes des microsystèmes ___________________________ 97

5.1.2 Etat de l’art _________________________________________________________________ 98

5.1.3 Structure du chapitre __________________________________________________________ 98

5.2 La modélisation des microsystèmes __________________________________________98 5.2.1 La modélisation en éléments finis _______________________________________________ 100

5.2.2 La modélisation par équivalent électrique_________________________________________ 104

5.2.3 La modélisation comportementale par langage de description du matériel. _______________ 107

5.2.4 La modélisation nodale _______________________________________________________ 110

5.2.5 La réduction de modèles ______________________________________________________ 113

5.3 Les fautes _______________________________________________________________115

5.4 La modélisation et l’injection de fautes ______________________________________117 5.4.1 La modélisation et l’injection de fautes au niveau éléments finis _______________________ 118

5.4.2 La modélisation et l’injection de fautes au niveau circuit équivalent électrique ____________ 122

5.4.3 La modélisation et l’injection de fautes au niveau description comportementale ___________ 122

5.4.4 La modélisation et l’injection de fautes au niveau modélisation nodale __________________ 123

5.5 Vers la validation des stimuli de test par simulation de fautes____________________124

5.6 Conclusion ______________________________________________________________125

6

Conception en vue du test des microsystèmes______________________________ 129

6.1 Introduction ____________________________________________________________129

6.2 Conception BIST des microsystèmes basée sur l'auto stimulation ________________129 6.2.1 Principe ___________________________________________________________________ 129

6.2.2 Travaux précédents __________________________________________________________ 130

6.3 Génération de stimuli de test in situ et application aux microsystèmes. ____________131

6.4 Jauge de déplacement capacitive____________________________________________131 6.4.1 Les accéléromètres capacitifs __________________________________________________ 132

6.4.2 Mesure du déplacement et circuit d'interface ______________________________________ 133

6.4.3 Génération de stimuli de test in situ _____________________________________________ 135

6.5 Jauge de contrainte piézo-résistive __________________________________________136 6.5.1 Explication physique de la piézo-résistivité _______________________________________ 136

6.5.2 Jauges de contraintes piézo-résistives en technologie micro-usinage de volume compatible CMOS. 139

6.5.3 Stimulation thermo-mécanique d’une jauge de contrainte piézo-résistive ________________ 141

6.5.4 Application DFT : le capteurs d’empreintes à micropoutres___________________________ 145

6.6 Jauge de température à thermopile _________________________________________149 6.6.1 Les thermopiles et l’effet Seebeck ______________________________________________ 149

6.6.2 Détecteur Infra rouge à thermopiles avec fonction d'auto-test _________________________ 152

6.6.3 Le capteur infrarouge à thermopiles : thermatrix ___________________________________ 154

6.7 Conclusion ______________________________________________________________162

7

Conclusions générales et travaux futurs __________________________________ 167

Annexe 1 :

Dérivation des matrices structurelles pour l'analyse nodale___________________ 171

Annexe 2 :

Modèle HDL-A d'une poutre flexible à deux nœuds________________________ 174

Annexe 3 :

Détail d'un procédé de fabrication CMOS à deux niveaux de métal non planarisés.__ 176

Liste des figures

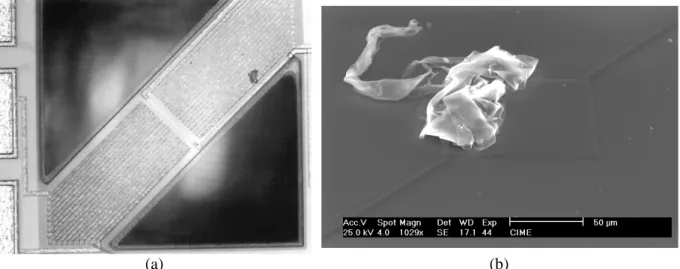

Figure 1 : "Microsystème biologique" illustrant la diversité des fonctions qui seront dans le futur intégrées

au niveau d'une puce. ________________________________________________________________ 11 Figure 2 : Schéma en coupe d’une technologie de micro usinage en volume face avant compatible CMOS. _____ 18 Figure 3 : Image MEB d’une microstructure obtenue par micro-usinage en volume face avant et montrant

la composition en sandwich des structures suspendues.______________________________________ 18 Figure 4 : Diagramme polaire des vitesses de gravure du TMAH. ______________________________________ 19 Figure 5 : Schéma représentant l’avancée de la gravure anisotropique à partir d’ouvertures triangulaires. _______ 19 Figure 6 : Photo MEB d’une microstructure en pont obtenu par micro usinage en volume par gravure

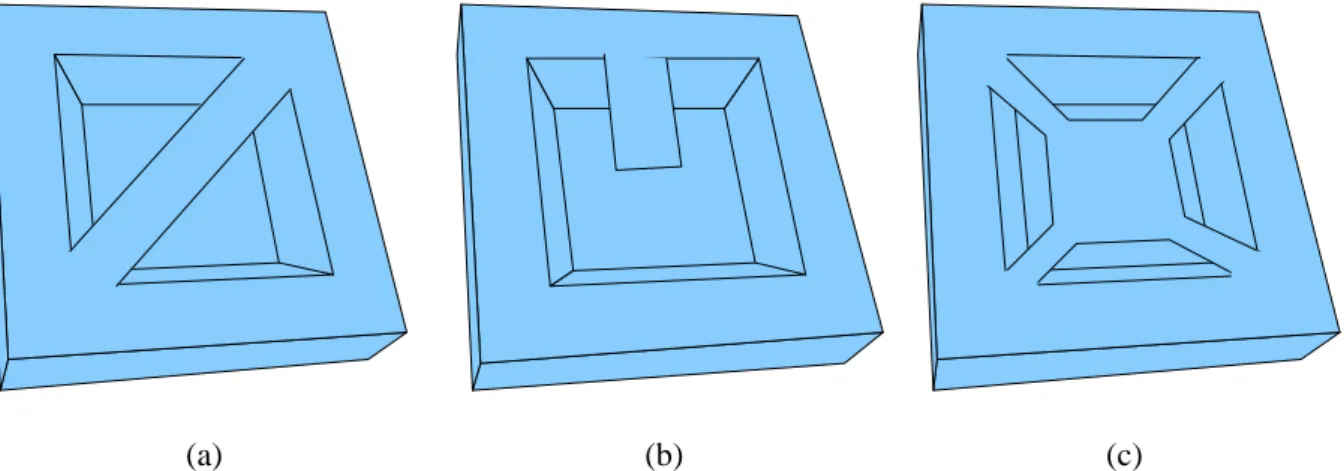

anisotropique du silicium du substrat. ___________________________________________________ 20 Figure 7 : Simulation géométrique (a) de la gravure anisotropique d’une membrane soutenue par quatre

bras à 45°, et photo MEB (b) de la même structure avec gravure TMAH incomplète. ______________ 21 Figure 8 : Simulation atomistique de la gravure anisotropique d’une membrane soutenue par quatre bras à

45°, pour différents pas de calculs montrant la progression de la gravure. _______________________ 21 Figure 9 : Schéma des différentes microstructures que l’on peut obtenir par micro usinage en volume face

avant. ____________________________________________________________________________ 22 Figure 10 : Schéma d’une structure à masse suspendue obtenue en micro usinage en volume face avant. _______ 22 Figure 11 : Schéma des différentes structures résultantes d’un micro-usinage en volume face arrière. __________ 23 Figure 12 : Schéma en coupe d’une structure à masse suspendue obtenue en micro usinage en face avant

et en face arrière. ___________________________________________________________________ 23 Figure 13 : Schéma en coupe de structures suspendues par micro usinage électrochimique en volume, face

arrière (a) et face avant (b). ___________________________________________________________ 24 Figure 14 : Schéma en coupe d’une technologie de micro usinage en surface avant (a) et après (b) gravure

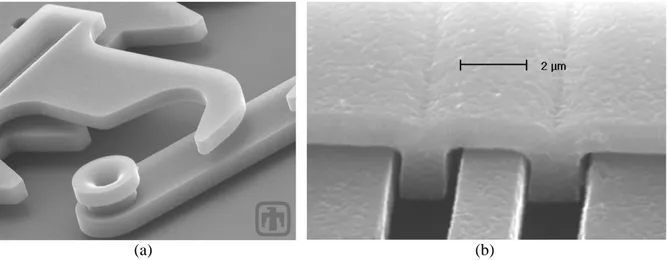

des oxydes sacrificiels._______________________________________________________________ 24 Figure 15 : Photos MEB d’éléments micromécaniques fabriqués par micro usinage de surface

(technologie MUMPS), charnière (a), dents d’engrenage (b), ressort pivotant (c). _________________ 25 Figure 16 : Photo MEB d’un micromoteur électrostatique fabriqué en technologie MUMPS. ________________ 25 Figure 17 : Photos MEB de structures micro-usinées en surface avec planarisation (a) (Courtesy, Sandia

National Labs - MEMS, S&T Department, www.mems.sandia.gov) et sans planarisation (b). _______ 26 Figure 18 : Photo MEB d’un dimple sous une couche de polysilicium suspendue (Courtesy, Sandia

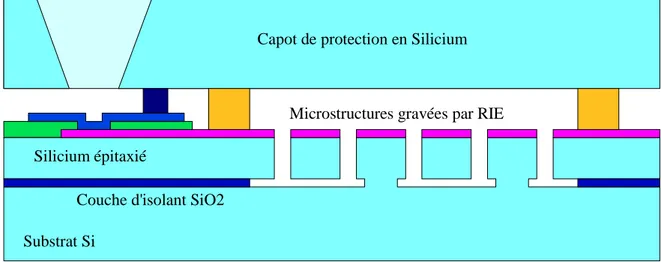

National Labs - MEMS, S&T Department, www.mems.sandia.gov). ___________________________ 27 Figure 19 : Schéma en coupe d’une technologie de micro usinage en surface intégrée.______________________ 28 Figure 20 : Schéma en coupe d’une technologie MEMS intégrée avec parties microsystèmes enterrées,

(Courtesy, Sandia National Labs - MEMS, S&T Department, www.mems.sandia.gov). ____________ 28 Figure 21 : Schéma en coupe d’une technologie microsystème intégrée avec parties déposées et gravées

après l’électronique et l’usage de niveaux métalliques en tungstène. ___________________________ 29 Figure 22 : Schéma en coupe de la technologie de micro-usinage sur SOI : Epi-SOI de Tronic's

microsystems (Courtesy of TRONIC'S Microsystems, France)________________________________ 30 Figure 23 : Procédé LIGA pour la fabrication de pièces métalliques ou de moules métalliques pour

injection de plastiques. _______________________________________________________________ 31 Figure 24 : Application automobile des microsystèmes.______________________________________________ 33 Figure 25 : Application des microsystèmes dans les satellites._________________________________________ 34 Figure 26 : Application des microsystèmes dans l’avionique. _________________________________________ 35 Figure 27 : Applications des microsystèmes dans le corps humain. _____________________________________ 36 Figure 28 : Schéma de principe d’une biopuce, (a) molécule d'ADN dénaturée et (b) puce à ADN

contenant des sondes à ADN.__________________________________________________________ 36 Figure 29 : Image MEB d'inductances suspendues obtenues par micro-usinage en volume sur AsGa (a) et

sur Silicium (b). ____________________________________________________________________ 37 Figure 30 : Schéma d'un banc optique intégré. _____________________________________________________ 39 Figure 31 : Image MEB d'un miroir vertical monté sur une roue actionnée par crémaillère (MUMPS). _________ 39 Figure 32 : Multiplexeur optique à micro miroirs ___________________________________________________ 40 Figure 33 : Vue schématique des micro-miroirs électrostatiques de Texas Instruments (a) en technologie

propriétaire, et de TIMA (b) en technologie MUMPS. ______________________________________ 40 Figure 34 : Schéma de principe du fonctionnement d’un micro-résonateur en peigne. ______________________ 41 Figure 35 : Connexions électriques d'un micro-résonateur en peigne. ___________________________________ 42 Figure 36 : Image MEB de micro-résonateurs en peigne, à déplacement longitudinal (a) et rotatif (b). _________ 42

Figure 37 : Image optique de micro-résonateurs sous pointes, (a) non excité et (b) excité à la résonance à 20 kHz, on remarque le halo laissé par la rémanence de la caméra qui permet de déterminer

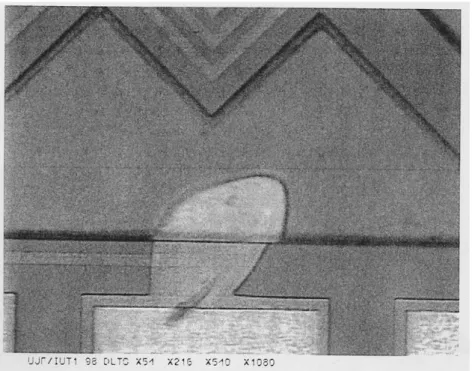

l’amplitude de déplacement d. _________________________________________________________ 45 Figure 38 : Apparition d'un void lors du dépôt d'un diélectrique. _______________________________________ 52 Figure 39 : Image au microscope optique d'un défaut de lithographie au niveau de la métallisation. ___________ 53 Figure 40 : Vue en coupe d’une particule métallique, réalisée par microscope à faisceau d’ions focalisés

[16]. _____________________________________________________________________________ 54 Figure 41 : Image MEB de microsystèmes ayant subi des fractures sur les bras de suspension.

Convertisseur électrothermique à 12 bras (a)(b) et à 4 bras (c)(d). _____________________________ 55 Figure 42 : Image MEB de poutres suspendues ayant subies de fractures (a) et image au microscope

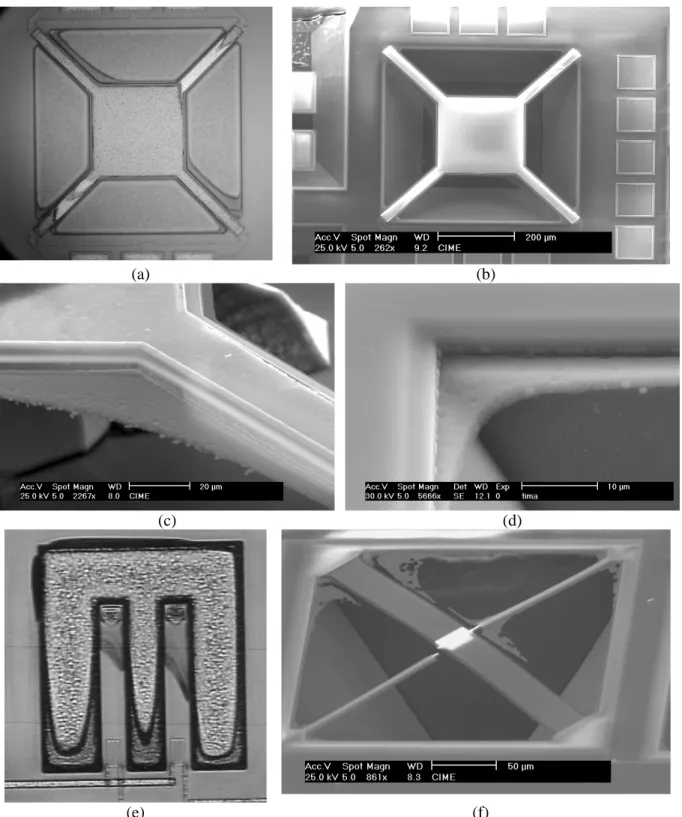

optique d'une thermopile en pont ayant également subie une fracture. __________________________ 56 Figure 43 : Images optiques (a) et MEB (b) de particules de poussière déposées sur des microstructures. _______ 56 Figure 44 : Image MEB de structures microsystèmes insuffisamment gravées. ____________________________ 57 Figure 45 : Images optiques (a,e) et MEB (b, c, d, f) de résidus d'oxydes dans les ouvertures vers le

silicium du substrat. _________________________________________________________________ 58 Figure 46 : Images prises avec un détecteur infrarouge refroidi d'un convertisseur électrothermique en

fonctionnement et superposition de l'intensité lumineuse produite par la résistance de chauffe._______ 59 Figure 47 : Apparition d'un composé chimique déposé en fond de cavité lors d'une gravure anisotropique

à l'EDP. __________________________________________________________________________ 60 Figure 48 : Apparition d'un composé chimique encapsulant dans une cavité gravée par TMAH. ______________ 60 Figure 49 : Image MEB montrant des défauts de lithographie dans des microstructures suspendues. ___________ 62 Figure 50 : Photos MEB de microstructures collées, (a), (b) et (c) micro-résonateurs en peigne et (d)

actuateur thermique à bilame. _________________________________________________________ 63 Figure 51 : Effet d’attraction entre microstructures dus aux tensions de surface de l’interface liquide gaz

lors du séchage après gravure humide.___________________________________________________ 63 Figure 52 : Images MEB montrant des fractures dans des microstructures suspendues, (a) et (b) doigts de

peignes interdigités, (c) fracture le long d’une structure et (d)(e)(f) fracture des ressorts de

suspension. ________________________________________________________________________ 65 Figure 53 : Effets thermiques dans des actionneurs à bilame. _________________________________________ 66 Figure 54 : Images MEB montrant des pollutions par des particules sur des micro-résonateurs

électrostatiques. ____________________________________________________________________ 67 Figure 55 : Image MEB d'un microphone électrostatique obtenu en micro-usinage de surface et des effets

des contraintes internes (a). Détail du non alignement (b) ____________________________________ 68 Figure 56 : Cycle de conception et de fabrication des circuits intégrés et la place du test dans ce cycle _________ 74 Figure 57 : Fautes affectant un circuit numérique. __________________________________________________ 76 Figure 58 : Schéma d’un circuit soumis à une injection de faute (collage à 1 sur le nœud d) pour la

génération automatique de vecteurs de test. _______________________________________________ 76 Figure 59 : Schéma représentant la conception de type scan path en vue du test. __________________________ 78 Figure 60 : Configuration d’un circuit selon la norme IEEE 1149.1 boundary scan. ________________________ 78 Figure 61: Schéma de principe d’une architecture BIST. _____________________________________________ 79 Figure 62 : Schéma d’un LFSR. ________________________________________________________________ 79 Figure 63 : Représentation d’une faute de collage à l’état passant d’un PMOS dans un inverseur, et effet

sur le courant Iddq.__________________________________________________________________ 80 Figure 64 : Principe du test Iddq, les circuits dont la valeur du courant Iddq dépasse une certaine limite

sont rejetés ________________________________________________________________________ 80 Figure 65 : Environnement de test analogique spectral typique.________________________________________ 82 Figure 66 : Exemple de fautes affectant un circuit analogique, fautes catastrophiques : courts circuits dans

un transistor MOS et fautes paramétriques : déviation des paramètres électriques d’un

transistor. _________________________________________________________________________ 83 Figure 67 : Schéma représentant l’insertion dans une suite de blocs analogiques de multiplexeurs

analogiques pour améliorer l’observabilité en vue du test. ___________________________________ 86 Figure 68 : Architecture standard de BIST analogique pour circuits mixtes. ______________________________ 87 Figure 69 : Structure interne d’un circuit mixte selon la norme IEEE 1149.4 en vue du test. _________________ 88 Figure 70 : Circuit intégrant différentes technologies intégrées de manière monolithique dit System On a

Figure 74 : Analyse structurelle de la déformation d'une poutre soumise à un encastrement à sa base et à

l'application d'une force verticale à son extrémité._________________________________________ 102 Figure 75 Image MEB d’un filtre micro-électromécanique. __________________________________________ 103 Figure 76 : Analyse en éléments finis des modes de résonance d’un filtre micro-électromécanique, les

quatre premiers modes sont représentés. ________________________________________________ 103 Figure 77 : Analyse électrothermique transitoire d’une poutre suspendue contenant une thermopile et une

résistance chauffante à l’extrémité. L’analyse montre l’évolution de la distribution de

température à la surface de la micropoutre. ______________________________________________ 104 Figure 78 : Schéma (a) et image MEB (b) d'un convertisseur électrothermique à poutre suspendue. __________ 106 Figure 79 : Modélisation en équivalent électrique d'un convertisseur électrothermique. ____________________ 107 Figure 80 : Exemples d'assignements explicite et implicite dans des modèles HDL. _______________________ 108 Figure 81 : Simulation d'un microsystème avec des modèles HDL. ____________________________________ 109 Figure 82 Représentation d'une poutre en flexion par un modèle à deux nœuds de 3 degrés de liberté. ________ 111 Figure 83 : Représentation en modélisation nodale de l'équipage mobile d'un micro-résonateur. _____________ 112 Figure 84 : modèle d'un élément de transmission de la chaleur à une dimension. _________________________ 113 Figure 85 modèle d'un élément de transmission de la chaleur à deux dimensions._________________________ 113 Figure 86 : Principe de la sous structuration. _____________________________________________________ 114 Figure 87 : Schéma de principe de la méthode de génération de modèles HDL à partir de simulations

FEM. ___________________________________________________________________________ 115 Figure 88 : Images MEB de convertisseurs électrothermiques, complètement suspendu (a) et

insuffisamment gravés (b,c). _________________________________________________________ 119 Figure 89 : Mesure de la réponse d'un convertisseur électrothermique à une impulsion de 1V, dans le cas

sans fautes (a) et dans le cas présentant un défaut de gravure (b). Les niveaux de sortie sont

respectivement de 38,4 mV et de 28 mV, les constantes de temps sont de 1.8 ms et de 0,88ms. _____ 119 Figure 90 : Simulation FEM d'un convertisseur électrothermique avec (b) et sans (a) la présence d'un

défaut de sous gravure anisotropique. __________________________________________________ 120 Figure 91 : Simulation FEM d'un transducteur électrostatique à peigne interdigité. La simulation

électrostatique représente le potentiel électrique dans l'air entre les électrodes, pour un doigt aligné (a) et ayant subi une de rotation de 4°(b).Représentation vectorielle du Champ électrique

(c) et (d)._________________________________________________________________________ 121 Figure 92 : Modélisation d'une faute au niveau équivalent électrique d'un court circuit thermique dans un

convertisseur électrothermique. Défaut de gravure anisotropique insuffisante.___________________ 122 Figure 93 : Simulation d'une faute paramétrique (masse du résonateur) dans une description

comportementale par HDL d'un micro-résonateur électrostatique. ____________________________ 123 Figure 94 : Exemple d'injection de fautes au niveau de la modélisation nodale, collage à la masse

thermique d'un convertisseur électrothermique pour modéliser un défaut de gravure

anisotropique._____________________________________________________________________ 123 Figure 95 : Exemple d'injection de fautes au niveau de la modélisation nodale, collage mécanique. __________ 124 Figure 96 : Schéma de principe de l’intégration de fonctions d'auto test dans un microsystème.______________ 130 Figure 97 : Schéma de principe d'un accéléromètre capacitif _________________________________________ 132 Figure 98 : Photos MEB d’un accéléromètre capacitif fabriqué en micro usinage de surface avec la

technologie MUMPS, vue d’ensemble (a) et détail de la masse mobile et des électrodes

interdigitées (b). ___________________________________________________________________ 133 Figure 99 : Représentation schématique des connexions d'un accéléromètre capacitif _____________________ 133 Figure 100 : Schéma d'une interface en boucle ouverte de mesure capacitive du déplacement._______________ 134 Figure 101 : Représentation schématique d'un circuit de mesure de déplacement capacitif à contre

réaction négative de force. ___________________________________________________________ 134 Figure 102 : Réponse de l'accéléromètre ADXL 105, à une pulsation carrée sur l'entrée "self test". ___________ 136 Figure 103 : Diagramme E(k) du silicium monocristallin. ___________________________________________ 137 Figure 104 : Définition des stress normaux et de cisaillement ________________________________________ 138 Figure 105 : Facteur de jauge du polysilicium en fonction de dopage du polysilicium (d'après French et

Evans [18][19][20]) ________________________________________________________________ 139 Figure 106 : Image optique d’une poutre avec résistance piézo (non libérée) et schéma en coupe de la

section de la poutre montrant l’empilement des couches (échelle non respectée). ________________ 140 Figure 107 : Différentes implémentations des jauges de contraintes à piézo-résistance_____________________ 140 Figure 108 : Image optique (a) et MEB (b) d’une micro-poutre à jauge de contrainte piézo-resistive

contenant une résistance de chauffe pour l’effet bimétallique. _______________________________ 141 Figure 109 : Vue d'écran des mesures à l'oscilloscope, signal carré d'entrée et réponse du pont de

Figure 111 : Mesure de la variation de la résistance de la jauge piézo, la déflexion de la micro-poutre

étant imposée par une pointe de test. ___________________________________________________ 144 Figure 112 : Variation de la résistance de la jauge piézo en fonction de la flèche de la micro-poutre,

obtenu par calcul analytique. _________________________________________________________ 144 Figure 113 : Simulation en FEM thermo-mécanique d'une micro-poutre à jauge piézo-résistive contenant

une résistance de chauffe, température et déformée pour la poutre entière (a) et pour les

conducteurs (b)____________________________________________________________________ 145 Figure 114 : Schéma de principe du capteur d’empreintes digitales à micro-poutres. ______________________ 146 Figure 115 : Layout du premier prototype de capteur d'empreintes digitales à micro-poutres implémenté

en technologie AMS 0.6µ m avec post process de gravure anisotropique. _______________________ 147 Figure 116 : Image MEB des micro-poutres piézo-résistives du capteur d’empreintes digitales. _____________ 147 Figure 117 : Image MEB de la fracture d'une micro-poutre. _________________________________________ 148 Figure 118 : Schéma de l’électronique d’adressage de chaque pixel ainsi que l’électronique de test. __________ 148 Figure 119 : Schéma de principe de l’effet Seebeck ________________________________________________ 149 Figure 120 : Effet du déplacement du niveau de Fermi et de la thermodiffusion sur la densité de porteurs

dans un métal. ____________________________________________________________________ 150 Figure 121 : Images MEB de capteurs infrarouges à thermopiles fabriqués par micro-usinage en volume

sur une technologie CMOS. En forme de ponts (a) et de membrane (b).________________________ 151 Figure 122 : Schéma d’un détecteur infrarouge à bolomètre. _________________________________________ 153 Figure 123 : Layout du capteur infrarouge à thermopile_____________________________________________ 154 Figure 124 : Détail d’un pixel (une seule thermopile a été représentée). ________________________________ 155 Figure 125 : Simulation de gravure anisotropique de la membrane du pixel. _____________________________ 155 Figure 126 : Simulation transitoire en éléments finis (ANSYS) du pixel sous un flux radiatif équivalent à

10µW, (a) répartition de la température à la surface en régime permanent et (b) variation

transitoire de la température en différents points. _________________________________________ 156 Figure 127 : Schéma du circuit analogique d’amplification __________________________________________ 157 Figure 128 : Schéma de l’électronique de chaque pixel comprenant le mode test avec la résistance de

chauffe (a) et simulation FEM thermique de la distribution de chaleur créée par la résistance de

chauffe (b) _______________________________________________________________________ 158 Figure 129 : Modèle comportemental du pixel (a), simulation du mode self test : températures du pixel (b)

et sortie de l’interface analogique (les pics d’échantillonnage ont étés retirés pour plus de

clarté) ___________________________________________________________________________ 159 Figure 130 : Image MEB de défauts de fabrication provenant d'un résidu d'oxyde dans les ouvertures vers

les silicium du substrat dans un capteur infrarouge à thermopiles. ____________________________ 160 Figure 131 : Modélisation nodale à partir du langage VERILOG-A d'un capteur infrarouge à thermopile à

membrane, capture d'écran de l'éditeur de vue schématique de CADENCE._____________________ 160 Figure 132 : Résultats de simulation de fautes en transitoire d'un capteur infrarouge à thermopiles en

mode auto-test. Les courbes correspondent à la température à différents nœuds de la membrane

et des bras de support, (a) modèle sans fautes, (b) modèle avec fautes de collage thermique. _______ 161 Figure 133 : Représentation d'une poutre en flexion par un modèle à deux nœuds de 3 degrés de liberté. ______ 171 Figure 134 : Fonctions de forme _______________________________________________________________ 172

Liste des tableaux

Tableau 1 : Estimation de la date d’apparition de l’intégration de différentes technologies en System On a

Chip sur les technologies CMOS standard (source International technology Roadmap for

Semiconductors, 1999 edition). ________________________________________________________ 13

Tableau 2 : Principaux mécanismes de défaillance des circuits intégrés et leurs modes de défaillance. _________ 51 Tableau 3 : Principaux mécanismes de défaillances et défauts des technologies microsystèmes de

micro-usinage en volume compatible CMOS. __________________________________________________ 61 Tableau 4 : Principaux mécanismes de défaillances et défauts des technologies microsystèmes de

micro-usinage en surface. __________________________________________________________________ 69 Tableau 5 : Différents types de fautes en analogique et composants affectés. _____________________________ 84 Tableau 6 : Récapitulatif des méthodes de test structurel pour les circuits intégrés numériques,

analogiques et microsystèmes. _________________________________________________________ 95 Tableau 7 : différents niveaux de modélisation d’un microsystème : exemple d’un micro-résonateur en

peigne. ___________________________________________________________________________ 99 Tableau 8 : Représentation des variables de potentiel et de flux pour différents domaines d'énergie. __________ 105 Tableau 9 : Equivalence électrique _____________________________________________________________ 106 Tableau 10 : Niveaux hiérarchiques de la simulation analogique ______________________________________ 107 Tableau 11 : Modèles HDL-A et VERILOG-A d'une structure en peigne interdigitée. _____________________ 110 Tableau 12 : Liste de fautes pour les composants microsystèmes fabriqués à partir des technologies de

micro-usinage en volume compatible CMOS. ____________________________________________ 116 Tableau 13 : Liste de fautes pour les composants microsystèmes fabriqués à partir des technologies de

micro-usinage en surface.____________________________________________________________ 117 Tableau 14 : Exemple de modèles de fautes affectant des microsystèmes représentés par des collages, par

analogie aux modèles de fautes des circuits analogiques et numériques.________________________ 118 Tableau 15 : Coefficient Seebeck des thermocouples réalisables en technologie AMS. ____________________ 151 Tableau 16 : Caractéristiques de l’imageur infrarouge à thermopiles. __________________________________ 156

1

Introduction

1.1

Les microsystèmes

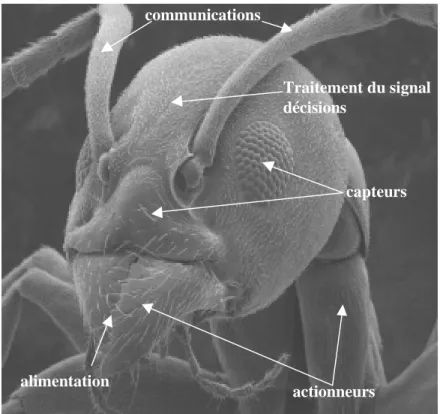

Les microsystèmes, au sens de la définition européenne du terme, sont des systèmes miniaturisés intelligents qui combinent de manière monolithique des capteurs et des actionneurs [1][2] à des fonctions de traitement du signal et de l'information. Le terme microsystème comprend également la notion de multidisciplinarité de par l'emploi de signaux mécaniques, électrostatiques, optiques, thermiques, etc. Cette définition des microsystèmes est beaucoup plus large que celle employée par les Américains : MEMS1 pour définir des systèmes électromécaniques à l'échelle du micron comprenant des capteurs et des actionneurs fabriqués avec les techniques de croissance, de dépôt de matériaux et de lithographie des circuits intégrés [3][4]. On recense également les appellations micromachines ou mechatronics spécialement au japon et l'acronyme MST en Europe.

Si aujourd'hui les microsystèmes sont en général seulement un capteur fabriqué par un procédé issu de la microélectronique intégré dans le meilleur des cas avec un amplificateur, leur réelle vocation est de devenir des systèmes complexes intégrant de manière monolithique des fonctions de capteurs et d'actionneurs mais également des ensembles de traitement du signal et de l'information, des fonctions de communication avec l'extérieur ou entre microsystèmes et même de télé-alimentation. La Figure 1 représente un microsystème biologique qui préfigure ce à quoi pourraient ressembler les microsystèmes du futur. capteurs actionneurs communications Traitement du signal décisions alimentation

Figure 1 : "Microsystème biologique" illustrant la diversité des fonctions qui seront dans le futur intégrées au niveau d'une puce.

1.2

Historique des microsystèmes

L'histoire des microsystèmes commence par une conférence donnée par le professeur Feynman [5] au CALTECH pour la réunion annuelle de l'American Physical Society en décembre 1959 [6][7]. Le titre de son allocution "There’s Plenty of Room at the Bottom", que l'on peut interpréter par : Il y a plein d'espace en bas de l'échelle, Feynman voulait attirer l'attention sur l'intérêt de la miniaturisation non pas en terme de taille ou de volume mais sur le fait que la miniaturisation d'un système rend possible la multiplication des fonctions réalisées par ce système ou de la quantité d'informations stockée par ce dernier. C'est lui qui le premier parla de micromachines et qui comprit leur intérêt et les problèmes soulevés par la physique et la mécanique des petites dimensions.

C'est quelques années après l'apparition des premiers circuits intégrés en 1958, par le récent prix Nobel jack Kilby, que l'on découvrit la possibilité de fabriquer des structures mécaniques avec des technologies dérivées de la microélectronique et notamment la lithographie et le dépôt de couches minces [8]. Les développements de la micro-mécanique ont étés motivés par le fait que les matériaux de la microélectronique comme le silicium et le polysilicium possédaient des propriétés mécaniques intéressantes pour les applications visées. En effet le silicium et le polysilicium ont des modules d'Young très élevés (respectivement 190 et 160 Gpa) et ils travaillent presque toujours dans le domaine élastique et non plastique (pas d’hysteresis). Dans les années 80 les travaux portèrent sur les propriétés du silicium et du polysilicium en tant que jauge [3] par l'utilisation de propriétés de ces matériaux comme la piézo-résistivité, l’effet Seebeck ou la variation de la résistivité en fonction de la température et qui permirent d’utiliser ces matériaux comme transducteurs. On vit apparaître les technologies de micro-usinage en volume [9] et en surface [10][11][12] qui utilisèrent les techniques de gravure sélective développées pour la micro-électronique. Enfin les premiers capteurs microsystèmes intégrés avec l'électronique, des capteurs de pression, apparurent [13]. Les années 1990 virent l'explosion des applications industrielles et l'apparition de technologies standardisées utilisées pour différentes applications. Ce fut ensuite l'intégration monolithique avec l'électronique et l'apparition des premiers outils de CAO. C'est dans les années 90 également qu'apparurent les initiatives telles que la fabrication multi utilisateurs comme pratiquée par MCNC/CRONOS ou les services CMP et MOSIS et qui permirent l’accès à faible coût à ces technologies.

1.3

Marché et applications industrielles

Le marché global des microsystèmes est complexe à évaluer à cause des différentes définitions accordées aux microsystèmes. Faut-il par exemple faire entrer les capteurs magnétiques à effet Hall qui sont effectivement des capteurs mais ne possèdent par d'éléments mécaniques ? Dans le même registre, les détecteurs CCD ou APS font-ils partie de la famille des microsystèmes ?

Les études de marché effectuées montrent que le marché mondial des microsystèmes atteignait 12 milliards de dollars en 1996 et 34 milliards prévus à l'horizon 2002. Les deux tiers de ce marché sont en gros consacrés aux têtes de lecture de disques durs et aux têtes d'imprimantes à jets d'encre [14]. Le dernier tiers est consacré aux capteurs de pression, aux accéléromètres et capteurs inertiels, aux imageurs infrarouges, aux systèmes de projection à micro-miroirs et aux microsystèmes biomédicaux. De nombreuses applications n'ont pas encore atteint le stade de commercialisation massive mais vont sans doute l'atteindre dans les prochaines années. Ce sont par exemple les biopuces, les multiplexeurs de fibres optiques, les éléments passifs pour la radiofréquence et beaucoup d'autres applications. Le chapitre 2.2 sera consacré aux solutions apportées par les microsystèmes dans différents domaines d'applications.

qualité et de fiabilité réclamé par les intégrateurs au niveau système. L'augmentation importante de la complexité des circuits intégrés de dernière génération impose que le test soit inclus au niveau de la conception non plus uniquement pour des raisons de coût mais simplement pour des raisons de testabilité. En effet comment entreprendre le test d'un circuit contenant 40 millions de transistors (cas du pentiumIII) si ce n'est en ayant recours à des techniques spéciales ? Les travaux concernant le test structurel des circuits intégrés qui ont étés menés dès l'apparition des circuits intégrés complexes ont permis l'apparition de techniques de test permettant d'opérer des procédures de test rapides et dont le niveau de qualité, c'est à dire la qualité d'une procédure de test à détecter les défauts potentiels d'un circuit, est connu.

Les microsystèmes ayant suivis une évolution en marge des circuits intégrés, on est en droit de se poser des questions concernant le test des futures applications microsystèmes et de se demander si les techniques développées pour les circuits intégrés peuvent s'appliquer aux microsystèmes. L'objectif de cette thèse est alors de transposer les techniques de test structurel issues de la microélectronique aux nouvelles technologies microsystèmes.

On assiste également, à l'heure actuelle aux développements de Systèmes sur une puce ou SoC (pour System On a Chip), qui sont en fait l'intégration au niveau monolithique de circuits qui autrefois étaient intégrés au niveau carte. Cette nouvelle philosophie de conception permet d'intégrer dans un même circuit des parties numériques (logique, mémoires), des parties analogiques et bientôt des sous-ensembles microsystèmes. Le Tableau 1 recense les estimations des dates d’apparition de l’intégration de différentes technologies en System On a Chip sur les technologies CMOS standard. On remarque que les premières applications System On a Chip contenant des parties microsystèmes devraient apparaître vers 2002. Logique SRAM FLASH E-DRAM RF CMOS FPGA MEMS FRAM Capteurs chimiques Optoélectronique Electro-biologique 98 99 00 01 02 03 04 05 06 07 08 09 10 11 12

Tableau 1 : Estimation de la date d’apparition de l’intégration de différentes technologies en System On a Chip sur les technologies CMOS standard (source International technology Roadmap for Semiconductors, 1999 edition).

Au niveau du test de ces System On a Chip, l'intégration implique l'unification des méthodes et des équipements de test. Cet état de fait impose plusieurs contraintes aux microsystèmes, notamment en ce qui concerne l'application des stimuli de test et la compatibilité avec les futures normes de conception en vue du test comme IEEE P15002 et IEEE 1451.23 . C'est pourquoi nous allons consacrer un chapitre à la génération de stimuli de test multidisciplinaires, c'est à dire mécanique, optique, électrostatique etc., directement sur la puce. Ceci en vue de doter les parties microsystèmes de fonctions "self test" exploitables plus tard pour le test d'un System On a Chip contenant des parties microsystèmes.

2 IEEE P1500 : Standard for Embedded Core Test : projet de norme internationale définissant des méthodes de

test pour des systèmes sur une puce contenant des cœurs embarqués.

1.5

Structure de la thèse

Cette thèse concerne la transposition aux microsystèmes des techniques de test structurel utilisées pour le test de production des circuits intégrés numériques et analogiques. Ces techniques sont la simulation de fautes et la "conception en vue du test"4. Ces techniques se basent sur la détection des défauts de fabrication potentiellement présents en sortie de fabrication. Pour mener à bien l'élaboration de ces techniques de test nous avons donc exploré à la fois les domaines technologiques pour arriver à élaborer une liste de défauts à rechercher lors du test mais également les domaines de la conception des microsystèmes et de la modélisation de fautes. De fait, cette thèse est à cheval entre la science du test des circuits intégrés et le monde des microsystèmes et de leurs technologies. C'est pourquoi ce manuscrit de thèse comprendra des chapitres introductifs à ces deux domaines.

Après ce premier chapitre introductif, le second chapitre donnera une aperçu des différentes technologies de fabrication des microsystèmes en se focalisant plus spécialement sur les technologies intégrées avec l'électronique. La seconde partie du chapitre sera consacrée aux solutions apportées par les microsystèmes dans plusieurs domaines d'applications tels que le spatial, l'automobile, le biomédical, etc. Un exemple de dispositif microsystème intervenant à de multiples reprises tout au long de ce manuscrit, le micro-résonateur électrostatique à peignes interdigités, sera étudié un peu plus en détail.

Le chapitre 3 sera consacré à la fiabilité et à l'étude des mécanismes de défaillances et des défauts potentiels des microsystèmes; ceci afin de servir de base aux techniques de test structurel basé sur la détection des défauts de fabrication. Cette partie concernant les aspects technologiques de la fabrication des microsystèmes a été menée en parallèle à mes activités au sein du service de prototypage de microsystèmes au CMP. En effet, l'accès aux différentes technologies microsystèmes offertes par le CMP nous a permis de mener une grande quantité d'observations sur des dispositifs microsystèmes fabriqués. Ces observations nous ont permis de dresser une liste de défauts de fabrication et de leurs mécanismes de défaillance associés.

Le chapitre 4 entrera dans le domaine du test des circuits numériques et analogiques et en particulier dans les techniques de test structurel basées sur la simulation de fautes et sur les techniques de conception en vue du test. Ce chapitre essaiera d'introduire ces techniques de manière à comprendre dans quelles mesures elles pourront s'appliquer au cas des microsystèmes.

Le chapitre 5, consacré lui directement à la modélisation et à la simulation de fautes des microsystèmes, tentera de définir une méthodologie de test et de l'appliquer à quelques exemples. Ce chapitre se focalisera surtout sur la problématique de la modélisation des microsystèmes et tentera de trouver quel niveau de modélisation est le plus adapté à la simulation de fautes pour permettre d'utiliser ou d'adapter des outils spécifiques de simulation de fautes déjà existants.

Enfin le chapitre 6 s'intéressera aux techniques de conception en vue du test adaptées aux microsystèmes. Ces techniques, de plus en plus utilisées dans les circuits intégrés, vont dans le futur s'imposer à l'ensemble des blocs composant un System On a Chip. Dans l'optique d'une future intégration des microsystèmes en System On a Chip, nous étudierons les possibilités d'intégrer des fonctions d'auto test et de génération in situ de stimuli de test à des dispositifs microsystèmes. Ces concepts seront ensuite appliqués à des exemples de réalisations microsystèmes comme le capteur d'empreintes digitales à micropoutres et à un détecteur infrarouge non refroidi à thermopiles.

Références

[1] S.M. Sze, "Semiconductor Sensors", John Wiley and Sons, Inc., New York, 1994.

[2] J.W. Gardner, "Microsensors Principles and Applications", John Wiley and Sons Ltd., Chichester, England, 1994.

[3] K.E.Peterson, "Silicon as a mechanical material". In Proc. IEEE, 70 (1982), pp. 420-457.

[4] S. Middelhoek et S.A. Audet, "Silicon Sensors", Harcourt Brace Jovanovich Publishing, London, 1989.

[5] J. Gleick, "Le Génial Professeur Feynman", Editions Odile Jacob, 1994.

[6] Richard P. Feynman, "There’s Plenty of Room at the Bottom". In J. MEMS, Vol.1 No. 1, March 1992. (Transcription d'une allocution donnée par Richard P. Feynman le 36 décembre 1959 à la réunion annuelle de l'American Physical Society au California Institute of Technology).

[7] http://www.zyvex.com/nanotech/feynman.html

[8] H.C. Nathanson et R.A. Wickstrom, "A resonant-gate silicon surface transistor with high Q bandpass properties", In Appl. Phys. Lett., 7 (1965) 84.

[9] G.T.A. Kovacs, et al., "Bulk Micromachining of Si", In Proc. IEEE, Vol. 86, Aug 1998.

[10] M. Mehregany, et al., "Integrated fabrication of polysilicon mechanisms". In IEEE Trans. on Electron Devices, ED-35, 1988.

[11] R.T. Howe, "Surface micromachining for microsensors and microactuators". In Jour. Vac. Sci. Technol., 16, 1988.

[12] M. Mehregany et al., "Integrated fabrication of polysilicon mechanisms", In IEEE Trans. on Electron Devices, ED-35, 1988.

[13] W.H. Ko, M.H. Bao, Y.D. Hong, "A high sensitivity integrated circuit capacitive pressure transducer". In IEEE Trans.Elect. Dev., ED-29 (1982) 48-56.

[14] N.J. Nielsen, "History of ThinkJet printhead development", In Hewlett-Packard Journal Volume 36, Number 5, May, 1985.

2

Technologies et applications microsystèmes

Le but de ce chapitre est de donner un aperçu détaillé des différentes technologies de fabrication des microsystèmes pour introduire l'étude des mécanismes de défaillance liée à ces technologies. Les technologies microsystèmes ne sont pas aussi standardisées que les technologies de circuits intégrés et les développements technologiques sont plus souvent tirés par les applications. De ce fait les technologies microsystèmes sont très différentes les unes des autres. Cependant il apparaît quand même des classes de technologies que l’on peut apparenter aux diverses technologies de circuits intégrés et qui supportent des applications différentes. C’est pourquoi nous allons nous intéresser aux deux technologies les plus courantes à savoir le micro usinage en volume et le micro usinage en surface. En ce qui concerne les applications, nous montrerons différents types d’applications classées par domaine d'application comme le biomédical, l'automobile, la spatial, etc.

2.1

Les technologies microsystèmes

2.1.1

Le micro-usinage en volume

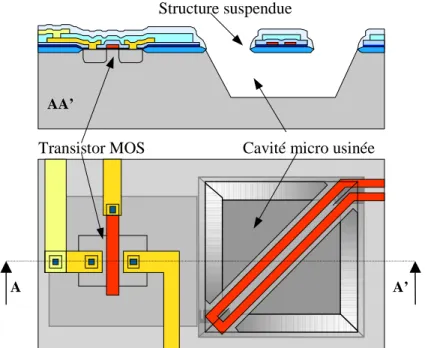

Le micro-usinage en volume est une technique qui permet l’obtention de microstructures suspendues par gravure chimique du substrat d’un circuit intégré. Le terme en volume est utilisé ici puisque l’attaque chimique forme une cavité dans le volume du substrat sous les couches déposées. Cette technique est généralement utilisée directement à partir d’une technologie micro-électronique, les structures suspendues étant obtenues après le post process spécifique. Dans le cas du micro-usinage en volume face avant le post process ne nécessite qu’une étape de gravure anisotropique. La définition des zones à graver se faisant simplement en empilant les ouvertures dans les différents oxydes au niveau layout de manière à laisser une zone où le matériau du substrat est à nu. La Figure 2 montre un schéma représentant une coupe verticale d’un process CMOS micro usiné en surface. On remarque à coté d’un transistor la cavité micro usinée laissant les couches déposées suspendues. A partir de là, la solution de gravure anisotropique va creuser dans le volume du substrat libérant des structures composées d’un sandwich des couches d’oxydes et des couches de polysilicium, de métal et de passivation. A ce titre la Figure 3 montre une photo MEB5 d'une microstructure suspendue au-dessus d'une cavité obtenue par gravure anisotropique. La micropoutre a été dessinée en décalant les différentes couches d'oxyde de manière à observer la structure en sandwich. L'extrémité de la poutre sans oxyde laisse apparaître les couches de barrières de diffusion, sous le polysilicium, ce dernier ayant été gravé par la solution de gravure anisotropique. Une des principales filières est le micro-usinage en volume face avant compatible CMOS qui permet à partir d’une technologie industrielle standard et en rajoutant un simple post process de gravure sans niveau de lithographie additionnel d’obtenir des structures microsystèmes suspendues. Le post process est une gravure anisotropique du silicium du substrat réalisée avec des solutions de gravure du type KOH6 ou TMAH7.

Transistor MOS Cavité micro usinée Structure suspendue

A’ A

AA’

Figure 2 : Schéma en coupe d’une technologie de micro usinage en volume face avant compatible CMOS.

Figure 3 : Image MEB d’une microstructure obtenue par micro-usinage en volume face avant et montrant la composition en sandwich des structures suspendues.

2.1.1.1

La gravure anisotropique du silicium

La gravure anisotropique du silicium [1][2] est une réaction chimique en phase liquide entre la solution de gravure et le silicium et dont la cinétique est commandée par l’orientation cristallographique des surfaces de contact. En effet la vitesse de gravure exprimée le plus souvent en µm.mn-1 dépend de l’orientation cristallographique de la surface en contact avec la solution. Par exemple les faces (111) du silicium ont des vitesses de gravures de plusieurs ordres de grandeurs inférieurs à ceux de plans "rapides" comme les plans (100). La Figure 4 montre le diagramme polaire des vitesses de gravure du silicium pour une solution de TMAH 10%, le schéma montre que la vitesse de gravure des plans (111) est très faible (mais pas nulle) par rapport aux plans (100) (surface des wafers) et aux plans (314).

(100)

(314)

(111)

Figure 4 : Diagramme polaire des vitesses de gravure du TMAH.

2.1.1.2

Intérêt de la gravure anisotropique

L’intérêt de la gravure anisotropique pour fabriquer des microstructures suspendues tient au fait qu’en définissant simplement une ouverture vers le silicium du substrat il est possible d’obtenir une cavité sous des structures suspendues (comme une gravure isotropique) mais également une cavité qui reste confinée par les plans d’arrêt virtuel (111) comme le ferait une gravure plasma de type RIE8. Ceci est possible du fait des très faibles vitesses de gravure des plans (111) mais également du fait des effets de bords qui permettent de graver des structures convexes. La Figure 5 montre la progression de la gravure anisotropique définie par un masque comportant deux ouvertures triangulaires orientées selon les axes CAO9.

(111)

(100) (314)

Figure 5 : Schéma représentant l’avancée de la gravure anisotropique à partir d’ouvertures triangulaires.

On peut noter que la solution commence par consommer le plan (100) tout en formant les plans d’arrêt virtuels (111).L’effet de bord sur les parties convexes vient créer des plans (314) "rapides" permettant de libérer complètement la structure et d’obtenir une cavité en forme de pyramide inverse. Le résultat d’une telle gravure peut alors être observé sur la photo MEB de la Figure 6 où l’on voit une structure en pont au-dessus d’une cavité pyramidale.

Figure 6 : Photo MEB d’une microstructure en pont obtenu par micro usinage en volume par gravure anisotropique du silicium du substrat.

2.1.1.3

L’anisotropie de la réaction de gravure

L’anisotropie d’une réaction de gravure humide d’un monocristal est un phénomène complexe. Nous n’entrerons pas ici en détail dans les phénomènes mis en jeux mais il semble que l’explication de ce caractère anisotropique vienne des différences d’orientation des hybridations orbitales sp3 entre les différents plans cristallographiques qui créeraient des différences de vitesse de gravure. L’effet de bord ou undercutting qui permet l’apparition de plans rapides à l’intersection de plans (111) est également un phénomène complexe. Des publications traitent de ce sujet [3][1][2].

2.1.1.4

Les solutions de gravure anisotropique du silicium

Les solutions de gravure du silicium présentant un caractère anisotropique sont des hydroxydes : KOH, NaOH, CeOH, RbOH, NH4OH, TMAH. Pour cette dernière, la réaction se déroulant est alors

l’oxydation du silicium par les hydroxydes pour former un silicate :

( )

++ +−

+

→

+

2

OH

4

H

Si

OH

2Si

Les silicates réagissent ensuite avec les hydroxydes pour former un complexe soluble dans l’eau :

( )

OH

OH

SiO

( )

OH

H

O

Si

2+

4

→

2 2+

2

2 − − − + +Les solutions les plus souvent utilisées pour la gravure anisotropique du silicium sont l’hydroxyde de potassium (KOH), qui offre une très grande anisotropie mais a le défaut d’être peu sélectif envers l’aluminium ce qui pose des problèmes quant aux plots de connexions dans les technologies CMOS. De plus la présence d’ions potassium qui sont des polluants des circuits CMOS est extrêmement gênante pour la compatibilité avec les process microélectronique. Les vitesses de gravure typiques du silicium dans une solution de KOH à 80°C sont de 1µm.mn-1 et de 20 Angstrom.mn-1 pour l’oxyde de silicium. L’anisotropie de gravure est de 1 pour 400 entre les plans (111) et (100). La seconde solution de gravure anisotropique du silicium est l’éthylène dyamine pyrocathécol (EDP) qui bien qu’offrant de meilleures caractéristiques de sélectivité reste peu employée du fait de sa très haute toxicité et de son interdiction en salle blanche. La vitesse de gravure typique du (100) du silicium dans une solution EDP à 80°C est de 20µm.mn-1 ce qui est beaucoup plus grand que le KOH, l’anisotropie est de 1 pour 35 entre les plans (111) et (100). La dernière solution de gravure est l’hydroxyde de tétra-méthyle ammonium (TMAH) qui bien que d’un emploi délicat du fait de sa nature organique qui lui confère une faible stabilité, reste la solution offrant les meilleurs résultats en termes de vitesse de gravure, d’anisotropie et de sélectivité par rapport à l’aluminium. De plus elle est totalement compatible avec les procédés de fabrication de la microélectronique. Une solution de gravure à base de TMAH a été développée [4] au laboratoire TIMA en collaboration avec la société IBS et est utilisée comme post process des technologies bulk micromachining au CMP. Dans la suite de cet exposé la majeure partie des microsystèmes présentés ont étés gravés avec cette solution.

2.1.1.5

La simulation de gravure anisotropique

La simulation de la gravure anisotropique peut s’effectuer selon deux approches distinctes, la simulation géométrique et la simulation atomistique. Dans le premier cas la progression de la gravure au cours du temps est représentée par l'évolution de vertex définissant l'intersection de plusieurs plans. En fonction des vitesses de gravure de ces plans la position de vertex évolue et peut mener à la disparition ou à l'apparition de nouveaux plans. Plusieurs algorithmes de simulation géométrique de la gravure anisotropique existent et ont étés utilisés pour construire des simulateurs. La Figure 7 montre une comparaison entre la simulation de gravure anisotropique géométrique réalisée avec le simulateur 2D ACCESIM développé au laboratoire TIMA et une photo MEB d’une structure à membrane identique dont la gravure est incomplète. On remarque la fidélité du profil simulé.

(a) (b)

Figure 7 : Simulation géométrique (a) de la gravure anisotropique d’une membrane soutenue par quatre bras à 45°, et photo MEB (b) de la même structure avec gravure TMAH incomplète.

La seconde méthode, la simulation atomistique est basée sur la discrétisation d’un volume en points (les atomes) d’un réseau régulier, comme un réseau d’atomes dans un cristal. L’algorithme [5] va alors, pas à pas, calculer l’orientation du plan formé par un point et ses proches voisins puis en extraire une vitesse de gravure correspondante. En fonction du pas de calcul et de la vitesse de gravure déterminée, l’atome sera alors déclaré gravé ou pas. La Figure 8 montre une simulation atomistique en 3 dimensions de la progression de la gravure anisotropique d’une structure en forme de membrane soutenue par quatre bras à 45°. Cette simulation a été effectuée avec le simulateur de gravure anisotropique ACES [6].

2.1.1.6

Les différents types de micro usinage en volume

Le micro-usinage en volume face avant compatible CMOS [9] permet d’obtenir facilement des structures suspendues sans étapes de lithographies supplémentaires. La Figure 9 montre les différentes structures qu’il est possible d’obtenir, une structure suspendue en forme de pont (a), de poutre (b) ou de membranes suspendues par des bras de support (c).

(a) (b) (c)

Figure 9 : Schéma des différentes microstructures que l’on peut obtenir par micro usinage en volume face avant.

En opérant une gravure assez longue, il est possible aussi de traverser l’épaisseur du wafer de manière à laisser une masse suspendue à une membrane [4]. La gravure s’opérant également par la face arrière du wafer (dans le cas d’une gravure au niveau puce). Néanmoins cette technique impose une taille assez grande de la structure suspendue (typiquement 800µm de coté). La Figure 10 illustre cette technique et montre une membrane suspendue par quatre bras de support et à laquelle est accrochée une masse en silicium de forme tronconique. On remarque au passage que la forme coudée des bras de support est une méthode pour retarder la gravure de la masse centrale par les effets d’arêtes au moment de la gravure anisotropique. De fait la masse suspendue n’est pas tout à fait pyramidale mais arrondie au niveau des arrêtes. Une masse suspendue de ce type peut alors faire office de masse sismique dans des applications de capteurs inertiels ou de masse thermique.

Masse suspendue

Bras de support

Figure 10 : Schéma d’une structure à masse suspendue obtenue en micro usinage en volume face avant.

2.1.1.7

Le micro-usinage en volume face arrière

Le micro-usinage en volume face arrière nécessite quant à lui une étape supplémentaire de lithographie de manière à créer un masque pour la gravure anisotropique. Cette étape de lithographie

doit être alignée par rapport à la face avant, ce qui nécessite l’emploi d’un aligneur double face. De plus cette technique impose de travailler au niveau wafer et non au niveau puce comme c’était le cas pour le micro-usinage de surface en face avant. La Figure 11 montre les structures qu’il est possible d’implémenter avec cette technique. La Figure 11(a) montre une membrane close obtenue par gravure en face arrière, c’est cette technique qui est employée dans les capteurs de pressions ou la déflexion de la membrane suite à une différence de pression entre ses deux faces est mesurée. Notons aussi que la cavité formée sous la membrane peut être fermée par collage du dispositif sur une surface de silicium (wafer bonding) et mettre ainsi une référence de pression dans la cavité, on a alors un capteur de pression absolue. La Figure 11(b) montre une membrane close à laquelle est attachée une masse suspendue, pour des applications thermiques ou de capteurs inertiels.

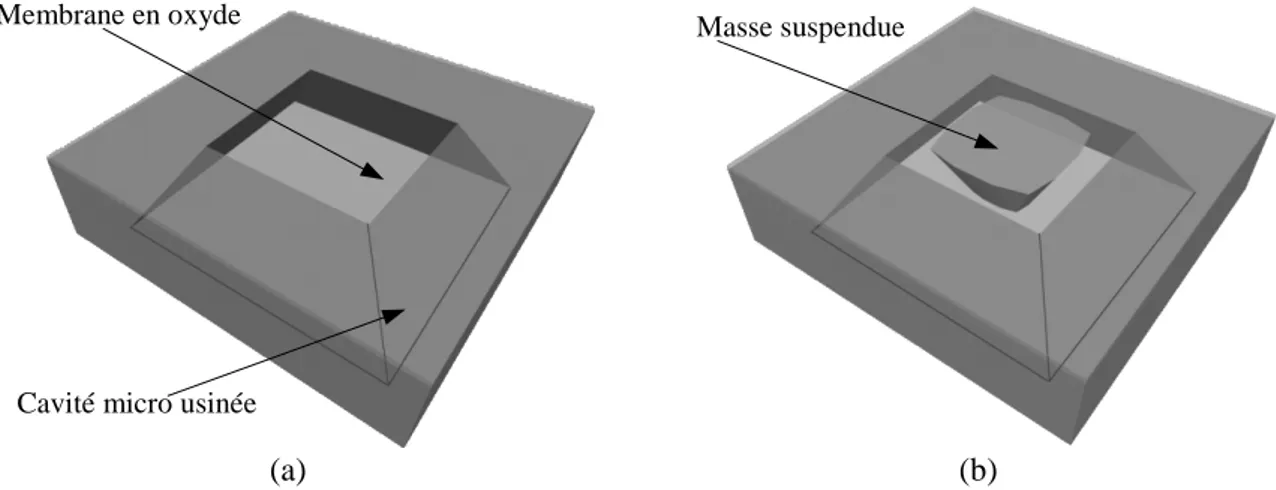

Membrane en oxyde

Cavité micro usinée

Masse suspendue

(a) (b)

Figure 11 : Schéma des différentes structures résultantes d’un micro-usinage en volume face arrière.

2.1.1.8

Le micro-usinage en volume face avant et arrière

En combinant le micro-usinage en volume face avant et face arrière, il est possible d’obtenir des structures suspendues avec masse attachée. L’intérêt de cette méthode est que la gravure va s’opérer des deux cotés en même temps ce qui va diminuer le temps de gravure nécessaire pour suspendre complètement une masse de silicium. De plus la taille minimum des ouvertures à pratiquer sera plus petite. La Figure 12 montre un schéma en coupe d’une structure à masse suspendue analogue à celle présentée en Figure 10 mais cette fois ci obtenue en micro usinage en volume face avant et face arrière. On remarque la forme en diamant de la masse suspendue et la superposition dans le plan des masques de gravure avant et arrière.

Masse suspendue

2.1.1.9

Le micro-usinage en volume électrochimique.

Cette technique de gravure exploite l’effet de la polarisation électrique d’un matériau sur les vitesses de réaction de gravure. Dans le cas du micro-usinage en volume, la gravure électrochimique [7] permet d’obtenir des couches d’arrêt de la gravure simplement en polarisant les caissons (n uniquement) implantés dans le silicium. La gravure anisotropique s’opérant en phase liquide, on doit prendre une référence de potentiel dans la solution. Il est possible alors d’obtenir des structures à membrane épaisse formées par les zones implantées n non gravées comme le montre la Figure 13. Une autre possibilité est de suspendre des zones de silicium isolées contenant de l’électronique (uniquement Pmos) qui serait isolée électriquement et thermiquement du substrat.

n n

Masse de silicium suspendue

Arrêt de la réaction de gravure sur le caisson n

(a) (b)

Figure 13 : Schéma en coupe de structures suspendues par micro usinage électrochimique en volume, face arrière (a) et face avant (b).

2.1.2

Le micro-usinage en surface

Le micro-usinage en surface est basé sur l’emploi de couches sacrificielles. Ces couches vont être gravées entièrement à la fin du process par une étape de gravure sélective et isotropique. Le terme micro-usinage en surface vient par opposition à l’expression micro-usinage en volume car ici la gravure n’attaque pas le silicium du substrat (bulk). Pendant le process les couches déposées vont être une succession de couches sacrificielles de dioxydes de silicium et de couches structurelles de polysilicium. Au cours du process les couches d’oxydes sacrificielles sont gravées de manière à définir les zones d’ancrages des structures en polysilicium sur le substrat ou sur le niveau inférieur. La Figure 14 montre un schéma en coupe d’une technologie de micro usinage en surface avant (a) et après (b) gravure des oxydes sacrificiels. On peut remarquer au passage la couche de nitrure sur tout le substrat, les trois couches structurelles de polysilicium ainsi que les couches d’oxydes sacrificielles et les zones d’ancrage. La gravure des oxydes sacrificiels est généralement opérée par de l’acide fluorhydrique à 49%, suivi par une étape de séchage au CO2 supercritique pour éviter les problèmes de collage qui

seront détaillés au chapitre 3.

polysilicium métal Oxydes sacrificiels

Silicium (a) Nitrure (b)

Figure 14 : Schéma en coupe d’une technologie de micro usinage en surface avant (a) et après (b) gravure des oxydes sacrificiels.

2.1.2.1

La micromécanique

Un des aspects intéressant des technologies de micro usinage en surface est la possibilité de fabriquer des éléments mécaniques en 3 dimensions. On peut alors créer des systèmes mécaniques complexes comprenant des moteurs, rotatifs ou linéaires, des chaînes de transmission du mouvement comme des engrenages, des bielles et des paliers. La Figure 15 montre différents éléments permettant de construire des systèmes mécaniques complexes, la photo (a) représente une charnière faite avec deux niveaux de poly et permettant de créer une liaison pivot, la photo (b) montre des dents d’engrenage qui ne sont pas engrenées. La photo (c) représente le détail d’un ressort rotatif.

(a) (b) (c)

Figure 15 : Photos MEB d’éléments micromécaniques fabriqués par micro usinage de surface (technologie MUMPS), charnière (a), dents d’engrenage (b), ressort pivotant (c).

2.1.2.2

Les principaux fondeurs multi-utilisateurs

Il y a deux principaux fondeurs qui offrent un accès multi-utilisateurs à leur technologie. Ce sont CRONOS [10] avec la technologie MUMPS et SANDIA national labs avec les technologies SUMMIT et SUMMIT V. La technologie MUMPS est une technologie de micro usinage en volume offrant 3 niveaux de polysilicium dont deux niveaux structurels. Le premier niveau Poly 0 sert uniquement à des fins de routage électrique et d’électrodes, il n’est pas suspendu. Les niveaux poly1 et poly2 avec respectivement 2µm et 0.75µm d’épaisseur forment les structures suspendues. Une couche de métal (or) peut être déposée sur le dernier niveau de polysilicium à des fins de routage faiblement résistif ou pour des applications optiques.

Poly0

Poly1

Poly2

dimples

Figure 16 : Photo MEB d’un micromoteur électrostatique fabriqué en technologie MUMPS. Cette technologie correspond au schéma de la Figure 14. La photo MEB de la Figure 16 montre un micromoteur électrostatique fabriqué avec la technologie MUMPS, on remarque les niveaux poly0 qui forme l’électrode de polarisation du rotor, le niveau poly 1 qui forme le rotor mobile et les 12 électrodes fixes ainsi que le niveau poly 2 qui est employé pour le pivot central et la bague d’arrêt verticale. Le second fondeur, les laboratoires SANDIA [11] ont un procédé microsystème similaire à base de polysilicium et de couches d’oxydes sacrificiels contenant 3 (SUMMIT) et 5 (SUMMIT V)

![Figure 40 : Vue en coupe d’une particule métallique, réalisée par microscope à faisceau d’ions focalisés [16].](https://thumb-eu.123doks.com/thumbv2/123doknet/14603873.731494/56.892.229.665.627.946/figure-coupe-particule-métallique-réalisée-microscope-faisceau-focalisés.webp)