HAL Id: pastel-00998731

https://pastel.archives-ouvertes.fr/pastel-00998731

Submitted on 2 Jun 2014HAL is a multi-disciplinary open access archive for the deposit and dissemination of sci-entific research documents, whether they are pub-lished or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L’archive ouverte pluridisciplinaire HAL, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d’enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Gutemberg Gonçalves dos Santos Junior

To cite this version:

Gutemberg Gonçalves dos Santos Junior. Robust design of deep-submicron digital circuits. Other. Télécom ParisTech, 2012. English. �NNT : 2012ENST0039�. �pastel-00998731�

T

H

È

S

E

T H È S E

pour obtenir le grade de docteur délivré par

TELECOM ParisTech

Spécialité « Communications et Electronique »

présentée et soutenue publiquement parGutemberg GONÇALVES DOS SANTOS JÚNIOR

le 6 septembre 2012Conception Robuste de Circuits Numériques

à Technologie Nanométrique

Directeurs de thèse : Mme. Lirida NAVINER

M. Jean-François NAVINER

Jury

M. Raoul Velazco,Directeur de recherche, CNRS-TIMA Rapporteur

M. Luis Entrena,Professeur, Université Carlos III Madrid Rapporteur

M. Habib Mehrez,Professeur, UPMC, LIP6 Examinateur

M. Gilles Deleuze,Chercheur senior, EDF R&D Examinateur

Mme. Lirida Naviner,Professeur, Télécom Paristech Directrice de Thèse

M. Jean-François Naviner,Maître de conférences, HDR, Télécom Paristech Directeur de Thèse

TELECOM ParisTech

Thèse

Robust Design of Deep-Submicron Digital Circuits

Gutemberg GONÇALVES DOS SANTOS JÚNIOR

Directeurs de thèse Pr. Dr. Lirida NAVINER Dr. Jean-François NAVINER

“Education is the most powerful weapon which you can use to change the world.”

Nelson Mandela

“Il n’y a aucune connaissance de la terre qui ne commence par l’imagination. Lorsqu’elle disparaît, lorsque se brise la création par l’imaginaire, la curiosité s’évanouit avec elle et le savoir s’épuise.”

Acknowledgement

Working on a Ph.D has been an extraordinary experience. It would not have been possible to succeed without the support of many people who gave of their time tirelessly and patiently in order to make the difficult moments less unbearable.

First and foremost I offer my sincerest gratitude to my supervisors, Dr Lirida Naviner and Dr Jean-François Naviner, without whose sincerity, knowledge, encouragement and assistance this study would not have been successful. I’m deeply thankful for the excellent atmosphere you created for doing research, where everybody could contribute and learn from each other. Besides, you acted not only as a supervisor, but more importantly as a real friend, and I appreciate that from my heart.

I would like to express my deepest gratitude to EDF R&D for the financial support and the opportunity to carry out my research studies. I would like to extend my greet-ings to Bastien Cousin, Laurent Cretinon, Gilles Deleuze, Anne-Lise Didierjean, Laurent Doireau, Sandrine Legruel, and Philippe Mathevon, whose advice, support and patience were fundamental during my studies.

I would like to thank Dr Luis Entrena and Dr Raoul Velazco for agreeing to be the reviewers of this dissertation. Your knowledge and remarks were vital for the improvement of the current work.

Many thanks to all my friends for sharing their enthusiasm for and comments on my work. I would like to thank Alban Gruget, Arthur Liraneto, Arwa Ben Dhia, Bruno Lyra, Chadi Jabbour, Cibele Trinca, Daniel Caon, Davi Bibiano, Dimitri Edouard, Eduardo Fer-raz, Elaine Crespo, Eric Bouton, Fabrice Linot, Farhan Mirani, Florent Lozac’h, Hasham Khushk, Joana Silveira, Julie Gaudin, Maí Correia, Márcia Costa e Silva, Mariem Slimani, Pietro Maris, Sami Mekki, Samuel Pagliarini, Sereuja Zier, Shivam Bhasin, Tian Ban, Yang Liu, and all the other students in Télécom Paristech and friends I made in Paris for the great moments we spent together. Just remembering the happy hours in the “butte-aux-cailles”, the picnics in the parks and on the banks of the Seine, the travels, the dinners in Maisel, and all the parties we went make me laugh and feel good. I’m truly grateful to all of you guys, you are fantastic people, and I hope to see you all again very soon.

all the employees of Télécom Paristech who welcomed me and made my stay so memorable. You helped me so much with my problems, bureaucracy and so many other things that I can’t really imagine finishing this thesis without your help.

I’m especially thankful to my family for their unflagging love, and for always supporting me during difficult times, listening to my worries and complaints.

Abstract

The design of circuits to operate at critical environments, such as those used in control-command systems at nuclear power plants, is becoming a great challenge with the technol-ogy scaling. These circuits have to pass through a number of tests and analysis procedures in order to be qualified to operate. In case of nuclear power plants, safety is considered as a very high priority constraint, and circuits designed to operate under such critical envi-ronment must be in accordance with several technical standards such as the IEC 62566, the IEC 60987, and the IEC 61513. In such standards, reliability is treated as a main con-sideration, and methods to analyze and improve the circuit reliability are highly required. The present dissertation introduces some methods to analyze and to improve the reli-ability of circuits in order to facilitate their qualification according to the aforementioned technical standards. Concerning reliability analysis, we first present a fault-injection based tool used to assess the reliability of digital circuits. Next, we introduce a method to evalu-ate the reliability of circuits taking into account the ability of a given application to tolerevalu-ate errors. Concerning reliability improvement techniques, first two different strategies to se-lectively harden a circuit are proposed. The first one is based on the assumption that some output bits of a circuit may be more important for a given application than the others. Then, the proposed technique drives the reliability improvement effort to those bits. The other technique uses a cost function in order to automatically select the best candidates to be hardened. Finally, a method to automatically partition a TMR design based on a given reliability requirement is introduced.

French Summary

Introduction

Depuis l’avènement de la micro-électronique, ce domaine n’a pas cessé de prendre de l’ampleur. Les technologies de fabrication ont vécu une évolution exponentielle comme prévu par la Loi de Moore [1,2]. Comme résultat, les dispositifs électroniques deviennent de plus en plus petits, plus performants et moins chers.

Afin de continuer l’évolution de la micro-électronique même après l’arrivée des dimen-sions submicroniques, les chercheurs doivent surpasser des défis comme la considération des phénomènes physiques qui auparavant étaient négligeables et maintenant sont prépondé-rants, comme les forces de Casimir et de Van Der Waals [3]. De plus, les systèmes d’inter-connections sont devenus très complexes avec l’arrivée du schéma de connexion 3-D [4]. En fait, l’augmentation de la quantité de composants dans la même puce et l’augmentation de la complexité des interconnections font croître la probabilité de défaillance des composants. En même temps, l’augmentation des fréquences d’opération augmente la probabilité des erreurs de synchronisation [5]. En conséquence, une réduction du rendement de fabrication aussi bien que de la fiabilité des circuits intégrés est attendue [6–10].

Avec l’augmentation de la probabilité de fautes dans les circuits numériques, les sys-tèmes développés pour les environnements critiques comme les centrales nucléaires, les avions et les applications spatiales doivent être certifiés selon des normes industrielles. Cette thèse est un résultat d’une coopération CIFRE entre l’entreprise Électricité de France (EDF) R&D et Télécom Paristech. EDF est l’un des plus gros producteurs d’énergie au monde et possède de nombreuses centrales nucléaires. Les systèmes de contrôle-commande utilisé dans les centrales sont basés sur des dispositifs électroniques, qui doivent être cer-tifiés selon des normes industrielles comme la CEI 62566 [11], la CEI 60987 [12] et la CEI 61513 [13] à cause de la criticité de l’environnement nucléaire. En particulier, l’utilisation des dispositifs programmables comme les FPGAs peut être considérée comme un défi du fait que la fonctionnalité du dispositif est définie par le concepteur seulement après sa conception physique. Le travail présenté dans ce mémoire porte sur la conception de nou-velles méthodes d’analyse de la fiabilité aussi bien que des méthodes d’amélioration de la

fiabilité d’un circuit numérique.

La fiabilité dans les circuits numériques

Un circuit électronique peut être vu comme l’assemblage d’un certain nombre de com-posants électroniques de telle façon qu’il produit une fonctionnalité souhaité. Cette fonc-tionnalité peut être garantie si on considère que les composants sont exempts de fautes. Malheureusement les dispositifs électroniques sont susceptibles de défaillances occasion-nées par des mécanismes naturels comme les impuretés dans les matériaux et les variations de paramètres, entre autres. Pour être précis, il y a une certaine probabilité qu’un cir-cuit numérique va fournir la fonctionnalité souhaitée pendant un période de temps. Cette probabilité est connue comme fiabilité et peut être définie comme suit : la fiabilité est l’ap-titude d’un dispositif à accomplir une fonction requise dans des conditions données pour une période de temps donnée [14].

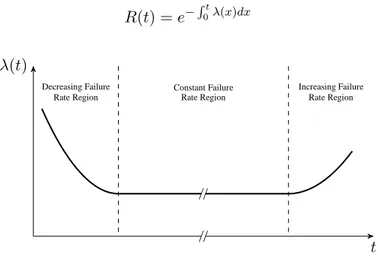

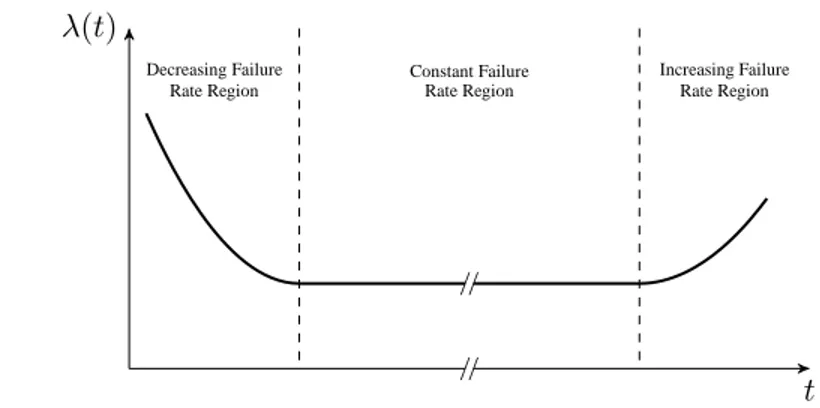

La fiabilité d’un circuit électronique peut être calculée selon (1). Son comportement par rapport au temps peut être divisé en 3 phases (voir Figure1) :

1. Taux de défaillance décroissant → Cette phase de vie est aussi appelée période de jeunesse.

2. Taux de défaillance sensiblement constant → C’est aussi appelé période de vie utile du dispositif.

3. Taux de défaillance croissant → Correspond à la période de vieillissement du circuit

R(t) = e−R0tλ(x)dx (1) // λ(t) t // Decreasing Failure Rate Region Constant Failure Rate Region Increasing Failure Rate Region

Figure 1 – Courbe en baignoire

Parmi les types de fautes qui peuvent occasionner une défaillance du système électro-nique, les fautes transitoires sont particulièrement une menace à cause de leur

comporte-de durcissement d’un circuit intégré. Cela représente toujours un surcoût en surface, en consommation ou en vitesse. Ainsi, les méthodes d’analyse de la fiabilité d’un circuit intégré deviennent de plus en plus importantes avec l’évolution de la technologie. C’est grâce à ce type d’analyse que les concepteurs peuvent identifier les zones de défaillance potentielles, la nécessité d’ajout de redondance, la nécessité d’un système de sauvegarde, etc. De plus, les méthodes d’analyse de la fiabilité peuvent être utilisées comme un outil pour mesurer la performance de différentes stratégies de durcissement d’un circuit intégré.

Plusieurs méthodes d’analyse de la fiabilité d’un circuit ont été reportées dans la lit-térature. C’est bien connu qu’une analyse optimale doit prendre en considération autant d’information que possible du circuit lui-même aussi bien que de l’application cible. En dé-pit de cela, la plupart de méthodes d’analyse de fiabilité considère quelques simplifications dans les modèles mathématiques comme la considération de fautes simples, de signaux non corrélés, etc. En outre, peu de travaux sur l’analyse de la fiabilité ont été effectués tenant en compte l’importance des résultats du circuit pour l’application cible. En fait, beaucoup d’applications présentent la capacité de tolérer un certain nombre et certains types d’er-reurs. En considérant cette information, un concepteur peut mieux contrôler l’ajout de redondance afin d’éviter un surcoût trop élevé. La première contribution de ce travail est une technique nommée « effective reliability » qui prend en considération la tolérance aux erreurs d’une application pour évaluer la fiabilité du circuit.

Effective Reliability

L’augmentation considérable du nombre d’erreurs attendue dans les circuits avec l’évo-lution de la technologie a inspiré les discussions sur la tolérance aux erreurs depuis la sortie du « 2001 International Technology Roadmap for Semiconductors (ITRS) ». Le concept de tolérance aux erreurs a été introduit comme un paradigme orienté à l’application pour faire face aux variations du processus, aux défauts et au bruit [7]. L’idée principale est de que certaines applications présentent la capacité de tolérer un certain nombre et certains types d’erreurs à condition qu’ils soient limités à un certain niveau de sévérité défini par l’application. En effet, plusieurs applications multimédia présentent cette caractéristique grâce au fonctionnement des sens humains comme la vue, l’audition et l’odorat, qui ne peuvent pas s’apercevoir de la présence de certains types d’erreurs. Ce mémoire se réfère à ce type de phénomène comme les masquages des erreurs par l’application et introduit la

classification d’erreurs suivante :

– Erreurs critiques → Ce sont les erreurs qui peuvent occasionner un grand impact dans les résultats produits par un circuit ;

– Erreurs non-critiques → Ce sont les erreurs qui sont masquées par l’application.

Cette classification des erreurs prend en considération l’usage des résultats produits par un circuit. Par conséquence, un facteur très important qui affecte ce type de classifica-tion est l’approche de codificaclassifica-tion utilisée pour représenter l’informaclassifica-tion dans la sortie du circuit. En fait, l’impact d’une inversion d’un bit de sortie du circuit dépend directement de son poids, c’est-à-dire de sa signifiance relative par rapport au mot de sortie. En dépit de cela, le concept traditionnel de fiabilité d’un circuit (appelé fiabilité nominale dans ce mémoire) est basée sur le paradigme de passer ou échouer, c’est-à-dire il ne prend pas en considération l’importance d’un bit de sortie comme décrit en (2).

Rnom= M −1

Y

i=0

qi (2)

Pour faire face à ces problèmes, nous proposons le concept de « effective reliability » comme décrit par (3) et (4). Dans ce cas, le terme Rack représente la probabilité qu’une

erreur soit masquée par l’application cible. Cela veut dire que le terme Rack prend en

considération les erreurs qui sont classées comme non-critiques alors que le terme Rack considère les erreurs critiques. La classification d’une erreur en critique ou non-critique prend en compte des métriques de qualité qui sont considérées pertinentes par rapport à l’application cible. Ce mémoire introduit aussi deux métriques de qualité différentes basées d’importance d’un bit (voir (5) et (6)) et d’erreur relative (voir (7) et (8)).

Ref f = Rnom+ Rack (3) Ref f = 1 − Rack (4) Ref f = M −1 Y i=0 qi+ T +1 X k=1 CkT +1 X r=1 γk,r (5) Ref f = 1 − T +1 X k=1 CM k X r=CT +1 k +1 γk,r− M X k=T +2 CM k X r=1 γk,r (6)

b3 99.24% b4 99.20% b5 99.18% b6 99.17% b7 99.16% b8(retenue) 99.36% Ref f = M −1 Y i=0 qi+ 2H−1 X a=0 p(a) kmax X k=1 CM k X r=1 γk,r.u (δmax− δ(k, r, a)) (7) Ref f = 1 − 2H−1 X a=0 p(a) kmax X k=1 CM k X r=1 γk,r.u (δ(k, r, a) − δmax) (8) Résultats

Prenons comme exemple un additionneur parallèle à propagation retenue de 8 bit (APPR8), construit à partir de 8 additionneurs de 1 bit en chaîne, dans lequel la probabi-lité de défaillance de chaque porte logique est égale à 99.9%. Supposons que la contrainte de fiabilité minimale de l’APPR8 soit Rmin = 95% et que l’application cible présente la

capacité de tolérer des erreurs aussi grandes que 2% du résultat correct (δmax = 2%).

La fiabilité de chaque bit de sortie du APPR8 a été évaluée en utilisant la méthode SPR-MP [15], et les résultats sont illustrés dans le Tableau 1. La concept de fiabilité nominale peut donc être calculée selon (9). En analysant le résultat pour la fiabilité nominale un concepteur ira conclure que l’APPR8 ne respecte pas la contrainte de fiabilité minimale et que le circuit a besoin d’être durci. En considérant la méthode TMR (Triple Modular Redundancy) pour réaliser cette procédure, l’architecture durcie avec moins de surface mais qui encore respecte la contrainte de fiabilité minimale cause un surcoût en surface de 75%.

R =

8

Y

i=0

qi= 94.06% (9)

Rappelons que l’application cible présente la capacité de tolérer des erreurs s’ils ne dépassent pas la contrainte d’erreur relative δmax = 2%. Prenons donc le concept de «

Table2 – Valeurs de Reff pour différentes tolérances aux erreurs (APPR8)

Erreur Relative (δmax) Fiabilité

0.5% 94.23% 1.0% 94.64% 1.5% 94.96% 2.0% 95.22% 2.5% 95.44% 3.0% 95.62% 3.5% 95.77% 4.0% 95.92% 4.5% 96.05% 5.0% 96.16%

dépend de la capacité de l’application cible de tolérer des erreurs (voir Tableau 2). C’est bien noté qu’en considérant une capacité de tolérance d’erreurs δmax = 2% la fiabilité

du circuit pour cette application est égale à 95.22%, c’est-à-dire la contrainte de fiabilité minimale est déjà respectée et en fait il n’y a pas besoin d’ajout de redondance.

Le concept de « effective reliability » est très intéressant pour les applications dans lesquelles un certain nombre d’erreurs peut être toléré. Par contre, dans les applications appelées critiques comme les centrales nucléaires, les avions et les satellites, l’occurrence d’une seule erreur peut causer des conséquences sévères. En fait, les circuits développés pour ces environnements ont besoin d’une couverture de test qui s’approche de 100%. Pour faire face à ces problèmes, la deuxième contribution de ce travail est un outil basée sur Verilog appelé FIFA (Fault-Injection-Fault-Analysis) développé pour accélérer les tests exhaustifs dans les circuits intégrés.

L’outil FIFA

C’est déjà bien connu que l’injection de fautes est une approche intéressant pour ana-lyser le fonctionnement des circuits intégrés en présence de fautes. L’idée principale est d’injecter des fautes dans le circuit de forme aléatoire ou contrôlée et analyser si la faute est propagée jusqu’à la sortie. Comme les circuits intégrés deviennent de plus en plus com-plexes avec l’évolution de la technologie, le temps nécessaire pour atteindre un niveau élevé de couverture de test est très important, voire prohibitif. Cela devient un problème pour les applications qui ont besoin de tel niveau de couverture, et de ce fait le développement des nouvelles méthodes que puissent accélérer la procédure d’injection de fautes devient nécessaire. La deuxième contribution de ce travail est un outil appelé FIFA (Fault-Injection-Faut-Analysis) qui a été développé comme un « hardware IP » pour accélérer l’analyse de fiabilité basée sur l’injection de fautes. Cet outil est adapté à différents modèles de fautes

saboteur est un dispositif électronique capable de changer la valeur logique d’un nœud du circuit. Le saboteur qui a été développé pour l’outil FIFA supporte quatre types de fautes différentes : les inversions de bit, les collages à zéro, les collages à un, et les hautes impédances. Son schéma est illustré dans la Figure 3.

Figure 2 – Schéma général de l’outil proposé

Node j ej m1 m0 Node je 00 01 10 11 Saboteur “j” 0 1 Z sel[s1:s0]

Figure 3 – Schéma général d’un saboteur

L’évaluation de la fiabilité d’un circuit à partir des résultats fournis par l’outil FIFA est basée sur la méthode PBR [16]. Le module «fault generator» a été développé pour générer des erreurs en ordre croissante de multiplicité, de sorte que le concepteur peut limiter le nombre de tests à effectuer s’il connaît le nombre maximal de fautes simultanées. Afin d’analyser la performance et la quantité de ressources utilisées par l’outil FIFA, nous l’avons comparé avec une plateforme reportée dans la littérature nommée FuSE [17].

Table3 – Plate-forme Fuse vs. outil FIFA

Fuse [17] FIFA

ALUTs 2157 817

Registres 694 467

Fréquence maximale 75.1MHz 109.87MHz

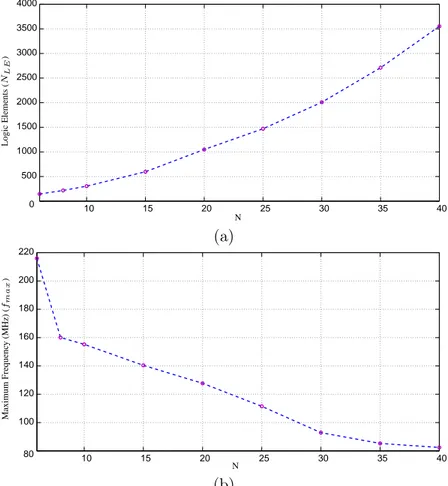

L’implémentation a été faite dans un stratix ii ep2s180f1508c3 et il a été considéré un circuit avec N = 10 saboteurs et P = Z = 32 entrées et sorties. Les résultats de comparaison peuvent être analysés dans le Tableau 3. Les résultats de synthèse de l’outil FIFA sont présentés dans la Figure4.

10 15 20 25 30 35 40 0 500 1000 1500 2000 2500 3000 3500 4000 N L o g ic E le m en ts (N L E ) (a) 10 15 20 25 30 35 40 80 100 120 140 160 180 200 220 N M ax im u m F re q u en cy (M H z) (f m a x ) (b)

Figure4 – Résultats de la synthèse de l’outil (jusqu’à N erreurs simultanées) : (a) nombre d’éléments logiques nécessaires dans le FPGA (b) fréquence maximale d’injection de fautes

Magré la bonne performance de l’outil FIFA, l’analyse de la fiabilité de circuits com-plexes reste très coûteuse en temps. Pour surmonter ce problème, nous proposons d’utiliser la technique de parallélisme. La Figure 5 illustre une architecture parallèle très simple pour l’outil FIFA. Le problème avec cette approche est la grande surface additionnelle qui

GENERATOR 2 DUT REF N DUT FAULTY N STIMULI GENERATOR N

Figure5 – Une simple architecture parallèle pour la FIFA

FAULT GENERATOR 1 MASKING ANALYSIS SUPERVISOR DUT REF STIMULI GENERATOR FAULT GENERATOR 2 DUT FAULTY 1 DUT FAULTY 2 DUT FAULTY N FAULT GENERATOR N

Figure 6 – L’architecture en parallèle proposée pour la FIFA

devient nécessaire à cause de la réplication des modules «stimuli generator», «dut faulty» et «dut ref». En fait, les modules «dut ref» et «dut faulty» répliqués re-quièrent une surface qui peut être significative par rapport à celles des autres modules. Une architecture qui évite la réplication de «dut ref» est illustrée dans la Figure 6. Dans ce cas il est nécessaire de répliquer seulement les modules «dut faulty» et «fault generator».

Afin d’implémenter correctement l’architecture illustrée dans la Figure6, il faut bien distribuer la génération de vecteurs de fautes entre les N modules «fault generator». C’est important de remarquer que la génération de fautes est faite en ordre croissante concernant le nombre de fautes simultanées. En conséquence, il faut développer un al-gorithme pour calculer les vecteurs de fautes qui iront initialiser chaque module «fault generator». Cet algorithme a été developpé en utilisant quelques régularités numériques comme décrit dans le Chapitre 2. Les résultats, présentés dans la Figure 7, prouvent la bonne distribution de la génération de vecteurs de fautes.

Jusqu’à ce point il a été introduit deux méthodes pour analyser la fiabilité d’un circuit numérique. Cette analyse est généralement utilisée pour certifier le fonctionnement correct du circuit pendant sa période de vie utile. Si sa fiabilité ne respecte pas la contrainte de fiabilité minimale, les concepteurs peuvent réaliser le durcissement du circuit.

Générale-1 2 3 4 5 6 7 8 1 1.5 2 2.5 3 3.5 4x 10 4

Number of Parallel Modules (N)

Total Logic Elements

1 2 3 4 5 6 7 8 0 0.5 1 1.5 2 2.5 3 3.5 4x 10 8

Number of Parallel Modules (N)

Number of Clock Cycles

Figure 7 – Performance de l’architecture en parallèle proposée pour la FIFA

ment, la protection partiale d’un circuit contre défaillances est suffisante pour la plupart des applications. Ainsi, le développement des nouvelles méthodes basée sur une procédure de durcissement sélectif devient nécessaire. La troisième contribution de ce travail concerne le développement de deux techniques pour identifier les portes logiques les plus critiques et ainsi permettre de réaliser le durcissement sélectif d’un circuit.

Durcissement Sélectif

Les techniques de durcissement sélectif d’un circuit offrent un bon compromis entre l’augmentation de sa fiabilité et le surcoût correspondant. Ces techniques consistent fonda-mentalement de deux étapes : les portes ou blocs logiques sont analysés et ordonnés selon leur susceptibilité aux fautes et la probabilité que ces fautes produisent une défaillance du système ; ensuite, les portes ou blocs logiques les plus critiques sont protégés en uti-lisant une technique de durcissement choisie par le concepteur. La difficulté de mise en œuvre du durcissement sélectif réside dans l’identification des portes ou blocs logiques les plus critiques pour une application. La première technique proposée dans ce travail consi-dère l’utilisation des résultats produits par un circuit comme le facteur déterminant de la criticité d’un bloc logique.

Évitement des erreurs critiques dans les circuits intégrés

Un problème présent dans la plupart des méthodes de durcissement sélectif est négliger le profil d’utilisation des résultats d’un circuit par l’application cible. En fait, le concept de fiabilité nominale ne prend pas en compte la quantité d’information que chaque bit de sortie contient pour évaluer la fiabilité d’un circuit. Ce fait peut être illustré en considérant 3 architectures d’un circuit additionneur de 4 bits. La fiabilité de chaque bit de sortie (y = b3b2b1b0) de ces 3 architectures est donnée dans le Tableau 4. La fiabilité nominale

2 95% 99% 99% 99% 92.18% 94.17%

3 98% 99% 99% 95% 91.25% 96.64%

peut être calculée selon (10), et les résultats correspondants sont aussi disponibles dans le Tableau 4. Concernant les valeurs pour la fiabilité nominale de ces architectures, un concepteur conclura que les architectures 1 et 2 sont également fiables. Cependant, en analysant la fiabilité de chaque bit de sortie pour ces architectures, il est évident que l’architecture 1 fournit des résultats plus en conformité avec l’application que l’architecture 2. Rnominal= M −1 Y i=0 Ri (10)

Pour faire face à ce problème, ce travail propose le concept de fiabilité pratique. Ba-sée sur le fait que chaque bit de sortie d’un circuit peut avoir une importance différente pour une certaine application, la fiabilité pratique utilise un facteur ki pour déterminer la

sévérité d’une erreur dans un bit de sortie spécifique (voir (11)). Par exemple, dans le cas d’utilisation d’une codification binaire, la valeur de ki est calculée selon (12). Ce concept

corrige le problème décrit par l’exemple du additionneur 4 bits comme illustré dans le Tableau 4 Rpractical= M −1 Y i=0 Rki i (11) ki= 1 2(M −1)−i (12)

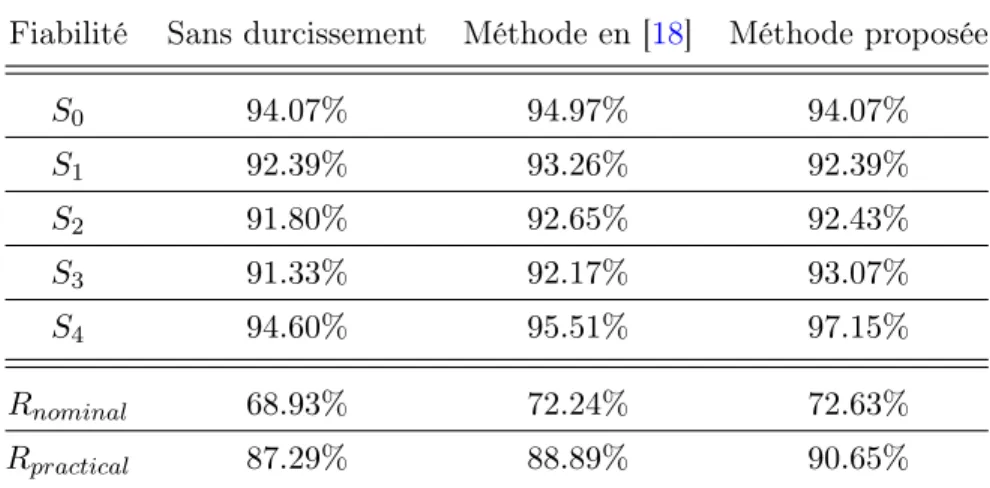

L’utilisation de la fiabilité pratique dans le processus de durcissement sélectif d’un circuit est illustrée avec l’additionneur de 4-bit de la Figure 8. Dans ce cas, la première étape consiste à identifier les portes logiques les plus critiques selon le modèle de fiabilité pratique. Les résultats sont présentés dans le Tableau 5. La méthode [18] a été aussi implémentée et les résultats ont été comparés avec la méthode proposée en considérant la même contrainte de surface (voir Tableau6).

Les résultats présents dans le Tableau 6 prouvent l’efficacité de la méthode proposée. En fait, il peut être noté que le gain en fiabilité est plus marqué pour les bits les plus

significatifs du circuit (les plus critiques). En conséquence, le circuit durcit par la méthode proposée exhibe la plus grande fiabilité pratique.

10 11 9 12 13 14 16 17 18 19 20 22 23 24 25 27 28 29 31 32 36 37 34 35 38 39 0 1 8 33 15 26 21 30 • • 2 3 • • 4 5 • • 6 7 • • • • • • • • • • •• • • • • • • • • • • • • • • • • • • • • • • S 4 C 0 2B 2A 3B 3A A 1 B 1 A 0 B 0 S 3 S 2 S 1 S 0 •

Figure 8 – Schéma en portes logiques du circuit 74283

L’utilisation d’une fonction de coût pour déterminer les portes critiques

La méthode décrite dans les paragraphes précédents ne s’applique pas à toutes les applications. En fait, plusieurs applications ne présentent pas une différence d’importance entre les bits de sortie du circuit. Pour ces applications, ce travail propose aussi une méthode basée sur des fonctions de coût pour automatiser le processus d’identification des portes logiques critiques. Cette méthode utilise le modèle SPR pour évaluer la fiabilité d’un circuit et déterminer les blocs logiques offrant la meilleure relation entre gain en fiabilité et coût. Prenons un circuit composé de K portes logiques [gi· · · gk] pour lesquelles les fiabilités

sont représentées par [qi· · · qk] et la fiabilité total du circuit par R. Donc, en considérant

un gain en fiabilité dans la porte logique gi, la fiabilité total du circuit devient R∗i. Dans ce

cas, deux portes logiques gi et gj peuvent contribuer différemment pour la fiabilité totale

du circuit (R∗

i et R∗j). Il faut définir donc un paramètre pour qu’une fonction de coût puisse

être utilisée. Dans ce travail, nous proposons un paramètre appelé « hardware affinity » (Chai) qui peut être lié à n’importe quelle contrainte du circuit. Par exemple, le Tableau 7

utilise la surface des portes logiques obtenue par une synthèse basée sur la bibliothèque de Synopsis [19]. Il faut noter que le durcissement des portes logiques avec une valeur de Chai plus grande sera prioritaire. Une fonction de coût Ci peut donc être exprimée comme

gi S0 S0w S1 S1w S2 S2w S3 S3w S4 S4w P ew CritF ac 0 0 0 0 0 0 0 384 3072 192 3072 6144 36 1 0 0 0 0 0 0 384 3072 320 5120 8192 38 2 0 0 0 0 384 1536 192 1536 96 1536 4608 33 3 0 0 0 0 384 1536 320 2560 160 2560 6656 37 4 0 0 384 768 192 768 96 768 48 768 3072 25 5 0 0 384 768 320 1280 160 1280 80 1280 4608 32 6 384 384 192 384 96 384 48 384 24 384 1920 14 7 384 384 320 640 160 640 80 640 40 640 2944 23 8 512 512 256 512 128 512 64 512 32 512 2560 22 9 0 0 0 0 0 0 0 0 320 5120 5120 35 10 0 0 0 0 0 0 0 0 288 4608 4608 34 11 0 0 0 0 0 0 0 0 272 4352 4352 31 12 0 0 0 0 0 0 0 0 264 4224 4224 29 13 0 0 0 0 0 0 0 0 272 4352 4352 31 14 0 0 0 0 0 0 512 4096 0 0 4096 27 15 0 0 0 0 0 0 384 3072 0 0 3072 24 16 0 0 0 0 0 0 320 2560 0 0 2560 21 17 0 0 0 0 0 0 288 2304 0 0 2304 20 18 0 0 0 0 0 0 272 2176 0 0 2176 18 19 0 0 0 0 0 0 288 2304 0 0 2304 20 20 0 0 0 0 512 2048 0 0 0 0 2048 17 21 0 0 0 0 384 1536 0 0 0 0 1536 13 22 0 0 0 0 320 1280 0 0 0 0 1280 12 23 0 0 0 0 288 1152 0 0 0 0 1152 10 24 0 0 0 0 320 1280 0 0 0 0 1280 12 25 0 0 512 1024 0 0 0 0 0 0 1024 7 26 0 0 384 768 0 0 0 0 0 0 768 6 27 0 0 320 640 0 0 0 0 0 0 640 4 28 0 0 384 768 0 0 0 0 0 0 768 6 29 512 512 0 0 0 0 0 0 0 0 512 2 30 384 384 0 0 0 0 0 0 0 0 384 0 31 512 512 0 0 0 0 0 0 0 0 512 1 32 0 0 0 0 0 0 0 0 512 8192 8192 39 33 0 0 0 0 0 0 512 4096 0 0 4096 27 34 0 0 0 0 512 2048 0 0 0 0 2048 15 35 0 0 512 1024 0 0 0 0 0 0 1024 8 36 0 0 0 0 0 0 512 4096 0 0 4096 28 37 0 0 0 0 512 2048 0 0 0 0 2048 16 38 0 0 512 1024 0 0 0 0 0 0 1024 9 39 512 512 0 0 0 0 0 0 0 0 512 3

Table6 – Analyse de fiabilité du circuit 74283

Fiabilité Sans durcissement Méthode en [18] Méthode proposée

S0 94.07% 94.97% 94.07% S1 92.39% 93.26% 92.39% S2 91.80% 92.65% 92.43% S3 91.33% 92.17% 93.07% S4 94.60% 95.51% 97.15% Rnominal 68.93% 72.24% 72.63% Rpractical 87.29% 88.89% 90.65% en (13).

Table7 – Paramètre Chai pour quelques cellules logiques

Cellule Surface (µm2 ) Chai INVX0 5.5296 1 NAND2X0 5.5296 1 NOR2X0 5.5296 1 AND2X1 7.3728 0.75 OR4X1 10.1376 0.55 XOR3X1 22.1184 0.25 Rgi = R∗i − R Ci = Rgi/Chai (13)

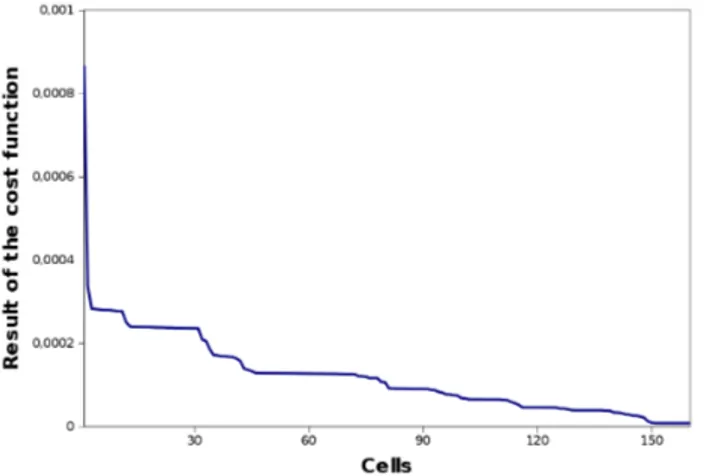

La méthode proposée évalue la fiabilité du circuit et identifie les portes logiques qui seront durcies jusqu’à ce qu’un niveau minimal de fiabilité ‘T’ soit atteint. En utilisant cette méthodologie pour les circuits du benchmark ISCAS [20], deux profils pour la fonction de coût ont été obtenus (voir Figure 9 et10). Le premier présente une décroissance très marquée juste après le début de la courbe, et le deuxième présente la formation des plateaux jusqu’à la fin de l’évaluation.

A partir de ce constat, ce travail propose aussi deux heuristiques pour trouver un point d’arrêt pour la méthode. Le premier est appelé l’heuristique de la somme des éléments et est calculé selon (14). Dans ce cas, C0 représente la valeur de la fonction de coût du

meilleur candidat pour le durcissement, et K est une contrainte empirique choisie par le concepteur. Le deuxième s’appelle l’heuristique basée sur le pourcentage et utilise un point

Figure 9 – Profil de la fonction de coût pour le circuit c432

Figure 10 – Profil de la fonction de coût pour le circuit c499

d’arrêt pour l’algorithme égal à X% du valeur de C0. L’utilisation des deux heuristiques

peut être analysée dans la Figure 11.

j

X

i=2

Ci ≤ K × C0 (14)

Les deux heuristiques ont été utilisées pour réaliser le durcissement de plusieurs circuits du benchmark ISCAS. Les résultats de cette utilisation sont indiqués dans les Tableaux 8

et9.

Le durcissement sélectif peut offrir un bon compromis entre le gain en fiabilité du système et l’ajout de redondance nécessaire. Cela est une caractéristique fondamentale pour la plupart des circuits. Cependant, il y a des applications qui requièrent un niveau de fiabilité très élevé. Pour ces applications un durcissement sélectif peut ne pas être suffisant et l’utilisation de méthodes offrant un niveau de protection plus haut est intéressante, même au pris d’un surcoût significatif de surface. La quatrième contribution de ce travail

Table 8 – Résultats pour l’heuristique de la somme des éléments, K = 10

Circuit Nombre Surface Portes Surface Surcoût

de portes original (µm2 ) durcit durcit (µm2 ) en surface c17 6 33.1776 6 99.5328 200% 74283 40 306.5096 20 547.9688 78.7% c432 160 1134.4672 33 1541.4208 35.8% c499 202 2155.1680 12 2414.1504 12.0% c1355 546 3194.7328 11 3316.3840 3.8% c1908 880 5273.7488 13 5417.5184 2.7% c2670 1269 8018.0632 19 8233.7176 2.6% c3540 1669 10855.1824 25 11177.7424 2.9% c5315 2307 15293.5992 20 15518.4696 1.4%

Table9 – Résultats pour l’heuristique basée sur la pourcentage, X = 50%

Circuit Nombre Surface Portes Suface Surcoût

de portes original (µm2 ) durcit durcit (µm2 ) en surface c17 6 33.1776 5 88.4736 166.6% 74283 40 306.5096 9 406.0424 32.5% c432 160 1134.4672 2 1187.5264 4.6% c499 202 2155.1680 41 2854.6752 32.4% c1355 546 3194.7328 201 5647.1232 76.7% c1908 880 5273.7488 119 6611.912 25.3% c2670 1269 8018.0632 10 8128.6552 1.4% c3540 1669 10855.1824 8 10963.9312 1.2% c5315 2307 15293.5992 15 15459.4872 1.1%

heuristic

Figure 11 – L’utilisation des deux heuristiques dans le circuit c1355

est une méthode pour optimiser la procédure de partitionnement d’un circuit TMR de telle façon que un niveau de fiabilité très élevé soit assuré.

Optimisation du placement des arbitres dans un circuit TMR

La méthode TMR est souvent utilisée pour réaliser le durcissement d’un circuit intégré. L’idée générale est très simple : trois répliques du circuit fournissent les résultats pour un arbitre qui juge quel est la sortie exacte en utilisant normalement le critère de majorité (voir Figure 12). Dans ce cas, même avec la présence d’une erreur dans la sortie d’un module, l’arbitre peut fournir la sortie exacte. Donc, la fiabilité totale du circuit initial (Rm) devient Rcir comme illustré dans (15).

Module

Module

Module

Majority

Input Output

Figure 12 – Schéma en blocs de la méthode TMR

Rcir = R3m+ 3R2m(1 − Rm)

Rcir = 3R2m− 2R3m (15)

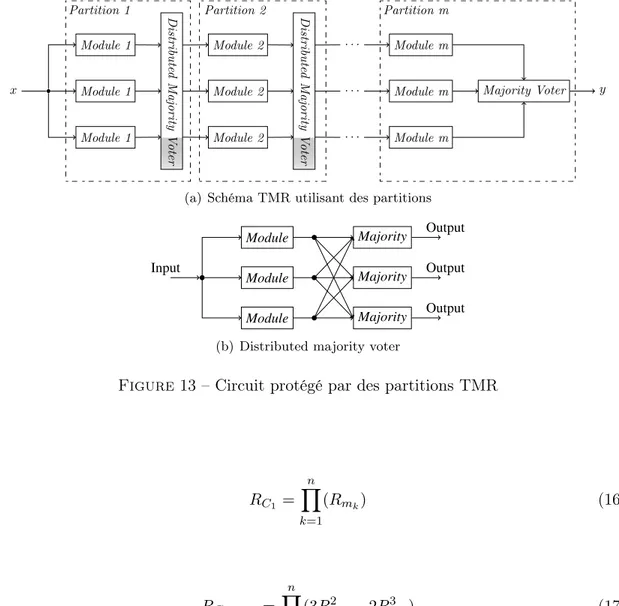

En dépit de sa simplicité, la méthode TMR offre un bon niveau de protection contre défaillances. Si une application requiert un niveau de fiabilité plus élevé que celui fourni par le TMR, il est possible de réaliser un partitionnement du circuit de telle façon qu’il soit composé par ‘m’ modules et sa fiabilité soit donnée par (16). En considérant que

chaque module est protégé par TMR (voir Figure 13), la fiabilité total du circuit peut être déterminée selon (17).

Module 1 Module 2 · · · Module m

x Module 1 Di st ri bu te d M a jo ri ty V o ter Module 2 Di st ri bu te d M a jo ri ty V o ter

· · · Module m Majority Voter y

Module 1 Module 2 · · · Module m Partition 1 Partition 2 Partition m

(a) Schéma TMR utilisant des partitions Module Module Module Majority Majority Majority Input Output Output Output (b) Distributed majority voter

Figure 13 – Circuit protégé par des partitions TMR

RC1 = n Y k=1 (Rmk) (16) RC1T MR = n Y k=1 (3R2mk− 2Rm3k) (17)

L’approche de partitionnement d’un circuit TMR peut offrir un niveau très élevé de fiabilité qui dépend de deux facteurs principaux : la quantité ‘n’ des modules et le placement des arbitres pour ces modules. Donc, une question qui devient intéressante est comment déterminer ces deux facteurs d’une façon optimale pour qu’un niveau de fiabilité minimale Rmin soit atteint.

Ce problème peut être divisé en deux parties. En considérant une quantité ‘n’ de par-titions, il faut évaluer la valeur de la fiabilité de chaque module Rmk pour que la fiabilité

totale RC1T MR soit maximisée. Cela peut être obtenu avec la méthode des multiplicateurs

ci-après : ∂ ∂Rm1g = (6Rm1− 6R 2 m1) Qn k=2(3R 2 mk− 2R 3 mk) − λ Qn k=2(Rmk) = 0 ∂ ∂Rm2g = (6Rm2− 6R 2 m2)(3R 2 m1− 2R 3 m1) Qn k=3(3R 2 mk− 2R 3 mk) − λRm1 Qn k=3(Rmk) = 0 ∂ ∂Rm3g = (6Rm3− 6R 2 m3) Q2 k=1(3R 2 mk− 2R 3 mk) Qn k=4(3R 2 mk− 2R 3 mk) − λRm1Rm2 Qn k=4(Rmk) = 0 .. . ... ... ... ... ∂ ∂Rmng = (6Rmn− 6R 2 mn) Qn−1 k=1(3R 2 mk− 2R 3 mk) − λ Qn−1 k=1(Rmk) = 0

Par inspection, il peut être déterminé qu’une solution qui maximise la valeur de RC1T MR

en considérant l’utilisation de ‘n’ modules est Rm1 = Rm2 = · · · = Rmn = R 1/n

C1 .

C’est-à-dire, le circuit doit être partitionné en modules de fiabilités aussi identiques que possible. En utilisant ce résultat, l’équation (17) devient (19). De plus, ce résultat permet l’évaluation du nombre de modules ‘n’ qui doivent être utilisés pour qu’un niveau de fiabilité minimale Rmin soit atteint.

RC1T MR = (3R2/nC1 − 2R 3/n C1 )

n (19)

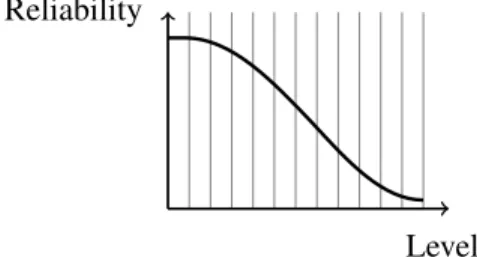

La littérature ne reporte pas l’existence d’outils permettant la mise en œuvre automa-tique de la procédure de partitionnement d’un circuit TMR. Pour faire face à ce problème, nous proposons une méthode basée sur une idée très simple. D’abord, il faut visualiser l’évolution de la fiabilité du signal par rapport aux niveaux logiques comme illustré dans la Figure 14. Dans ce cas, un niveau logique est défini comme un nœud qui présente la capacité de devenir la frontière d’un module.

Si un arbitre est inséré dans un niveau aléatoire d’un circuit, une augmentation de la fiabilité est attendue dans ce même niveau (voir Figure 15). En fait, le gain en fiabilité est obtenu à cause de la capacité que possède l’arbitre de corriger des erreurs simples.

C’est bien connu que le gain en fiabilité obtenu par l’utilisation de la méthode TMR dépend de la fiabilité du module Rm comme illustré par (15). En même temps, la réduction

de la fiabilité du signal illustrée dans la Figure14 est aussi proportionnelle à Rm. Donc,

Reliability

Levels

Figure 14 – Comportement de la fiabilité du signal d’un circuit par rapport aux nombre de niveaux

Reliability

Levels Majority Voter

Figure 15 – L’insertion d’un arbitre dans un niveau aléatoire du circuit

blocs logiques de fiabilités aussi égales que possible. Cela est la première conclusion pour obtenir une solution optimale. Si ce seuil est défini par la fiabilité minimale du circuit, le résultat sera un nombre des modules ‘n’ très proche de la valeur optimale. Cette procédure est illustrée dans la Figure16.

Reliability

Levels

Reliability

Requirement(Rmin) Level 5 Level 9 Level 12

Figure16 – Circuit TMR utilisant une distribution du processus de vote

Ce résultat peut être mieux analysé en considérant un circuit simple comprenant 10000 inverseurs logiques identiques (même fiabilité Rm= 99.99%) connectés dans une structure

en cascade (voir Figure17).

La fiabilité totale du circuit Rc peut être évaluée à l’aide de l’outil SPR (Rc =

méthode proposée insère 1000 arbitres. Tous les modules ont la même quantité de compo-sants (N=10) sauf le premier (N=11) et le dernier (N=9). Il résulte de (19) que la quantité minimale de modules pour attendre le valeur de Rmin est égal à 961. Cependant, cela

vou-drais dire que chaque partition devrait avoir 10.4058 inverseurs ce qui est impossible. La solution la plus proche possible sera l’utilisation de 10 inverseurs par module, ce qui cor-respond à la quantité de 1000 arbitres insérés, la même obtenue par la méthode proposée. La Figure 18 illustre le comportement de la méthode proposée en considérant plusieurs valeurs de Rmin. Il peut être observé que les résultats sont proches des résultats optimaux

pour tous les valeurs de Rmin considérés.

0,99 0,991 0,992 0,993 0,994 0,995 0,996 0,997 0,998 0,999 1 0 100 200 300 400 500 600 700 800 900 1000 R min Number of Voters Optimal Result Proposed Method

Figure 18 – Nombre d’arbitres insérés par la méthode proposée

Conclusion

Avec l’évolution technologique, la fiabilité joue un rôle de plus en plus important dans la conception des circuits intégrés. L’analyse de fiabilité doit être utilisée dans le flot de conception du circuit pour identifier le besoin d’utilisation des techniques de durcissement. Dans la littérature il y a plusieurs techniques d’analyse et de durcissement d’un circuit intégré. Cependant, ces téchinques présentent des limitations du fait de la complexité

d’analyse. En conséquence, le développement des nouvelles méthodes d’analyse aussi bien que des techniques de durcissement deviennent nécessaires. Dans cette thèse, plusieurs méthodes et outils d’analyse et durcissement ont été proposés.

Concernant l’analyse de fiabilité, la métrique mathématique «effective reliability» per-met la prise en considération de la tolérance aux erreurs de l’application cible pour évaluer la fiabilité du circuit, alors que l’outil FIFA a été développé pour accélérer le processus d’analyse de fiabilité basée sur l’injection de fautes.

Dans le domaine de durcissement d’un circuit, deux techniques ont été développées pour identifier les portes logiques les plus critiques d’un circuit. Cela est une étape fondamentale pour l’application d’un processus de durcissement sélectif. Pour les applications qui ont besoin d’un niveau de fiabilité très élevé, un méthode automatique de partitionnement d’un circuit TMR a été élaborée. La performance optimale de cette méthode a été prouvée mathématiquement aussi bien que par simulation.

Symbols and Abbreviations

q Gate reliability 1 − q Gate unreliability qi Reliability of bit i

λ, λ(t) Failure rate

Chai Hardening affinity parameter

R(t), ˆR(t) Reliability function Ri Reliability of bit i

u(t) Step function

Rack Probability of errors being masked according to the application

Rnom Nominal reliability

Ref f Effective reliability

Rpractical Practical reliability

ALM Adaptive logic module

ASMBL Advanced silicon modular block AUED All-unidirectional error detecting code BUED Burst unidirectional error detecing code CCC Clock conditioning circuit

CD Code distance

CLB Configurable logic block

CMOS Complementary metal-oxide-semiconductor CMT Clock management tile

DCM Digital clock management DMA Direct memory access

DRAM Dynamic random-access memory DUT Device under test

ECC Error correcting code EDC Error detecting code EDF Électricité de France

EEPROM Electrically erasable programmable read-only memory EMI Electromagnetic interference

EPROM Erasable programmable read only memory

FA Full Adder

FIT Failures in time

FPGA Field-programmable gate array HALT Highly accelerated life test HD Hamming distance

IEC, CEI International electrotechnical commission IP Intellectual property

ITM Ideal transfer matrix

ITRS International technology roadmap for semiconductors JEDEC Joint electron devices engineering council

JTAG Joint test action group LAB Logic array block

LE Logic element

LET Linear energy transfer LSB Least significant bit LUT Look-up table MBU Multiple-bit upset MCU Multiple-cell upset

MOSFET Metal-oxide-semiconductor field-effect transistor MSB Most significant bit

MTBF Mean-time-between-failures MTTF Mean-time-to-failure NMR N-modular redundancy OTP One time programmable

PBR Probabilistic binomial reliability model PIP Programmable interconnect point PLL Phase-locked loop

PTM Probabilistic transfer matrix RAM Random-access memory RTL Register transfer level SBD Soft breakdown

SEU Single-event upset

SPICE Simulation program with integrated circuit emphasis SPR Signal probability reliability model

SPR-MP SPR multi-path model

SRAM Static random-access memory STMR Selective triple modular redundancy TMR Triple modular redundancy

TSC Totally self-checking

t-UED t-unidirectional error detecting code ULA Ultra-low alpha

VHDL Very high speed integrated circuit hardware description language VLSI Very-large-scale integration

Contents

Introduction 44

1 Background on Reliability 51

1.1 Introduction . . . 51

1.2 Reliability analysis . . . 51

1.2.1 Faults in VLSI circuits . . . 55

1.2.2 Reliability issues in FPGAs . . . 59

1.2.3 Prior works on reliability analysis . . . 62

1.3 Reliability improvement of integrated circuits . . . 68

1.3.1 Modular redundancy . . . 68 1.3.2 Voting strategies . . . 71 1.3.3 Selective Hardening . . . 72 2 FIFA Tool 75 2.1 Introduction . . . 75 2.2 FIFA Tool . . . 75 2.2.1 FIFA Architecture . . . 77 2.2.2 Reliability Assessment . . . 81 2.2.3 Synthesis Results . . . 82

2.2.4 Parallelizing the FIFA Fault Generation . . . 84

2.2.5 Results . . . 88 2.2.6 Conclusion . . . 89 3 Effective Reliability 91 3.1 Introduction . . . 91 3.2 Error tolerance . . . 92 3.3 Effective reliability . . . 94 3.4 Quality metrics . . . 95 3.4.1 Definitions . . . 95

3.4.2 Quality metric 1: bit significance . . . 96

3.4.3 Quality metric 2: relative error . . . 97

3.5 Simulation results . . . 98

3.5.1 Median filter . . . 98

3.5.2 8-bit ripple carry adder . . . 100

3.5.3 4-bit multiplier . . . 102

3.6 Conclusion. . . 104

4 Selective Hardening 107

4.1 Introduction . . . 107

4.2 Avoiding Critical Errors in Integrated Circuits . . . 107

4.2.1 Nominal reliability . . . 107

4.2.2 Practical reliability . . . 108

4.2.3 Selectively applying TMR . . . 109

4.3 Using a Cost Function to Detect Critical Gates . . . 114

4.3.1 Cost function profiling . . . 116

4.3.2 Experimental results . . . 119

4.3.3 Comparison with related works . . . 120

4.4 Conclusion. . . 121

5 Optimizing Voter Placement for TMR Systems 123

5.1 Introduction . . . 123

5.2 TMR approach . . . 123

5.3 Partitioning a TMR design . . . 125

5.4 Problem of automatically inserting voters . . . 128

5.5 Proposed method . . . 129

5.6 Conclusion. . . 134

6 Concluding Remarks 135

A Other Methods for Reliability Improvement of ICs 139

A.1 Fault detection and correction . . . 139

A.1.1 Basic principles . . . 139

A.1.2 Fault detection techniques . . . 140

A.2 Evolvable hardware . . . 149

B Basics on FPGAs 153

B.1 FPGA technologies . . . 153

B.2.1 Altera . . . 159 B.2.2 Xilinx . . . 162 B.2.3 Actel . . . 165 B.2.4 Lattice. . . 167 Conclusion 169 Glossary 171 Notations 171 Bibliography 184

List of Figures

1.1 Number of functioning parts of a circuit at time t . . . 53

1.2 Bathtub curve. . . 54

1.3 Residue induced intermittent fault in a DRAM chip. . . 57

1.4 Effects of a high-energy ion hitting a semiconductor device . . . 58

1.5 Fault simulation approach proposed by Ogus . . . 63

1.6 PTM representation for an AND gate . . . 64

1.7 Basic interconnection models of PTM . . . 64

1.8 SPR matrix for the output of a 2-input OR gate . . . 65

1.9 Propagation of the SPR matrices through a circuit . . . 65

1.10 TMR concept envisaged by Von Neumann . . . 69

1.11 TMR performance regarding reliability improvement . . . 69

1.12 TMR with three majority voters . . . 70

1.13 Word-Voter proposed in [21] . . . 71

2.1 General scheme of the proposed tool . . . 78

2.2 General scheme of a saboteur . . . 78

2.3 FIFA Timing diagram of communication signals . . . 80

2.4 Example of a step by step execution of Algorithm 1 . . . 81

2.5 Synthesis results of the FIFA tool . . . 83

2.6 A simple parallel architecture for FIFA . . . 85

2.7 The proposed parallel architecture for FIFA . . . 85

2.8 Example of a fault pattern generation sequence . . . 86

2.9 Pascal’s triangle. . . 87

2.10 Total logic elements . . . 89

2.11 Number of clock cycles . . . 89

3.1 Example of a logical masking . . . 92

3.2 Bit-flip occurrence in a sine wave . . . 93

3.4 Example of matrix E considering 3 errors . . . 96

3.5 Comparison between the original and the noisy “Lena” pictures . . . 100

3.6 Structure of FA (full adder) block . . . 101

3.7 Schema of FA block . . . 101

3.8 Structure of a 4-bit multiplier block. . . 103

4.1 4-bit fast adder circuit . . . 110

4.2 74283 gate-level schematic . . . 111

4.3 Simulation results for the 74283 circuit . . . 114

4.4 Cost function profile for the circuit c432 . . . 117

4.5 Cost function profile for the circuit c499 . . . 118

4.6 Both heuristics applied to the circuit c1355 . . . 118

5.1 TMR block scheme . . . 123

5.2 Reliability gain using TMR . . . 124

5.3 Partitioning a TMR design . . . 125

5.4 C1 comprises n modules serially interconnected . . . 126

5.5 Plot of Rm1 =

RC1

Rm2 for different values of RC1 . . . 127

5.6 Reliability of a circuit versus its number of levels . . . 129

5.7 Insertion of a majority voter . . . 130

5.8 Distributing the voting process of a TMR circuit . . . 130

5.9 Cascade of inverters . . . 131

5.10 Number of voters inserted by the proposed technique . . . 131

5.11 Circuit 74283 - Gate level . . . 132

A.1 Example of a duplex comparison scheme . . . 139

A.2 Computer memory using parity checking . . . 141

B.1 Programmable circuit concept . . . 154

B.2 Programmable circuit with intact fusible links . . . 154

B.3 Programmed circuit with output Y = A + ¯B . . . 154

B.4 Programmable circuit with intact antifuses . . . 155

B.5 Programmed circuit with output Y = A + ¯B . . . 155

B.6 Static Memory Cell . . . 157

B.7 Flash memory cell - ProASIC3 . . . 158

B.8 ALM High-Level Block Diagram . . . 160

B.9 LE Block Diagram . . . 161

B.10 Example of devices using the ASMBL architecture . . . 163

List of Tables

1.1 Programming technology properties summary . . . 60

2.1 Fuse platform vs. FIFA tool . . . 84

3.1 Effective reliability evaluation for different error tolerances . . . 99

3.2 Reliability values for the output bits of a full adder . . . 101

3.3 Reff for different error tolerances (CRA8). . . 102

3.4 Reliability values for each output bit of the 4-bit multiplier . . . 103

3.5 Reff for different error tolerances (MUL4) . . . 104

4.1 Reliability values of three different architectures of an adder . . . 108

4.2 Error analysis for the gates of the circuit 74283 . . . 112

4.3 Reliability Analysis of 74283 . . . 113

4.4 Hardware affinity (Chai) parameters for some cells . . . 116

4.5 Results for the sum of elements heuristic, K = 10 . . . 119

4.6 Results for the percent wise heuristic, X = 50% . . . 120

5.1 Placement of the voters for the circuit 74283. . . 133

5.2 Reliability of gates based on their area . . . 133

5.3 Placement of the voters for the 74283 circuit. . . 134

A.1 3-bit Berger code – B0 scheme. . . 142

A.2 Bose code for data words comprising 4 bits . . . 143

A.3 Syndrome Table for Hamming (7,4) code . . . 147

B.1 Programming technology properties summary . . . 159

B.2 Altera Devices Comparison . . . 162

B.3 Xilinx Devices Comparison . . . 164

B.4 Actel Devices Comparison . . . 167

Introduction

The first electronic computer was built in Antanasoff’s Iowa State College in 1942 [22] and used rather unreliable components. Improve the system reliability was a major concern and techniques such as duplexing with comparison, triplication with voting, control codes, among others, were proposed. Indeed, important researches were done by J. Von Neumann, E. F. Moore and C. E. Shannon using redundancy as a mean to build reliable systems from less reliable components [23,24].

Since then, the integrated circuit technology has underwent an exponential evolution as predicted by the Moore’s law [1,2]. Nowadays devices are shrinking into the deca-nanometer range, allowing the fabrication of chips containing billions of transistors, and operating at very high speeds (multiple GHz). In such scale, new physical phenomena, such as Van Der Waals and Casimir forces, appear leading to new fabrication methodologies and affecting the components reliability [3]. Further, interconnect systems are becoming very complex, particularly with the introduction of the 3-D die integration scheme [4]. In fact, the higher density of integrated circuits together with the higher complexity of the interconnections lead to a higher probability of erroneous components in a die. Meanwhile, the higher frequencies pose strict limits to timing, thus also increasing the probability of timing errors [5]. In other words, a reduction in manufacturing yield is expected, as well as in the overall circuit reliability [6–10].

Consequently, faults have become more and more likely to occur in deep-submicron technologies. Permanent faults can be significantly reduced by performing deep investi-gations during offline testing [25]. On contrary to that, transient faults depend on envi-ronmental conditions, and therefore they randomly occur during circuit operation. In the past, these faults used to be a concern only on the design of memories. However, the tech-nology scaling has increased the susceptibility of combinational blocks to thermal bit-flips, radiation events, among others, so that their resulting error rates are approaching those of memories [26,27]. This is a serious menace to circuits designed to operate under critical environments such as nuclear power plants, avionics, among others, and therefore solutions to construct fault-tolerant circuits are necessary.

Paristech. The motivations for this work can be explained as follows. EDF is one of the world’s largest producers of electricity with main activity in nuclear power. EDF’s control-command systems are based on electronics devices/circuits. Nuclear power plants consider safety as a very high priority in their systems, and electronic circuits must be in accordance to several technical standards such as the IEC 62566 [11], the IEC 60987 [12], and the IEC 61513 [13] in order to be qualified to operate in such critical environments. Particularly, the use of programmable devices poses a great challenge to be qualified since the functionality of the IC is not defined by the founder of the physical component, but by the designer of the application. Further, the technical standard IEC 62566 states that the benefits accomplished by the use of redundancy in an electronic circuit must be balanced with the corresponding increase in the system complexity as well as in the fault coverage. Because of that, methods to analyze and to improve the reliability of electronic circuits to be used in nuclear power plants are a major concern.

The main objective of the current work is to propose methods to analyze and to im-prove the reliability of circuits in order to facilitate their qualification according to the aforementioned technical standards. Therefore, different strategies that allows both to achieve a very high level of reliability in a circuit and to control the amount of redundancy adding are required. These methods must be developed in such a way that they can be used to construct circuits using programmable devices as well as for circuits tailored for a specific function, e.g. ASICs. Also, the proposed solutions must be able to be appended to traditional design flows of integrated circuits.

A fault-tolerant integrated circuit is generally obtained by the properly use of redun-dancy, whether it be temporal or spatial. The addition of redunredun-dancy, however, directly affects some attributes of the circuit, such as performance and surface, thus increasing the overall system cost and complexity. Because of that, the choice of which fault tolerant approach to use for a given scenario involves a multi-criteria optimization problem, taking into account all the specified design constraints. Therefore, whether a circuit is intended to mission critical applications or in the case reliability can be relaxed in order to avoid the increase in the complexity of the circuit, reliability analysis plays a crucial role in its design flow. Methodologies to assess the reliability of circuits have been extensively researched over the last years. As a matter of fact, an optimal reliability analysis lies on the use of as much information as possible about the circuit itself as well as about the target appli-cation. However, most of the existing techniques assume simplifications on mathematical models such as single faults, uncorrelated signals, among others. Further, not much has been done in order to consider the usage profile of the circuits’ results when calculating its reliability. In spite of that, many applications exhibit the ability to tolerate some kinds of errors. By considering such ability, a designer can obtain more accurate results, which can

critical errors. In this case, an error is said to be non-critical if it can be tolerated by the target application. Two possible quality metrics are also proposed in the current work.

Effective reliability is of great use for applications in which some errors can be tolerated. However, mission critical applications demand a high-degree of confidence, and they have low or no interest in accepting any kind of error. Indeed, these circuits usually require deep investigations to predict its behavior considering the occurrence of faults, so that the reliability of its results can be asserted. Generally, such circuits demand a test coverage approaching 100%, and therefore methods to accelerate exhaustive testing are necessary.

In order to cope with this problem, this work also proposes a Verilog-based platform to exhaustively analyze the behavior of a logical circuit considering the occurrence of faults. The proposed platform, named FIFA (Fault-Injection-Fault-Analysis), is based on the Probabilistic Binomial Reliability model (PBR), which can evaluate the reliability of a circuit based on its logical masking ability. One of the great advantages of the FIFA platform is that it is easily customized. Further, it supports several fault models as well as the ability to inject single and multiple simultaneous faults. It is important to highlight that the fault pattern generation as well as the fault injection can be performed without the need of any device reconfiguration. Also, the proposed platform allows the evaluation of approximated reliability values by considering a maximum number of simultaneous faults to be injected. In order to allow that, the platform generates the fault patterns in an ascending order regarding the number of simultaneous faults. The flip side of the coin is that such fault pattern generation sequence imposes strict difficulties to be parallelized. In order to address this problem, the current work also proposes a solution based on number patterns to elaborate a parallel design for the FIFA platform, which can significantly reduce the required computing time.

Although reliability analysis plays an important role during the design phase of an integrated circuit, methods to improve its reliability are more and more desired in deep-submicron technologies. Partial fault tolerant designs are usually enough for some appli-cations, and therefore methods based on selective hardening are very suitable.

Based on that fact, this work proposes two methods to identify the critical gates of a circuit in order to apply selective hardening. The first one is based on the criticality of the output bits regarding the usage profile of the results. In other words, it drives the reliability improvement effort to better protect the output bits that are considered more critical to

the target application. By doing that, the proposed methodology can automatically select a set of gates, based on an area overhead constraint, such that the probability of occurrence of critical errors is minimized. The second one uses a parameter similar to a hardening cost in order to drive the methodology using accurate cost values for hardening each gate. In addition, two heuristics are introduced as a means to determine when selective hardening is no longer feasible.

Although partial fault tolerance techniques are good solutions for some applications, this is not the case for mission critical ones. Indeed, most of the time such applications demand the most reliable system possible. In such context, Triple Modular Redundancy (TMR) is a fault-tolerant technique often used despite its huge area overhead. This is because TMR has proven to be a very simple, effective solution to the correction of single faults. Further, several tools were developed in order to automatically apply TMR to a circuit, which simplifies the whole process of circuit hardening. However, as the dimensions of integrated circuits continue to shrink, the probability of occurrence of MBUs increases as well. Therefore, methods that can deal with multiple simultaneous faults are highly desired.

One possible solution to that is the use of other modular redundancy techniques such as 5MR, 7MR, etc., but the area overhead is generally prohibitive. On the other hand, the heart of TMR is the majority voter block, responsible to mask the faults occurring in the circuit. Indeed, this block can correct any single fault or detect any double faults occurring in the circuit. Delegate the majority decision to several modules across the circuit has been proved to be a great cost-effective solution to correct multiple simultaneous faults. This technique, known as partitioned TMR, can increase the fault tolerance of a traditional TMR system by slightly increasing the corresponding area overhead. However, determine the number of majority voters to be used and their corresponding placements are not trivial tasks. Indeed, the voter insertion process directly affects the timing performance, the area, and the reliability of the obtained circuit. This problem is yet more complicated in case of FPGAs because certain nets are not allowed to be cut by voters, or this is not desirable.

Finally, the current work proposes an algorithm to tackle this problem. Given a reli-ability requirement, the proposed algorithm can automatically detect the best amount of voters as well as their placements in order to partition a TMR design. Further, the reliabil-ity gains achieved by the proposed method approach those obtained with an optimal TMR partitioning. Indeed, by using this method, only the first and last partitions do not always have optimal sizes. Last but not least, the method was developed in order to be applied in both VLSI and FPGA circuits by analyzing gate and primitive netlists, respectively.

The current work is organized as follows. First, some basics on reliability analysis and reliability improvement techniques are presented in Chapter1. Next, Chapter2introduces

presents a technique to automatically insert partitioning voters into a TMR design. Finally, a review of other methods existent in the literature to improve the reliability of a circuit is presented in Appendix A, and a review of some popular technologies and architectures of FPGAs is available in Appendix B.

Chapter 1

Background on Reliability

1.1

Introduction

Until the sixties, the consumer expectation when buying something was to receive a product that performed well its functionality at the time it left the manufacturer. This expectation evolved over the years, and the product bought today must perform the re-quired function free of failures for a specified period of time [28]. This brings the concept of reliability of a product, which can be defined as the probability of a given item to perform its required function under stated conditions for a stated time interval [14].

Since then, reliability has become a very important attribute for most of industrial products. In case of electronic circuits, reliability is a main consideration when designing nanoscale devices. Indeed, factors associated to technology scaling such as manufactur-ing precision limitations, devices parametric variations, supply voltage reduction, among others, are increasing the likelihood of faults in electronic circuits, thus decreasing their reliabilities. Therefore, methods that can analyze the reliability of a circuit in order to provide feedback for the elaboration of robust designs are highly desired.

This chapter presents some basics on reliability. First, Section 1.2 introduces some important concepts on reliability prediction. Next, techniques to improve the reliability of a circuit based on modular redundacy are discussed in Section 1.3.

1.2

Reliability analysis

An electronic circuit is composed of a set of electronic components interconnected in such a way that a given functionality, described by a circuit specification, is provided. Assuming that a circuit is well specified and that it contains only fault-free elements, the desired functionality can be always guaranteed. However, electronic devices are susceptible to some natural and human-made mechanisms, e.g. impurities in materials, device

param-eters variations, errors in the specification of a circuit, among others, which can affect the state of individual electronic components. These mechanisms, here called faults, are of great importance for reliability engineering because they are responsible for the occurrence of errors in electronic circuits. However, not every error will succeed to propagate to the output of a circuit and then affect the final results. As a matter of fact, the propagation of errors depends on the interaction among the electronic components of a design. If an error succeeds to reach the final output of a circuit, it will lead to the occurrence of results that are not in accordance with the circuit specification, also know as failures. Otherwise, it is said that the error was masked. This abnormal behavior is becoming more and more likely to happen with the downscaling of electronics. Because of that, reliability analysis has become an important step on the design flow of integrated circuits.

Reliability analysis can be performed in several phases of the circuit development. How-ever, the most effective way is to perform the analysis while still on its design phase [29,30]. This is because the correction of a design can be performed before physically fabricating it, thus reducing the time-to-market and the cost of the circuit in case of the validation process fails. In order to do that, it is important to deeply understand the possible causes of failures, so that they can be anticipated and prevented. Therefore, one of the most common forms of reliability analysis is the reliability prediction. It refers to the estimation of the failure rate of electronic components and of the overall system. This prediction contributes to define the initial, maintenance and total system costs, for example. By pre-dicting the reliability of a circuit, designers can evaluate the feasibility of a given design, revealing potential failure areas and the need for environmental control systems. They can also determine the need of redundant systems, back-up systems, among others. Fur-ther, reliability analysis can be used as a tool to compare the performance of different fault-tolerant strategies, measuring the reliability improvement achieved by using a given technique and the corresponding overhead in terms of area and/or timing [31].

In order to estimate the failure rate of a given circuit, let us first assume that it is composed of n statistical identical and independent parts that were put into operation at time t = 0. Then, the number of parts of this circuit that did not yet fail at time t can be represented by a continuous decreasing step function u(t) as shown in Figure1.1. Based on this curve, the empirical reliability of a circuit can be obtained by (1.1). A direct application of the law of large numbers (n → ∞) yields that ˆR(t) converges to the reliability function R(t) [28].

ˆ

R(t) = u(t)

n (1.1)