ETUDE ET SIMULATION D'UN BLOC DE CALCUL

par Cayrol Géraud.

Centre de calcul Université McGill Montréal-Canada Août 19670

ETUDE ET SIMULATION D'UN BLOC DE CALCUL

par Cayrol Géraud.

Centre de calcul Université McGill Montréal-Canada "-Aout 1967.

cv

Cayrol Géraud 1968RESUME

Ce compte rendu comporte l'étude d'une unité

arithmétique, à partir de données fbcées à priori. L'utilité et les particularités de chaque él~ment sont justifiées au cours de l'étude,dans trois

parties essentielles: le décodage de l'instruction, l'eJcécution des opérations logiques élémentaires, et l'eJcécution des opérations :J.rithmétiques d'abord avec des entiers, puis en virgule flottante. Le blGlc de calcul une fois défini est simulé en MAPo

D'autre part, considérant ce bloc de calcul comme un élément d'une machine disposant de plusi-eurs processplusi-eurs et d'une mémoire multimodulaire, une étude statistique des parturbations en mémoire et des queues ~ventuelles est éffectu~eo La pro-grammation est en GPSSo

REMERClMENTS

L'auteur tient à remercier Monsieur le Directeur WoD. Thorpe et tous les professeurs du centre de calcul.

D'autre part il a beaucoup appr~cié la coop-ération de tous les membres du centre, et en particulier de Mlle Carol Schaefer qui a contri-bué à la présentation finale du compte rendu.

Il eJcprime enfin, sa reconnaissance pour l'attribution d'une bourse d'études IBM, qui a rendu possible ce travailo

Pr~sentation Resum~

Remerciments

TABLE DES MATIERES

iiii

i

Table des mati~res

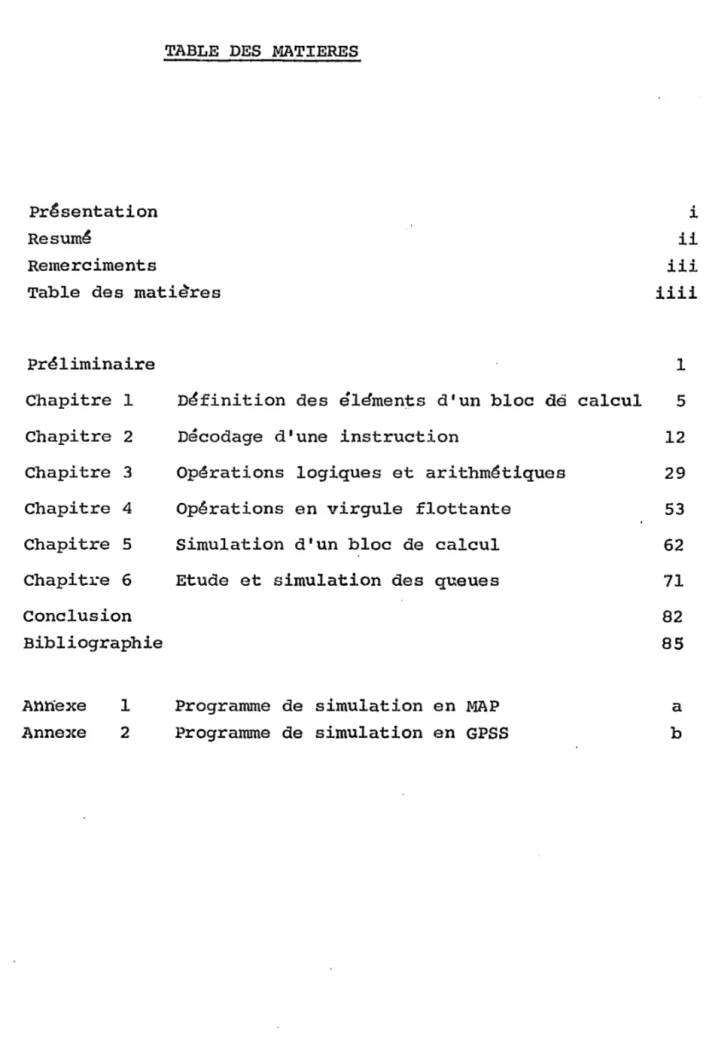

ii iii iiii Pr~liminaire Chapitre l Chapitre 2 Chapitre 3 Chapitre 4 Chapitre 5 Chapitre 6 Conclusion Bibliographie Annexe AnneJce l 2 l

D~finition des éléments d'un bloc dè calcul 5 Décodage d'une instruction 12 Opérations logiques et arithm~tiques 29 Opérations en virgule flottante 53 Simulation d'un bloc de calcul 62 Etude et simulation des queues

Programme de simulation en MAP Programme de simulation en GPSS 71 82 85 a b

PRELIMINAIRE

Cet exposé se base sur un compte rendu. . fait l'an dernier en France, au centre de calcul de la Facult4 des Sciences de Toulouse (par Mr. Lelann et l'auteur, sous la direction de Mr. H. Boucher). dans le cadre du diplome de fin d'Etudes de l'Ecole Nationale Supérieure d'Ingénieurs.

Il va consister d'une part en la simulation d'une unit~ arithm~tique pour en définir toutes les carac-téristiques et aboutir à en tracer un shéma général. D'autre part il comporte une étude statistique des gênes en mémoire dans le cadre d'une machine à plu-sieurs processeurs et la simulation des queues éven-tuelles en GPSS.

Dans l'étude de l'an dernier il s' agiss:dt de con-cevoir les caractéristiques d'une nouvelle calculatrice d'une facon trés généramd'abord, puis plus particu-lièrement dans l'étude d'un bloc de calcul:

1. Cette machine a été définie comme étant bi-naire( synchrone et à "mots". Sa logique est microprogramm~e et elle est essentielle-ment constituée de plusieurs blocs de calcul

(processeurs) et d'une mémoire modulaire: par exemple 4 blocs de

aK.

Le mot machine comporte 32 bits, le caractère est à

a

bits ainsi que les microinstructions. Les nombres négatifs sont représentés par leur complément à 2. Chaque processeur dis-pose d'autre part d'une mémoire privée deIl faudra décider eJcactement si cette m~moire priv(;)e sera de 2!{ mots de 16 bits ou de 1I{ mots de 32 bits.

2. D'autre part une ~tude a ét~ faite sur les formes possibles de liaisons entre les ' processeurs et les modules de mémoire. Les possibilités ont e;té 1imit~es à deuJc cas:

a-Une liaison: La barre de liaison a alors une technologie trés rapide, 4 fois le

cycle mémoire par eJcemp1e, pour permettre une certaine forme de'mu1tiprogrammationG

D

1

s:2cesseurs

1

-

mOduIJ.. s de mamoireDO

b-Trois liaisons g Plus eJcactement une

li-aison pour chaque procGsseuroChaque barre a une ,technologie normale.

2

processeurD.

Il était apparu que ces deuJc solut.ions êtaientà psu prés ~quivalent.es,et que le choi:u: final ~t&:U:. encore à faire 0

~. Une fois ces généralités ~tablies,nous

nous sommes donn~s un certain nombre d'él~ments

pouvant former la base d'un bloc de calcul: Soient essentiellement des registres, des mé-moires, et un type d'instruction.C'est sur ces donn4es que l'étude de l'eJcécution des opéra-tions va pouvoir être entreprise.

a-Dans une premi~re partie: le ddcodage d'une instruction.

b-Puis exécution des op~rations arithm~ti-ques et logiarithm~ti-ques usuelles.

La machine étant micro-programmée, c'est sous la forme de micro-programmes que se présentent

les r~sultats.La d~finition des ~léments du bloc de calcul et l'établissement de ces micro-programmes vont être repris dans ce compte rendu de la facon suiv·ante:

I-Dans le premier chapitre: définition des éléments du bloc de calcul. C'est en effet une introduction indispensable.

2-Dans la seconde, étude du décodage de l'instruction et écriture du micro-programme.

3-Dans la troisième partie étude des prin-cipales opérations.

A chaque étape nous po~rrons résumer les carac-téristiques des dj.fférents éléments, qui appa-raissent au cours de l'étude et qui sont

indispensables à l'exécution des instructions. Nous aurons alors une première idée des bascules, des voies de liaisons entre les différents regis-tres et les premiers schemas de l'unité arithmé-tique pourront être tracés.

4. Dans les chapitres suivants nous étudierons les problèmes posés par les opârations en vir-gule flottante. Une fois tous les micro-programmes écrits, nous simulerons dans la mesure du possi-ble ce bloc de calcul en MAP.

Nous pourrons ainsi vérifier que les éléments qui sont apparus.au cours de l'étude sont

suff-isants pour assurer une ex~cution correcte. Ceci étant terminé,nous pourrons considérer que

tous les problèmes relat-.ifs à cette unité micro-programmée ont ét~ abordés et que des solutions acceptables leur ont ~té trouvées.

5. Pour terminer, vu que cette machine dis-pose de plusieurs processeurs, la derni~re partie porte sur une étude statistique des gênes et des perturbations au niveau des m~moi res.En particulier90n pourra comparer plus

précisement les deux formes possibles de liaisons à une barre ou à trois barres. Les queues éventu@ elles seront étudiées en GPSS.

Chapitre 1

."

LE BLOC DE CALCUL

'Etude d'un bloc de Calcul

Nous venons de parler de la machine d'une facon générale sans aborder encore l'étude des mouvements internes et l'eJc~cution d'un calcul. Nous allons essayer d'avoir une idée du déroulement des instruc-tionsélémentaires et nous aurons ainsi un apercu des microinstructions d'eJcécution. Pour cela nous allons considérer un bloc de calcul dont nous allons fixer à priori les éléments essentiels. Nous pourrons étudier sur ce bloc de calcul les opérations classiques et cela nous permettra de fixer avec plus de précision la logique de la micromachine. Nous aurons une idée des couts, des problèmes particuliers qui se posent et nous pourrons définir d'une facon plus rationnelle le bloc de calcul. Une nouvelle étude pourra alors être entreprise d'une forme de macromacl1ine permettant une nouvelle approche vers ce que seront la logique et le bloc de calcul définitifs.

Dans cette première ~tape les éléments que nous allons décrire ne vont pr~juger en rien de ce que sera la machine définitive. Ces éléments sont ceux qui vont servir de base à l'eJCecution des instructions usuelles soient:

les éléments propres au bloc de calcul la technologie

la forme des instructions et des microinstruc-tions.

1. La memoire privée:

Ce sera la m~moire de microinstructions. La m~moire priv4e de chaque processeur avait été choisie de IR mots de 32 bita. Nous allons voir que les registres du'bloc de calcul sont fix~s à

16 bits. Da plus le temps d'écriture pour un mot

6

i,

de 32 bits est de lrs au lieu de 600~s pour un mot de 16 bits. Il semble donc avantageux de prendre des mots de 16 bits et nous consi-dèrerons que la mémoire privée de chaque proces-seur sera de 2K motsde:16.bits.

2. La mémoire scratch pad:

Le bloc de calcul de chaque processeur devra disposer d'une mémoire "Scratch Padlil de capacité réduite qui va se révéler indispensable, comme on le verra en étudiant le déroulement des in-structions usuelles. Certaines de ses positions pourront servir de registres. Cette mémoire sera trés rapide, 300ns de lecture et on peut considérer qu'elle comporte 256 mots de 16 bits. 3. Les registres du bloc de calcul:

Dans un souci d'économie, et compte tenu de la mémoire scratch pad nous allons prendre des re-gistres de 16 bits soient:

l

-2-Un accumulateur A de 16 bits avec bascule de débordement. C'est aussi un registre

..

a décalage.Deux compteurs ordinaux, pouvant servir de registres d'adresse:

le premier pour la mémoire principale com-portant 16 bits: C

- le second, p , pour la mémoire de micro-programmes, de Il bits avec bascule de

dé-.. ~., é

bordement. Il pourra etre equlpe ven-tuellement en compteur de facon permanente. 3 - Un compteur K de 8 bits. Il pourra être:

- un registre de décalage. On considère que l'on pourra avoir des décala~es de 1,2,4,8 positions.

un registre d'exposant dans une arithmétique virgule flottanteoIl aura ~ventuellement une bascule de débordemento

4 - Un registre l pour les interruptions. Il sera seulement écrit de l'eJttérieur par des' Inicre-instructions sp~ciales: Son contenu

indique la marche ~ suivre (M~ge .•• )

5 - Enfin les registres attachés aUJC différentes mémoires et servant soit de registre d'adresse soit ~ recevoir l'information.

- Pour la mémoire ~rincipale: C comme registre d'adresse et deul)c,= registres B et D de _ 16

bits chacun, où un mot mémoire sera transmis.

B D

[

(16) (16). p

~

M. principale!1

6lU- ,

-Pour la memoire de micro-instructions un regiotre adresse de Il bits et un registre

R de 16 bits où seront lues les micro-in-structions.

p

n_-

M~1I

(11)

U~,--_6_---,

R

2K mots de 16 bits

- Pour la m~moire sCl:'atch pad: un registre adresse U de 8 bits et un registre Wl de '16 bits ôlll 18 information sera lue.

(16)

u

~~

__

S_P __~

256 mots de 16 bits8

, '>,

Le r8le, l'utilité et les particularités de chaque registre seront précisés': aprés

l'étude du déroulement des instructions.Nous verrons en particulier si nous pouvons

con-fondre les registres adresse et les compteurs ordinaux de la mémoire principale et de la mémoire de micro-instructions.

4. La technologie

Une fréquence de base de 10 Mhz est tout à fait possible et nous pouvons considé'rer donc qu'elle sera de 3.3 Mhz ou 6.6 Mhz, en rapport ainsi-avec les 600ns d'écriture èt les 300ns de lec-ture des principaux éléments. Il faut en effet que le cycle machine soit ~gal au cycle mémoire, et on aura synchronisation avec une telle fr4quence. L'addition peut se faire en un temps de 10 à 100ns donc dans un cycle de base. Le registre R

contient 16 bits. Nous p6uvons considérer~que les micro-instructions ont 8 bits. R contient donc deux micro-instructions. En faisant l'hypothèse qu'une micro-instruction est toujours exécutable en un cycle de 300ns, on peut envisager de faire en un cycle l'exécution d'une micro-instruction de R, puis la préparation de la seconde par un décalage de R de 8 bits. Nous allons consid~rer en effet que le décodage porte sur 8 bits.

n'ou

le chobc possible de 6.6 Mhz comme fréquence.s.

Les micro-instructionsNous savons qu'une micro-instruction a 8 bits. Une micro-instruction peut indiquer un mouvement à

faire,ou bien elle peut préparer un appel en mémoire: soit en m~moire principale,elle peut alors introduire un nombre de 16 bitsloU bien en mémoire scratc'h-pad, elle introduit alors un nbmbre de 8 bits.

On peut donc avoir dans R:

-Deu::!: informations de 8 bits.Le décodeur ex-iste sur 8 bits donc pour une seule micro-instruction.La première micro'-instruction sera décodée et réalisée par une série de micro-6pèrations par l'intermédiaire d'une matrice par exemple. Puis le système se déca-leget on a un nouveau d~codage.

8 8

R

1 1 1 décodage ..

-Une micro-instruction de 8 bits, préparant une opération en scratch-pad et donc liée à un nombre de 8 bits.

-Une micro-instruction de 8 bits préparant un appel en mémoire principale, donc liée ~ un nombre de 16 bits.Il faudra alors garder en mémoire le mouvement à effectuer, une fois que la micro-instruction sera décodéeo

60 L1instruction

Nous allons choisir une structure qui va nous servir à fixer un procédé d'analyse mais qui ne préjugera en rien de la machine qù'i1 faudrait défin~r d~fini

tivement plus tarde

(6) COo (4) (16) r@h 11~indeJC 1 adresse l~

1ri

.~Incrémentation

ndics paramètre~dressags direct ou indirect

~---npâration ou macro-opération

Sch~ma gânêrnl de la machiner processeur 1 processeur 2 r·7P SP

1

1

SP mémoire principale I ! = = = ! J 4I<' 41\ processeur E/S 41\Un des processeurs a âté représenté avec une fonction particulière8 processeur d'entrée-sortie

(I/O)o

Les m~moires priv&es et scratch-pad sont spéci-fiques de chaque processeuro

r·7P 1 1

II

r

1 112

Chapitre 2

MICRO-SE~UENCES n'ANALYSE

MECANISME DES MICRO-PROGRAMMES

Dans cette étude nous allons trouver trois niveaux d'exécution:

. l-Niveau instruction

C'est le niveau situé au décodage des instructions des programmes de la machine objet.Ce décodage conduit au niveau suivant.

2-Niveau micro-instruction:

Le code· instruction fournit l'adresse d'un micro-programme situé en MP,qui consiste en une séquence de micro-instructionse

3-Niveau micro-opérations:

Une micro-instruction déclenche divers mouvements de registres.Ces mouvements élémentaires de reg-istres sont des micro-opérations~cablées,qui constituent la base technologique de la machine. Ce sont des opérations semblables

à:

-Décalage d'un registre quelconque. -Incrémentation du compteur ordinal. -Certaines opérations logiques bit â

bit, par exemple la négation.

La liaison entre les niveaux 1 et 2 se fait par l'intermédiaire des registres B et_D,qui recoivent l'instruction machine,laquelle est analysée par Un micro-programme.

La liaison 2 et 3 se fait à l'aide d'une matrice de liaison (Wilkes): micro-op l micro-op i micro-inst 1 r micro-inst j , 1, ~

Les micro.-opérations sont des actions élémentaires dont la durée ne dépasse pas celle d'une impulsion de synchronisation, soit 150 nano-secondes.

Nous allons essayer maintenant de résoudre les pro-blèmes que posent les exécutions des programmes.

Nous considèrerons plus spécialement l'exécution des: -Ruptures de séquence.

-appels de sous-programmes. -modifications d'adresse.

Tous ces problèmes apparaissent lors du déroulement d'un programme quelconque.Nous allons donc étudier

14

en d~tail le microprogramme d'analyse d'une instruction machine.

MICRO~PROGRAMME D'ANALYSE DE L'INSTRUCTION

Au début de chaque appel,le compteur ordinal (co), place son contenu en C,registre d'adresse de la mémoire cent.rale.Ce pourra être une position de la

,

.

memo~re scratch pad.

Nous aurons donc besoin d'une micro-instruction qui place l'adresse de co dans le registre U,registre . d'adresse de la mémoire scratch pad.150 ns aprés,au mieux,on dispose ,en M,du contenu de co.En un cycle de synchronisation,on transfère M dans C et une micro-seconde plus tard,au mieux,on dispose dans B et D de l'instruction à exécuter.

La mémoire principale possède en effet un cycle de 2 micro-secondes.C'est une mémoire

à

tores magnéti-ques donc,le résultat d'une demande de lecture est obtenue en moyenne,un demi cycle plus tard,soi.t une micro-seconde.Soit ADco l'adresse du compteur ordinal en SPo .-top synchro -top'{150 ns) -top{300 ns) ADco~U

V

{M)->COn dispose donc de l'instruction dans les regis-tres B et D.Le problème,maintenant est de passer en revue tous les bits de spdcialisation,d'enclan-cher les opérations correspondantes et d'aboutir enfin à la r~alisation de l'opération commandée. Pour cela, plutôt que de sélectionner, par décalages de B et D,des parties d'instruction,ce qui donnerait trop d'importance à la disposition des bits de

spécialisation choisis, nous utiliserons des masques stockés en mémoire scratch pad,qui donc pourront

ê'tre changés à volonté selon la structure d' instruc;;" , tion à traiter,etqui nous permettront, par inter-section,d'isoler les bits voulus.

Par exemple,pour la structure de l'instruction choisie,nous aurons les masques suivants:

-incrémentation 0000000000010000 -indexage 0000000000001111 -macro-instruction 0000000010000000 -paramètre 0000000000100000 -adressage 0000000001000000 Ml M2 M3 M4 MS

Ces masques subiront l'intersection avec le reg-istre B, (D contient la partie adresse de l'instr~ uction) •

l-Test d'incrémentation:

En fait,ce ne sera pas un testoOn fera l'inter-section entre B et Ml et, que le résultat soit nul ou non, on fe'ra l'addition avec l'index,

appel~1on replacera ensuite en mémoire scratch pad cet inde", incrémenté ou nono

2-Test d'indexage:

Ce ne sera pas un test non plus grâce à la disposition que nous avons adoptée:

Les 3 bits d'index fournissant 8 adresses en mémoire SP,nous avons pris les huit premières avec la convention que la mémoire d'adresse

o

contient le nombre 0000000000000000.On indexera donc de toutesfacons. 3-Test de macro-instruction:

Nous avons été amenés à le placer ici avant les autres tests, afin de disposer,dés que cela sera nécéssaire,de la première adresse de la première instruction du macro-code.On placera cette adresse dans le'registre IoCette adresse sera obtenue par addition du code de macro-instruction et de la constante de macro-instr-uction,contenue en scratch pad et définie par le programmeur.

Nous devons,dès.màintenant,montrer comment les tests et les ruptures de séquence,à l'intérieur d'un micro-programme,peuvent s'éffectuer à

l'aide du seul registre K.

Par exemple,on sait que le premier test à effec-tuer est celui de la macro-instruction:Au début du microprogramme d'analyse,ou bien juste avant le test, pour laisser le registre K disponible plus longtemps,on place dans K une quantité

16

égale au nombre de micro-instructions que l'on devra sauter (dans le cas de la rupture de

séquence),diminué de 1.On aura une micro-instruc-tion pour faire cela (transf~rer le contenu

d'une mémoire SP dans K)o

Lors du test du registre A,une bascule liée

a

A se· .positionnera à 0 ou l, selon que (A)=O ou l, et cette bascule validera ou non l'appel de l~ micro-instruction :(à adresse bien définie), sui-vante:s ' i l n'y a pas rupture de séquence (c'es't à dire si cette micro-instruction n'est pas app-elée) ,on ira automatiquement en séquence, puisque le registre P s'incrémente lui même tous les 2 tops de la synchronisation de base. 4-Test de paramdtre:

Il s'effectue identiquement au précédent~',A', noter que le masque MS est utilisé 2 fois,afin de savoir tout d'abord,si on a un paramètre fort poids ou faible poids.Ceci explique l'ex-istence d'une micro-instruction "décrémentation de U".L'existence de cette micro-instruction pourrait faire penser que l'on peut alors

supprimer la micro-instruction "incrémentation de

u",à

condition que U s'incrémente lui-même' tous les 2 tops de synchronisation.Ceci n'est pas possible,car l'on a besoin de conserver, durant des temps trés variables,le contenu du registre M (lecture de la scratch pad),et l'incrémentation de U se revèle nuisible. S-Test d'adressage:Aucune difficulté si l'adresse est directe.Une micro-instruction place le contenu de D dans C et on recoit l'opérande de 32 bits 7 tops de synchronisation plus tard.Celui-ci arrive en B et D et i l faut décoder aussitôt que l'on a lancé l'appel sous peine de perdre le code. ,Dans le cas le plus ddfavorable,il faut avoir

le temps de faire 2 tests,2 transferts simples, un décalage et une addition de registres,ce qui est possible en llSO nanosecondes.

Si l'adresse est indirecte,on doit additionner soit le paramètre situ~ en partie adresse de

l'instruction d'adresse 1000 (dans notre exemple), soit l'opérande contenu à l'adresse située en

partie adresse de l'instruction placée en 1000.

On doit donc reprendre entièrement le micro-programme d'analyse de l'instruction,en ayant soin de conserver le registre B qui contient le code machine à exécuter,et tous les bits de spécialisationo

18

o,n emploiera donc,dans ces cas là,la micro-séquence suivante:

i - - - -

(D) ~c ~,--- -decr U temps de lecture SP temps de L.'- - - - > -

(M) --;::.A l~ct~re en -A~A memOl.re appel en mémoire (M)=M5 - (D)A (A) ->A. - - - -ad [Ml]

->U

'---t--~ - (A) ->B

~

r...-_---::::>

sui teLa micro-séquence ci dessus se raccorde au micro-programme d'analyse au niveau de l'in-crémentation o

La fin du micro-programme d'analyse condui"t: à la situation standard,c'est à dire que l'opérande

à manipuler se trouve dans les registres B et D, cadré comme il convientoOn y est conduit de trois facons possibles: a-Paramètre droit b-paramètre gauche c-Adresse directe [on efface B [on conserve D [(D)~B [on efface D [(D)~C

[l'operande arrive en BDo

Une fois dans cette situation standard,il faut appeler le micro-programme d'exécution du code machine,si on est en présence d'une instruction normale (dans C), ou bien appeler une ins"truction en mémoire centrale si on vient de traiter une macro-instruction (en I)oLa distinction se fait

~

..

Avant de ,faire ce test,on envoie l'opérande dans les mémoires de travail de la scratch pad. L'op~rande occupant une position de 32 bits,on aura besoin de 2 adresses en SP:

SPTRI et SPTR2 (gauche et droit) 0

La micro-s~quence sera la suivante: -Situation standard retour -(B}-;:;'M au d~but -SPTRl--~U

1

-(D)~M

-SP'L'R2-~U '-_I..;...-I_O _ _ --...;._ -Te st l '"I~O

-(C)->pl '

. ,'V} i eJcecut on du code.Dans ce micro-prdgramme d'analyse,on a traité tous les cas de modifications d'adresse. voyons les problèmes posés par les ruptures de séquenceo Rupture de séquence:

Soit une instruction de saut inconditionnelg

SAUT M

Le micro-programme d'analyse commence par effectuer toutes les modifications d'adresse désirées,et M devient NoPUis le code SAUT est analyséoIl lance le micro-programme correspo~

dant,tandis que l'instruction placée à l'adresse N est imm~diatement appeléeo

Le micro-programme en question a seulement à -, corriger le contenu du compteur ordinal co,

pou~ continuer en s~quenceo

On a eu alors: -(C)--?>A

-(A)+l~

-(A)~M

-ADco~U

et on reprend le micro-programme d'analyse "à la hauteur de l'incrémentation puisque l'ins-truction suivante est déja en place.

..

,

Problemes poses par les appels de sotls-progr~es:. Un sous-programme n'est pas spécifique du programme en traitement.C'est là que réside

la différence à faire avec une macro-instructiono

Une macro-instruction est définie,rédigée en même temps que le programme.C'est une opération que l'on effectuera souvent,comportant une

suite plus ou moins longue d'instructions normales.C'est pourquoi il est commode de la repérer par un code spécial,unique.Une macro-instruction correspond à la notion de procédure en ALGOL.Un sous programme lui, est défini une

fois pour toutes (calcul du sinus,multiplication en VF, ••. ),et est utilisable par tout programme présent en mémoire centrale.

Fondamentalement,cependant,une macro-instruction et un sous-programme sont utilisés à des fins semblables et,dans une machine micro-programm~e, ne se distinguent pas.

Dans le cas présent,tout sous-programme sera repéré,comme pour une macro-instruction,par le

b ' ~t m= .Nous avons 1 3 " opera t ' ~ons a assurer: .. -La progression artificielle du compteur

ordinal et sa mise en mémoire.

-L'envoi au sous-programme et son exécution. -Le retour au programme principal.

A condition d'encadrer tout sous-programme par 2 instructions de saut inconditionnelj. on

peut grouper la première et la deu:ldème opération.

( ,

Considérons un sous-programme s'~tendant de la mémoire 500 à la mémoire 540oL'instruction

de la m~moire 540 doit ~tre:

.- Saut inconditionnel à 500

ce qui est facilement réalisable lors de la rédaction du sous-programme.L'instruction de la mé~oire 500 sera elle aussi un,'

- Saut lnconditionnel à Je+l

si Je désigne l'adresse de la derniêre instruc-tion elcecutée dans le programme principaloLe sous-programme d~bute en fait à l'adressa 501~

X+l programme principal ,....---~ 500 ---I---~ 501 540 sous-programme

EJcaminons la séquence d v appel 0

Arrivé à la fin du micro-progrrumne d' analyse, on est dana la situation'standard,et pour un sous-.. programme,on reprend ce microprogranwe au de~ut avec les micro-instructions qui suivent 0

Par sJtemple (1)=500. Le co contient JCo On a donc la micro-s~quencs suivante:

-ADco--?>U - (M)-.>A -(A)+l->D -(C)~A -(A)+l->A -(A)~M -ADco->U

~

vers le microprogramme d'analyse en 500 on al Saut JC+lOn a stocké le co (en partie adresse de~~500).

On a enclenché l":eJc~cution du sousprogramme en pla~ant 501 dans le co.

22

Le retour au programme principal est assuré, car la dernière inst~~ction renvoie

à

500, instruction de saut inconditionnel en X+l, qui re~enclenche le d~roulement du programme principal et assure la modification du co~ ùl,

1 ! f r 1 1 1 ! f : 1p

La sequence complète de micro-instructions esta l-Incrémentation:

-Appel du premier masque -[U]~M

-MflB--:s>A .

-A décalé de 4 positions

à

droitè -C-~SPOOO2-IndeJc

-Appel du second masque -[U]~M -MnB-!,>A -U~K -Ad[A]~U -U~M -M-~A -A+C-~A -A+D->D -I{-;;:.U 3-Macro-opération

-Appel du troisième masque -[U]-~M

-lYlllB-~A

-Appel. du masque eJctraction co - [U] -::>M

-M"B-~A

-Appel constante de réference -[U]->M

-Décalage de A de lO,positions à droiteo -A+M-~A

4-Indice paramètre

-Ap~el du masque suivant -[U]-~l4

pose d'un indicateur l

1=0 1=1 on doit chercher lOopérande D est l'opârandè ':"Raz B \ :-B-:>SPIO -D-.:>SP11

5-Adressage direct ou indirect -Appel du dernier masque

o

direct -:,(D)-->C - [Cl -.>BD -B->SP10 -D->SPll - CU] --;>1\1, puis execution du code opération nous avons deuJc casl I=O -SP~A -A-;:'P -[P]->R R est la première micro-instructionpose dlun indicateur 1 indirect

on doit avoir l'adresse

[D]

-D-.>C _c[C]->BD

on reaommence les opérations 1,2,364 jusqu'

à

l ' obtant:l.onde l'op~rande long.

I=l -SP->A

A est l'adresse en mémoire de la premiêre opération

-A-:>C

-[C]->BD

Ceci est la succession des micro-instructions du micro-programme d'analyse.Ce programme sera utilis~ à chaque appel dl instruc,tiono Il devra

donc être rapideaOn peut avoir une bonne idée de sa duree en faisant le compte des micro-instructions qu'il comporteoEn nous placant

, 0

dans le cas le plus defavorable on a 28 mouv-ements de registres

à

faire', ce qui demande le temps de 40 2 microsecondes.Dans le cas le plusfavorable le microprogramme ne dure que 2u4

microsecondes.Ce temps est peu influencé par l'adressage indirect ou la macro-instruction. On peut noter aussi qUe certains mouvements de registres pourront être regroup~so

En définitive,on peut considérer que le temps de déroulement moyen ?u programme dOanalyse est de 2.5 microsecondes~ 24 1 .' 1 r 1

Nous pouvons établir une première liste des micro-instructions que nous utiliserons:

Registre A:

-A décalé de 4 pOSe

à

droite.-dr[A]~U -A~P ·-A--:;"::1M' -A-->D -Raz A -A+l->A Registre B: -Raz B -B-;>A -B-;:;.D Registre D: -D-bC -D-;;>M Registre M: -M->C -A+M-~I -BfbM-~A -BI\M-c::-C -M->B -M-;;::.D -M+A-;>M -M+D-;>D Registre U: -Incr. et décr. U. -U-~K Registre P: -P+K-;>P Registre 'I: -I-:>C Registre K: -K-c:»U

Dec Add 1 -Tra Registre RI -R-t:>oI\ -R--t:::oU Registre Cz -C--c::>P -dr[C]~U

Nlont pas été écrites les micro~instructions qùi

font intervenir la mémoire Scratbh Pad.En effet tous les registres ont accés à cette l1lémoire;dans les deu:lc sens.

Lee Div Soitl [B [D Sp.<~·[C [A [M

Nous aurons d'autres micro-instructions qui appa-raitront dans lDétude des opérations arithm~tiqueso

On aura le schéma général suivant:

r'lémoire privée 1 \

~

Adresset

(decodeur) I l . -_ _ r:-"'~=,I pIf

V

\J \}vers les registres. . code opération

Liaisons du registre A avec les autres registres: ~ M r--~ ~ '-",

l r -~-

...,. '" p:) '-~~

,..-'C'

..-'! ~-~

...--

~ f...t ... ... ID '0 r--'0-

~ ,..;;::; ~ ' - ...-r 0 -I

~-

-r

... ... -ê'-~ r-t~ r - ~I ~ ..- .-.--9 lI-I

0 '-28

Liaisons des registres B et D avec les autres registresl

Adder \ ( ~

]\

1

r

q\

j\J

11

1

1

;j\"

'1\1

1l

1\ '" j 16 ~r

~ n,~r7 \ \ rl \'1 1rn

n

u

1 1 A -11

D1

1

B1

1 M1

U

Chapitre 3

. OPERATIONS LOGIQUES ET ARITm·1ETIgUES

PRELIMINAIRE

l~Les instructions que nous allons étudier vont pori:er sur des nombres extra,i ts de la mémoire principale,donc de 32 bits.Il y a de nombreux cas où ces nombres seront courts,c'est à dire auront moins de 16 bits. Leur manipulation peut se faire directement dans les registres de 16 bits et cette arithmétique qui est l'arithmétique d'adresse doit être facilitee au maximum.Nous

allons donc prévoir à chaque fois deux instructions différentes, par exemple addition courte et addition longue.Le programmeur devra savoir la taille des nombres qu'il manipule et quelle instruction il aura alors à employeroDans les cas où les nombres seront longs, ils se tr~uveront l'un en Scratch Pad 10,11 l'autre dans les registres B et DoSi les nombres sont courts ils seront en SPll,et en Do

2-Dans la partie précédente nous avons vu l'analyse d'une instruction jusqu'à ce que l'information arrive dans les registres B et DoSoit T l'ensemble des micro-instructions formant cette séquence.

T va être commun à toutes les instructions que nous allons étudier maintenant.Nous n'allons pas figurer cette séquence T au début des microprograrnrnes d'exé-cution des opérations que nous allons voir.Nous allons directement aborder les calculs en supposant que le nombre vient de se placer en B et Do

Nous allons appeler °chargement"l'instruction qui permet d1amener un opérande en SPlO,ll:Quand nous ferons une opération necéssitant un deuxième nombre, le premier sera placé en SPlO,lloLe deuxième nombre peut alors se placer en BD, sous l'effet de l'instruc-tion addil'instruc-tion par exemple,et les calculs peuvent

commencer. Une instruction demandant deu}c opérandes suc.,. cèdera à une instruction chargement. Son décodage

sera la séquence Tc

~~rections à apporter:

Nous savons que les nombres négatifs sont représentés sous la forme de leur complément à 2. Il faudra

donc apporter éventuellement des corrections: -Si les deux nombres sont positifs on ne pourra

craindre qu'un débordement de capacité.

-Si les deuJt nombres sont .n~gatifs, si le bit de signe du résultat est eJcact on néglige le bit de débordement1S'il est incorrect on a un dépa-ssement de capacité.

-si un seul nombre est· négatif l'addition se fait normalement.On néglige le bit de d~bordement

éventuel. E::cemplez 7 -3 i,\ 0111 1101 1 0100 R~sultat eJcact 1 bit à négliger -7 1001 -5 1011 -12 1 0100 Signe faux Dépassement de cap. 3 -7 -4 0011 1001 ·1100 Ré sul tat eJcact

-3 1101

-1 1111

-4 1 ·1100 Signe eJcact

1 bit à négliger Nous allons utili.ser deU:lc indicateurs I, I O qui . indiqueront le signe des deuJt nombres.

Aprés lladdition no~s aurons donc la séquence suivantez

Non Résultat correct Test retenue ~ l ou l'=O Deux nbs positifs :pépassement de capacité Oui

v~

l ou l'=l l et l'~l Un nombre positif Résultat correct Deux nbs négatifs On teste le signe du résultat 32 Si exact on néglige le bit de retenue Si faux on a d~pas sement de capacitéNous supposerons par la suite que le dépassement de capacité doit être signalé par un indicateur

(Impression message éventuel p~r I).

Remarque:

Il Y a un cas trés particulier qui n'a pas été prévu. Considérons en effet que les registres ont 4 bits et faisons -7-1:

-7 1001

-1 1111

-8 l 1000

Nous voyons que le signe du résultat est exact.Mais· le nombre que nous obtenons 1000 n'est pas -8 car on a eu un dépassement de capacité. Donc le seul test sur le bit de débordement et le signe du résultat ne

s:lffit pas. Il faudra prévoir le test qui consiste à voir si l'ensemble des bits autres que le bit.de signe est vide ou non.

séquences de micro-instructions: A- Les deult nombres sont courts:

Le premier est placé en SPII,le second en D. -SPII-~M

-Test signe .rol: indicateur lm -D~A

,-Test signe A:indicateur la -M---:i:>D -A+D-»M -Test retenue Non Rssultat correct A Oui

~~~

lm ou Ia=O lm ou Ia=l Im et la=l nâpas seme nt de capacité -A-~M -M-~SPII R~sultat e:mlct en A Test du rêsultat sans signe Si résultat =0 ove rfl 0\'1 sinon r<$sultlat eltact en A

Ces deUlt dernières opérations préparent les instructions suivantes.

B- Les deult nombres sont longsg

Ils sont placés en SPIO SPII et BDo

-SPII->M -.rol->A -A+D=->A -Test retenue Non Oui· /,

-A-~D -B->A -Test A:la -SPlO-~M . -Test M: lm -M+A-.>A -Test retenue Non Résultat SJcact en AD AD-~SPIO SPll Soustraction: -A-~D -B-~A -Test A:la -SPlO-~M -Test MI lm -I-i+A+l-.:>A -Test retenue oui

On a les mêmes tests que précédement sur la et lm le résultat éventuel est ~n AD

AD--::,,>SPIO SPll

Il faut d'abord prendre le compl~ment du nombre en BD1 Le déroulement est alors le mëmeo

INTERSECTION

L'intersection se fera directement dans l'unité arithmétique du bloc de calcul,en un cycle de baseo

A-Deux nombres courts: -SPll-.>M

-M-~A -AIlD->A -A~SPll

Le r~sultat se trouve en SPII B-Deux nombres longs:

1 .. " On a a meme sequence manipulant la deuJdème -SPlO->Xv7 -M-.:>A -B-~D }~At\D->A . -A-.>Xv7 -Xvl~SPlO P If) i 1) .precedente /1 pu s la sequence tranche de 16 bits soita

Le résultat se trouve en SPIO SPllo

REUNION

Elle est analogue à l'intersection mais se fait simplement par une r~union bit à bit des lignes portant 11 information repre'sentant les nombres.

A-Deux nombres courts:

-SPll~M -M-:;,A -AVD->A -A---?'>M

-M--?SPll

B-Deux nombres longs:

On a la séquence précédente," qui se poursuit par: -SP10-;:::-M -M-7A -B~D -AUD-~A -A-.>M -M--?SP10 DISJONCTION

AQB= (AI\B) \J (AAS)

Elle peut se faire par une combinaison des éléments précédents, ou bien directement dans un dispositif spécial de l'adder ce qui semble superflu.

COMPLEMENT A DEUX

Il s'obtient directement par un dispositif spécial li~ à l'adder.

A-Le nombre est court: D

-Complément à 2 de D--~A

-A->M -M~SPll

B-Le nombre est long: BD

La séquence précédente est valable pour DoIl fau,dra ,voir si on n'a pas de bit 1 indiquant un dépassement de capacité de A,lors de la '

complémentation de D.On ne devra prendre que le complément à 1 de B.On a donc en plus&

-B-;>D

-Si retenue,complément

à

2 de D~A -Sinon,complément à 1 da ~-->A-A-.>M

-M~SPIO

Cela se voit théoriquementz

N=A+2-n~1'B

C2 long=-N=2-A+2-P(2-B)

Il faut propager la retenue de B dans A. r·IDLTIPLlCATION

Nous avons deux fa~ons de représenter les nombres:

en convention des entlers ou en convention fractionnaire. Nous allons étudier la multiplication de nombres en con-vention des entiers car c'est celle qui est plus

directement accessible. Corrections à apporter:

Il y a des corrections dans les cas où le mult~ plicande ou le multiplicateur sont négatifs.

-Soit X le multiplicande,y le multiplicateur X positif,Y n~gatifo

P=X(2 n_Y)=2nX_ [XYl P=2 2n_[XYl_2n (2 n_X)

P=Fig (XY) _2n (2n -X)

On voit que pour que le résultat soit correct il faut ajouter le complément du multiplicande X aU't bits forts poids du résultat.

-On aurait une correction analogue si X était négatif et Y positif. Il faudrait alors ajouter au}c bits forts poids du résultat le complément de Y.

-Dans le cas enfin ou X et Y sont négatifs il

36

faut ajouter aUJ' bits forts poids du résultat le complément à 2 de X et de y~ (Livre de I-7r Ho BOUCHER Organisation et 'fonctionnement des machines arith-métiques)0

On peut éviter la correction dans le cas où le multiplicande X est négatif.On peut en effet ajouter au produit partiel un 1 d~cal~ dLune place par rapport au bit de plus fort poids de ce produit,chaque fois que le multiplicateur contient un zéro.L'opération sera complète quand on aura ajouté un 1 aux unités de fort poids

(H. Boucher).Nous allons voir que ce procédd nécessite une bascule supplémentaire.

Séquence de micro-instructions. A-Les nombres sont courts:

l-la multiplication en est alors bien facilitée. Considérons que nous employons d'abord la méthode qui consiste à faire les corrections aprés que le résultat ait été obtenu. Nous ferons donc les opérations préalables comme si les nombres

étaient positifs.

E1~

multiplicande B 1J

accumulateur A41

mul tiplicateur DL;:{Ïa-,

LI

,

ri

I~wLe multiplicande est en D.Il sera décalé bit

à bit et chaque bit sera testé en Id.A et D se décalent ensemble,les additions successives se faisant en AD

lb sert à tester le signe du multiplicande B~De même aprés le dernier décalage de AD,Id contien-dra le signe du multiplicateur.On pourra alors faire les corrections. Nous allons prendre K comme compteur des bits du multiplicateur.

Le résultat de l'opération sera AD.Il sera envoyé en SPIO SPll où, il pourra être ensuite utilisé. On peut penser à ne garder que les bits forts poids,les nombres X et Y êtant courts le résultat alors sera ~ et sera placé en SPII.

--,

La séquence de micro-instructions s'écrit si

le multiplicande est SPII et le multiplicateur D~ :"'SPll~M -M-.>B -16->1(' -RAZ A , . . - - - : .. "'> - (1(') -1->1(' -Décalage de A et D. -Test de Id Id=O Id=l -A+EI-:>A ' - - - -'l'Elst (1,)=0 non tOui -Décalage de AD de 1.

On peut alors faire les corrections en testant Id et lb et ajouter les compléments éventuels. On s'apercoit alors que le multiplicateur a été perdu et qu'il faudrait l'appeler de nouveau. On a une perte de temps et c'est pourquoi la correctio~ à faire si le multiplicande est nêga-tif sera faite directement dans le calcul.On n'aura plus alors à ajouter le complêment du multiplicateur .Soit la l'indicateur de retenue de Ao

2-Nous allons faire cette correction mais pour cela il faut garder en mémoire à l'instant i+l le bit de D de l'instant i.Il faut donc avoir:

1

multiplicateur DI-~J

Idll~I

Id21A l'instant i+l Idl contient le bit du multipli-cateur qui va déterminer si on fait une addition dans A~Id2 contient le bit qu~ servira éventuelle-ment (si )C est négatif)" à ajouter un l en

pos-ition fort poids de AoOn aura donc:la séquence

\

de micro-instructions suivante:

-SPll-.>M -M->B -16->1(' -Raz A -Décalage de A et D. r---t~ - (1(') -l--:;'!!>I(' -Test de Id1 Idl=O NOp Id1=1 -A+B-;>A -Décalage de A et'Do -Test Id2,Ib Ïd2nlb=1 _A+2n-l_:>A

1---

-Test (I('):::lO Oui -Tqst lb Ib=l -A+1-~A Idl=-l -A-~C -Test Id1 -Comp2 B-:::.A -A+C-:>A -Test d~bordo -A~.>M -~7-~SP10 -D-~M -M-.>SP11, Sinon rien Ib=O Nop Idl=O Nop~u bien si on a pr~vu d'avoir un résultat court:

-A-;>M -M~SP11 EJcpliquons cette séquence 0

Le premier test est pelu! qui est normal dans une mu1tiplication:C'est le test du bit du mu1 tiplicateur. Le secc>nd test apport.e une' correction ,si rd2~Ib=! soit lb=! et Id2=O.

Il correspond au cas où le multiplicande est négatif et l'opération qu'il entraine évite la correction finale~On ajoute à A un bit 1 en posi~'

tion de plus fort poids.

~~~

1 A'1\1

Dans le cas où i l y aurait débordement de capacité· i l faut que l'a se r~porte dans A, dans les d~

calages.Le résultat sera alors exact.

NOUS avons ensuite le test de fin d'opération,

puis le test correspondant à l'achèvement de la première correction'(multiplicande négatif).On ajoute un l en position faible poids de A. Le dernier test est la correction à apporter si le multiplicateur est négatif:on ajoute le complément du multiplicande, soit B,auJc bits fort:·; poids du résultat:A

Remarque:

La séquence précédente a été écrite en figurant des tests de bascules.En fait i l n'y a pas de test èt la séquence peut s'écrirez

p: -SPll-~M p: -M-t>B p: -16~K p: -Raz A p: -Décalage de A et 'D .. p: - (K)-l-;;>K ~ Idl pt -A+B-~A p: -Décalage de A et D. Ïd2f\Ib p: -A+2 n-l -;::.A

(R') -Rupture de #

p: sequence

lb p: -A+l-i;>A Idl p: -A-.>C

Idl p: -Comp2 B->A Idl p: -A+C-:>A

l'a p: -Débordement (message) p: -A-:>M·

p: -M-;:.>SPII

p est le pulse de synchronisation.ldl p s'éff-ectue seulement si Idl=I.Si Idl=O on a rupture de séquence vers la micro-instruction suivante. Les l'a,Idl,Ib sont les lndicateurs précédents. B-Les nombres sont longs.

Ils sont placés l'un en SPlO,SPll l'autre en BD. Nous allons employer la méthode permettant

d'éviter une correction si le multiplicande est négatif.NoUS aurons une séquence de micro-j.nst-ructions analogue â la précédente mais plus

compliquée évidement.II faut prévoir la'multipli-cation de D par SPlO,SPll puis la multiplila'multipli-cation de D par ce même nombre:d'où le test (1(')=16. Ensuite le test normal sur le bit du multipli-cateur IdiLes corrections si le multiplicande est négatif sont faites si lb=l et Id2=0. Si (K)=O il faut Jventuellement ajouter un 1 complétant la correction si le multiplicande est négatif.

Il faut aussi une correction si le multiplicateur est négatif. D'où le test lm=l.

Le résultat s'inscrit sur quatre positions SP20, 21,22,23 ceci au cas où l'on voudrait une double précision mais en fait seuls les bits fort poids sont conserv~s et 'envoyés en SPlO,ll.

-Raz A,SP19 -32~K -D~C -SPll--;:>M -M~SP12 -M~D

,

_---~ -Decalage de D avec report " danr~ Id.si oui Id=O

-

-·SP22-~M -M~D -SP21->M -M~A -Décalage de A,D de 1 sans "report dans Id. -D--?:>SP22 -A-;>D -SP20-:>M -M~A -Décalage de A avec report' dans D. -D-»M -M-~SP21 Ib"Ïd2=1 -'test (I{) =16 -SPIO->M -M-:;:.SP12 -SP22~M -M~SP23 -SP21-;>M -M--?:>SP22 -SP20~M -M-~SP21 -SP19-~M -M---;::,SP20 Id=l -SP22~M -M-~D -SP21~"'>M -M-;:;.A -A+C-~A -D~cal. AD sans report dans Id .. -D->M -M~SP22 -A-~D -SP20-;1;>M -M-~A l'a=l -A+B+l~A l ' a=O -A+B-~A l'a=1[''':'SP19--t>M - (K)-l->K -SP22-?:.>M [-M+l->M [-M->SP19 -Décal. de A avec report dans D .. -D-".>M -M->SP21 -D~calage de D avec repQrt" dans Id._A+2~b': (n-l) ~A -A->M -M-~SP20 1 -_ _ _ _ _ _ _ _ _ _ - (K)=O (K)=O lb=l [ [ [ [ -SP21-~M -M->A -A+l-~A ':"A->SP21 42

Ib=l [ l'a=l [ -SP20...;;>M [ [ '':'M-':>A [ [ -A+l->A [ [ -A--:!'>SP20 [ [ -Débordement de capacit~ -SPIO-..~M Im=l [ -SPll-:>M [ -Compl.2 de J).7->}\ [ -SP2l-~M [ -M+A~A [ -A-:.>SPII [ -SPlO--:>M [ -Compl.l de r·7-;>A [ -S~20-~M [ l'a=O -A+.M->A [ l'a=l [ -A+M+l-~A [ [ -Débordement de capacit~ Im=O [ -SP21-;:..M [ -M--r.>SPll [ -SP20->M [ -r-l-:>SPIO Remarque x

Dans cette séquence nous avons des micro-instructions particulières.

l-D~calage de A,D sans report dans Id.Cela signifie que A et D sont decal~~ mais que les indicateurs Idl etld2 restent inchangés.

2-Dâcalage de A avec report dans D.A se décale à droite et le bit sortant se transmet dans D.

r~J==A

==1

=:::.J~ll-!-~:

I_D

- - - - 4n-l

3-A+2 -.:>A

C'est à dire qu'un, l est ajout~ au bit de plus fort poids de A.

.J

DIVISION

La division se ramène à une série de soustractions mais on a des complications par rapport à la multi-plication.

-Diviseur nul.

-Dividende plus grand ou plus petit que le diviseur suivant la convention entière ou fractionnaire. On sait que si la machine est fractionnaire,pour

que la division soit possible il faut que le diviseur soit plus grand que le dividende. Sinon le résultat . donne un nombre plus grand que 'l,que la machine ne

peut pas représenter. Nous allons ~tudier la division en convention fractionnaire.

Le test utilisé portera sur le reste.C'est préférable à la méthode qui consiste à comparer les deuJc nombres. Dans le cas d'un arret possible il sera facile à dé-tecter:Si on a une retenue du dernier ordre indiquant une impossibilité, cette retenue ferme les gates et la soustraction ne se fait pas.

Il y a plusieurs méthodes possibles pour la division: Méthode de restauration:

Soit X le dividende,Y le diviseur.On a l'organigramme: Dividende-Diviseur

1

1 _

Si reste positif -On ajoute 1 dans

le quotient Q.

-On met le résultat de la soustr.ds A.

-On décale de 1 à

gauche A èt Q.

1

Si reste negatif

-On ajoute le diviseur a A.

-On met 0 dans Q. -On décale à gauche

A,Q de 1.

1

i

Nouvelle soustraction

X-y

Q est le quotientoOn peut représenter facilement les deuJc nombres et le résultat Cl El· ils ont 16 bitso

Diviseur

rn-

i videndeJ1

Quotient 1(accu A)

Méthode de non restauration:

Dans le cas prscédent,si le reste est négatif on ajoute le diviseur,puis on décale l'accumulateur (X-Y)+Y et on retranche alors le diviseur à l'é~

ape suivante.

On fait donc (X-Y)+Y-Y/2=(X-Y)+Y/2

On voit qu'il sera plus simple,dans le cas où le reste est négatif,de décaler l'ensemble accum~

lateur et quotient,et d'ajouter alors le diviseur. D'où l'organigramme: X-y Test de l'accu D 1 i . 1 , Reste negatif -On décale A et Q. -On additionne le diviseur dans A

r

Reste pos t~f -Addition de l dans Q. -Décalage de A et Q -soustraction A-Y 1 JNouveau test de l'accu. Séquence de micro-instructions

A-Les nombres sont courts:

SPll est le dividende,C sera le diviseur.

Le quotient va se trouver dans D,le complément à 2 de C sera place en SP14.

Nous n'allons considérer que des nombres positifs. Nous prendrons la méthode de non restauration et les nombres seront pris en convention fractionnaire. On a vu que cela. revenait à mettre des zéros à

droite du dividende. Ils appa~aitront ici lors des décalages. Nous conviendrons donc de dire que tout décalage sur le dividende, soit A,arnène des zéros sur les bits de plus faible poids dans le cas d'un décalage à gauche. A est l' accumulateur. Il contient

-Raz C -complément 2 de C--~A -A->M -M~,,>SP14 -16-~I{ -SPll->M -M-::::.A ~ ___________ ~ -SPI4~M -M+A-:s>A

Ia=l [ -Décalage de A et D de 1 a

..

gauche.[ .4A+C-~A Ia=O [ -D+l-::>D [ -Décalage de A et D de 1 à gauche. [ -S PI4--;:>,M [ -M+A-~A - (I{) -l->I{ -D-:>M -M->SPII

Pour que ceci soit complet il faut tester le divi-seur pour savoir s'il est nul.

Soit Ic=O: impression message.

Ceci est trés facile à obtenir par un indicateur relié à toutes les bascules du registre C.

B-Les nombres sont longs:

Ils sont en SPIO,SPII et B,D.Nous allons placer le dividende en B,C. AD jouera le role d'àccumula-teur.Il nous faut aussi le complément du diviseur BC.Nous aurons les mêmes remarques que précedementz nombres positifs en convention fractionnaire.

La sequence de micro-instructions s'~crit: -Raz SP2l -D-;:::.C -Comp2 de C~A -A-~M -M-~SP14

l'a=O [-Compl de B--~A l'a=l [~comp2 de B~A

[-Dépassement de cap. -A-;;::.M -M-::>SP13 -32-~K ~---~ -SPl4--~M -M-~A Ia=l -A+C-~ -A~D . -SP13--...,M -M->A l ' a=O [-1\+ B->A l'a=l [-A+B+l--~A -Décalage AD de 1 à gauche -A-::>M -D->A -A+C-;;:.A -A-;::;.D -M->A l'a==O [-A+B--:>A l'a=l [-A+B+l~ -SP20-~M -M-;:>D I;1.=O -Décalage de AD de 1 à gauche -A->M -M->SPl5 ':"SP14-:>M -M-:;:::..A -A+D-;::.A -A---!.,>D -SP13-r M -M-.>A -SP15-;>M -Décalage de D de 1 à gauche -D->M l'a=O [-A+M ~A l'a=1 [-A+M+l--~ -SP2l~M -M->SP21 -..i - (R) -1-:>1<" ~ ______ ~ ____ ~~~1_6 ___________ test (K)=ffi6 (k) =16 . [-SP2l->M [-M-~SP20 [-Raz SP21 I~O' I -_ _ _ _ _ _ _ _ _ ..::.;:t....::-.. _ _ _ _ _ test (I()=O \ -M+l->M -M-:>D -Décalage de D de 1 à gauche -D-.>M -r-i-;>SP21

(1(') =0 [ -A-"::bM [-M~SP22 [-D-~M [-M-->SP23 [-SP20-::::.M [-M~'SprO [-SP21->M [-M--!>SPll 48

Mtcro-instructions utilis~es Registre A: -A--t>D -A+B+l-:>A -A+B-~A -A+M-~A -A+M+ l--.."'>A -A+C->A -A+D~A n-l -A+2 -:!:>A -AVD--t>A -Af\D~A -complément à 2 de D--~A -complément à 1 de D--!>A -compl~ment à 2 de .M--~A -compl~ment â 1 de M--~A -complément à 2 de C~A -complément

a

2 de B~A -complément à 1 de B--~A-décalage de A avec report dans Do Registre A et D:

-dêcalage de A et D sans report dans Id. -décalage de A et D.

Registre D:

-D+l-~D

-décalage de D de 1 à gauche.

-décalage de D avec report dans Id. Registre B: -B-~D Regi stre .lV1: -M+ l-::>r-i Registre K: - (I{) -1-· :l>K -16-:>I{ ..;.32->1('

Particularités de chaque registre (indicateurs). Registre MI 8---,,--1-11 _ M _______

Sll

f

~

bJ

Registre A: Registre D: Registre BI B 1ÊJ

Indicateur de signe de M:Im M est équipé en compteur

Ilia (A)=O?

Indicateur de signe:la Indicateur de retenue:l1a

D est équipâ en compteur

1

1

l'

Indicateur de signe:Ib l'b:ensemb1e des bits de B

sans le signe nul?

Registre C:

IJ;L JI

,'/~

c==J

Indicateur (C)=O.Nous pouvons tracer le schéma des voies de relation de A et des autres éléments du bloc de calcul, (page suivante) ..

52

[j-

... .... 1 i ! CJ ... -t:l :;..-' ,:Q ... ~ .; r-I t:l[r=ï]

..

t:ll!

: - - ,:Q .....

~, Q)...

:;: ~ ; ' Of -ri-

+1 "Q) r-IN.

~

" - r-I ~ -ri--

~ Pt J..I.-B

ru tJ <aQ) +' -ri - t - s:: ::tr~

-~ r-t,-Chapitre 4

ARITHMETIQUE

ARI'rHMETIQUE EN VIRGULE FLOTTANTE

Gén~ralit~s :

. l-Considérons la représentation des nombres rê~ls en virgule flottante sur les modèles IBM 360. Il Y a des nombres ~ourts et des nombres longs, sous la forme:

nb court (32 bits) 1 s 1 caract./ fraction 1

o l 7 8 31

nb long (64 bits) r s / carac'ê. / fraction

o

l 7 8 63Pour la fraction, l'unité de base est 16, c'est à dire que les nombres sont représentés en hexa-décimal.

La technique employée consiste à avoir un seul signe, pour la fraction. On a 6 à 7 chiffres de

pr~cisio.n pour les nombres courts, et jusqu'à 17 pour les nombres longs. Soit f la fraction. On a:

o.

5~1

f I~l (nombre r!0).L'exposant est de 7 bits, c'est à dire peut prendre les valeurs de 0 à 127. En fait comme i l faut

pouvoir représenter les exposants négatifs, on a la méthode classique qui consiste à ajouter à l'exposant le nombre 64, et on obtient alors la caractéristique. L'exposant réèl est un nom-bre qui peut varier de -64 à 63.

C=Exp+64

2-La fraction doit toujours être normalisée. Cela donne une plus grande précision et explique que l'on ait 0.5~lfl~1, pour les nombres non nu~s. On distingue la prénormalisation et la post-normalisation:

-La prénormalisation se fait sur les nombres avant que ceux-ci interviennent dans une opération.

-La postnormalisation se fait sur le résultat.

La normalisation se fera toujours simplement par un décalage de la fraction à gauche, et en même temps la caractéristique sera diminuée de 1.Le zéro est représenté parz

o

3-Dans notre cas la représentation des nombres en virgule flottante sera analogue â celle que nous venons de voir.L'exposant sera un nombre variant de -64 à 63.La caractéristique sera un nombre de

o

à l27~dans les 7 bits disponibles.L'exposant sera donc exprimé en "excess 64 binary" notation. Le format des nombres est alors:1 7 8 31

[L,---,-' __

---JI

Les nombres auront une amplitude de:

2-6~Nb ~ (1_16- 6 ) 2 63

Cette représentation diffère de la précédente en ce sens, que la base sera 2 et non 'pas hexadécimale. Dans ce dernier cas l'amplitude des nombres est

augmentée,et essentiellement l'exposant. En effet en hexadécimal les 32 bits donnent une amplitude de:

16-64 ~Nb.~(1-16·-6) 16 63

ceci car les 24 bits de fraction donnent 6 bits hexadécimaux. Pour les nombres longs la base hexa-décimale donne un exposant, converti en décimal,de l'ordre de 10-78 à 1075•

4-Les nombres négatifs:

Ils seront comme précédement,représentés par leur complément à 2. La caractéristique restera toujours positive.

Addition en virgule flottantes

Nous savons que les nombres doivent etre prenormaliséso On ajoutera les caract~ristiques une fois qu'elles

seront égaleso Cela se fera en décalant l'un des nom-bresD Ce sera toujours la plus petite caractéristique

qui sera augmentée pour ètre égale à la plus grandeo Ceci parce-qu 'un nombre; dans l'accumulateur, peut être décalé à droite dans le multiplicateur-quotient sans perdre de bits, tandis qu'un décalage à gauche entraire les bits significatifs du nombre concerné.La procédure à suivre est donc la suivante:

On soustrait une caractéristique de ltautre.

-Si la différence est positive .. ce nombre ," résultat va dans un compteur de décalages et la partie fractionnaire du nombre soustrait va être déca-lée d'un nombre de positions égal au contenu du compteur.

-Si cette différence est négative, les deu:l~ nombres doivent être Interchangés.

Les deu,~ nombres sont:

B-D

"1_ S..,!I.I_7 ___

8 _ _ _ _ _ 1_6_-'SPlO,ll

Isi

7 8 16]

·Le registre K, de8 bits, sera le registre d'exposant du résultato Le nombre susceptible dGavoir sa partie

fractionnaire décalée est en B-D.

On va soustraire une caractéristique à l'autre. La caractéristique à soustraire doit être présenteê sous la forme de son complément à 20 Schématiquement le dêroulement des opérations es~ le suivantg

-SPIO-.:::>M

- [M] 7-t:;;>!{ -[B]7-DA

rien" -A->C -Comp2 C-bA" -A+l('-DA -A--c>I(, " f' 1('(0 on intervertit BD et SPo -l('-:>C -comp2 (c) -t:=>A -A-:;::,l(' -SPll-DA -D-i>SPll -A-:>D -SPlO-t>A -B--c>SPlO -A-.>B -décala de [BD] 24 de 1(' positions. l'addition peut. commencer'

- [SPlO] 7-t::> [M) 7 -M-:;:>I(,

1(' est la caractéristique finale -0-;> [M]7

-[M]7-C> [SPlO] 7

-0~[B]7

L'addition est alors celle de deuJc nombres de 24 bits, placés en SPlO,ll et BD. Il faudra donc pr~voir les indicateurs Ibf et autres tels qut.i.ls sont apparus dans l'étude de l'addition des entierso

Le résultat est en SPlO,ll pour la fraction.Il faudra la n~rmaliser éventuellement à 24 bitsoLs résultat définitif sera donné par:

-I(,-:::. [M] 7 -SPIO-DA

-A+M-DA

-A-,:;:;.SPIO Nombres négatifs

C'est comme dans le cas de la soustraction: On sai~ que cVest une addition qui se fait normalement, aprGs que-l'un des nombres ait été complementd.

rqultiplication en virgule flottante: Les rêgles sont les suivantes:

On normalise les nombres. Les caract~ristiques seront ajoutées et les fractions seront

multipli-~es comme des nombres de 24 bits. Ensuite il faut soustraire la valeur de la constante 64 à la car-actéristique. Pour cela on ajoute le complément à

deu~c: de 64, qui pourra par e~cemple être placé en permanence en mémoire scratch pad.

Au point devvue de l'exéclltion proprement dite,la multiplication s'éffectue comme nous l'avons vu pour des nombres entiers.. On conaidèreru ici que les nombres ont 24 bits ..

Supposons que les opérandes sont SPIO,ll et BD: -SPIO-~M - [M] 7.4-> 1(' -[B]7---;;>A -A+K-~K -Appe l de ( -64 ) ~l\1 -M->A

-~+A~K 9:lCpOsant du r~sultato

-0-;'-:' [B] 7 -0-;> [M] 7

- [M] 7-~ [SPIO] 7

La multiplication peut alors cooonenceroOn a la même séquence que celle faisant intervenir des /entiers longs,;

Les caractéristiques sont soustraites. Les nombres &tant nonnalisés les fractions sont divisées selon le micro-programme que nous avons vu pour les entiers.

Remarque sur les temps d'exécution des opérations:

En étudiant les micro-programmes,en sachant que le cycle de base est fixé à l/6.~

rs'

nous avons une idée du temps d'exécution des principales opérations arithmétiques et nous pouvons donc dresser le tableau suivant:en"tiers virgule flottante nb 4 ADD court 5 SUB nb 4.2 long nb 9 MOL court 50 nb 60 long nb 10 court DIV . " . 55 nb 60 long

On constate que le temps d'exécution de la multi-plication ou de la division en virgule flottante est moins important que le temps d'exécution d'une multiplication ou division avec des nombres longs. Cela peut" paraitre paradoxal mais s'explique par le fait que ·finalement , dans le premier cas l'op~r

ation s'éffectue sur 24 bits, au lieu de 32 dans le second.

Nouvelles caract~ristiques des registres: Registre M: l 2 8 Registres B et D: B A normalisation

b

nécalo [BD] 24On aura tous les indicateurs ne'céssaires à:.la multi-plication et à la division tels qu'ils sont apparus pour les opérations sur des nombres dè 12 bits.La différence est qu'il faut considérer que les nom-bres ont 24 bits (d'où les nouvelles bascules de

retenue,de normalisation)o

Nouvelles micro-instructionsl -[M]7->K - [B] 7->A. -K-~C -Décalage de

r

BD]24 -Décalage de [M]7 -Décalage de [M]16 -0-> [M]7 -0-> [B]7 - [M] 7->SP -A+[M]7-~A -K+A-~K -8->I(62

Chapitre 5

SIMULATION-D'UN