Brief announcement: Distributed shared memory based on computation migration

Texte intégral

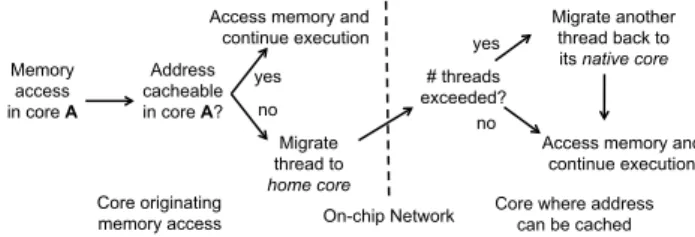

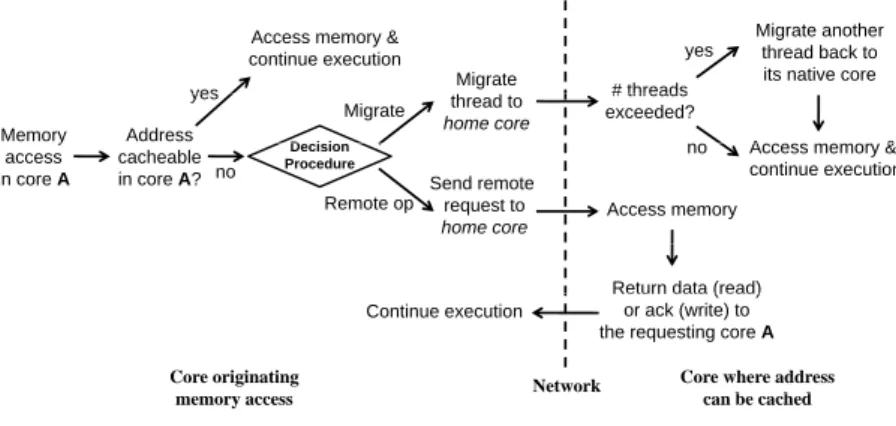

Figure

![Figure 2: The number of accesses to memory cached at non- non-native cores for a SPLASH -2 [13] OCEAN benchmark run, binned by the number of consequent accesses to the same core (the run length)](https://thumb-eu.123doks.com/thumbv2/123doknet/14184712.476910/3.892.98.421.79.253/figure-number-accesses-memory-splash-benchmark-consequent-accesses.webp)

Documents relatifs

Persistence. Since grid applications can handle large masses of data, data transfer among sites can be costly, in terms of both latency and bandwidth. In order to limit these

Persistence. Since grid applications can handle large masses of data, data transfer among sites can be costly, in terms of both latency and bandwidth. In order to limit these

Unité de recherche INRIA Rennes, Irisa, Campus universitaire de Beaulieu, 35042 RENNES Cedex Unité de recherche INRIA Rhône-Alpes, 655, avenue de l’Europe, 38330 MONTBONNOT ST

In the boolean case, the existence of an in situ program with 2n − 1 assignments for a bijective mapping is equivalent to the well known [2] rearrangeability of the Beneˇs network

Thread Guarded Memory Access Once the thread coprocessor memory space has been created the memory accesses must be guarded to ensure that they only addresses the abstract memory

configuration, as discussed in chapter 9. The resulting UP spectrum con- sequently shows unresolved features corresponding to the superposition of the signals coming from the

We evaluate the Worst-case response time of our Time-Triggered (WCRT TT ) solution, and compare it to 2 different implementations: (1) a single-core implementation, where all tasks

L’archive ouverte pluridisciplinaire HAL, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des