An Algorithm to Efficiently and Accurately Compute the Effective Capacitances of Interconnects Driven By Logic Gates

by

Marcin A. Strojwas

Submitted to the Department of Electrical Engineering and Computer Science in

Partial Fulfillment of the Requirements for the Degree of Master of Engineering in

Electrical Engineering and Computer Science

at the Massachusetts Institute of Technology

February 1, 2000

Copyright 2000 Marcin A Strojwas. All rights reserved.

The author hereby grants to M.I.T. permission to reproduce and

distribute publicly paper and electronic copies of this thesis

Author

Department of Electrical Enginering and Computer Science

February 1, 2000

Certified by

Jacob White

V/Thesis Supervisor

Accepted by

Arthur C. Smith

Chairman, Department Committee on Graduate Theses

MASSACHUSETTS INSTITUTEJUL

2 7 2000

ENG

An Algorithm to Efficiently and Accurately Compute the Effective Capacitances of Interconnects Driven By Logic Gates

by

Marcin A. Strojwas Submitted to the

Department of Electrical Engineering and Computer Science February 1, 2000

In Partial Fulfillment of the Requirements for the Degree of Master of Engineering in Electrical Engineering and Computer Science

ABSTRACT

This document contains the description of an algorithm for calculating the effective capacitance at a driving gate's output. The method applies for the cases of step and ramp waveforms at the driver's input. The algorithm proceeds in a two step manner. First, the driving gate fan-out is reduced to a H- model. This step is independent of the driving gate. Once a I model is calculated, the second part of the algorithm determines an effective capacitance. Included in this paper are the experimental results which indicate that results produced by this method are within 5% of effec-tive capacitance results generated by HSPICE which employs a significantly more costly method. Additionally, a closed form function is provided which approximates the effective capacitance to within 8%.

Thesis Supervisor: Jacob White

1 Introduction 1.1 Background

Improvements in integrated circuit technology have led to transistors with smaller feature sizes enabling faster switching speeds. Such decreasing feature sizes allow for denser chips with increased functionality while creating a need for finer interconnect line widths. As interconnect wiring shrinks, the interconnect resistance-per-unit-length scales up while interconnect capaci-tance-per-unit-length remains approximately constant due to fringing effects. Average metal lengths are not scaling down due to increasing interconnect densities. Therefore, the resistance of

on-chip metal interconnect is playing an increasingly dominant role in determining the timing behavior of logic gates.

The resistance and capacitance of interconnect is obtained through parasitic extraction. An extraction tool typically produces a distributed model for the interconnect. This distributed model consists of numerous capacitors connected to ground and resistors connecting the capacitors as shown in Fig. 1. Though a distributed interconnect model can capture the parasitic features of a wire in greater detail, a distributed model must be simplified into a model with a fixed number of parameters when performing an effective capacitance calculation. A H model serves this purpose, consisting of a resistor spanning between two capacitors connected to ground as shown in Fig. 2. Because a H model only has three parameters, R 1, C1, and C2, only certain features of the inter-connect loading can be modelled. In general, the use of a H model will prohibit the ability to accurately simulate the entire waveform at the driving gate's output. However, a H model can be crafted such that the delay through the driving gate and the slew at the output of the driving gate

are accurately captured. This feature makes the H model ideal for use in creating a digital abstrac-tion for a circuit and calculating effective capacitance..

T_

T

T T_

Fig. 1 A Distributed Interconnect Model

RI

C 1 C2

Fig. 2. A H model that captures the effects of interconnect parasitics.

1.2 Effective Capacitance

The term "effective capacitance" refers to the capacitance which is "seen" by a driving gate. The effective capacitance is less than the total load capacitance due to resistance shielding effects. The resistance of an interconnect wire from the driving gate to a load capacitance creates this resis-tance shielding effect. A useful example to consider for the purposes of understanding this effect involves considering the previously mentioned H model and examining the limiting cases of RI being zero and being infinite. If R 1 is zero, the capacitance seen by the driving gate is the sum of CI and C2. If RI is infinite, corresponding to an open circuit, then the capacitance seen by the driving gate is Cl. In this case, RI completely shields C2. In general, R 1 will be some finite, zero value because the wire resistance of the interconnect which RI models will be finite and non-zero. Therefore, as the interconnect resistance increases, the effective capacitance will be Cl plus

with a single capacitor, as shown in Fig. 3, such that the fifty percent output transition point in the effective capacitance model occurs at the same time as the corresponding point in the H model.

RI

C IC2 Ceff

Fig. 3. A -I model replaced by an effective capacitance model.

Calculating an effective capacitance is most crucial for driving gates whose drive resistance is less than the interconnect resistance. Under this condition, the effective capacitance will be sub-stantially less than the total capacitance. Due to the fact that gate delay is an increasing function of load capacitance, using an accurate effective capacitance model is essential to calculating gate delay. In this report, the gate delay is taken to be the time from which the input transition is fifty percent complete to the time at which the output transition is fifty percent complete. For short nets where the resistance of the interconnect is relatively small compared to the drive resistance of the gate, the effective capacitance does not differ too much from the total load capacitance. In this case, computing the effective capacitance is not worth the time required to perform the computa-tion during synthesis.

The effective capacitance for each gate is a function of the input transition time and the parameters of the I model. The nature of the synthesis process requires an extremely efficient algorithm to be embedded in the closed synthesis loop due to the number of times this algorithm must be executed. Furthermore, the parasitics which are available during synthesis are only rough estimates. Thus, there is no need for an exact calculation due to the error which exists between the parasitic estimation and the final parasitics present in the post-layout design. Theoretically, one

could precompute an effective capacitance table for each cell type. Though such a table could pro-vide the most efficient and accurate solution for effective capacitance modeling, the memory capacity required to store the necessary four dimensional table for each cell would be impractical. Thus a dynamic effective capacitance calculation is required.

2 The Effective Capacitance Calculation 2.1 Effective Capacitance Under Step Input

When a step input is applied to the gate, a transition will occur in the voltage at the gate's output. At one extreme, if this transition also occurs as a step input, the gate can be modeled by its Thev-enin equivalent consisting of a step input source (vs(t)) and a linear source resistance (Rs) as shown in Fig.4. A separate effective capacitance analysis must be performed for a rising gate tran-sition and for a falling gate trantran-sition because the source resistance is different for these two cases. This gate model drives the interconnect which is replaced with a 1- model.

Rs RI

+ CV C2

Vs (t)

-Fig. 4. A Thevenin equivalent for a gate driven by a step input loaded with a H model. For this case, the output voltage at the gate is given by:

VB(t) = V 0 + 1XsiRiC2 e St+ S2A X e s2t

sib2(si -S2) s2b2(s2-si)

where

b2 = RsRIC1C,

_ -b, ±(b) 2 -4b2 2b2

Solving for the time at which the output voltage at the gate crosses the fifty percent threshold voltage requires an iterative algorithm. However, this algorithm converges rapidly because the output voltage is a monotonically increasing or decreasing function. Let TH denote the time at which the gate output crosses the fifty percent threshold voltage. Once this time is known, one can model the load at the gate output with a single capacitor such that the trip time, the time at which the gate output voltage crosses the fifty percent threshold voltage, is identical to the trip time of the associated I model. Let Cstep denote the capacitance which matches the trip times in the two

models. Cstep can be computed as

T n Cstep = kiRs

where k1= ln(2).

At the other extreme, the gate can respond to the step input slowly. The lengthy transition time of the gate will cause the gate to charge up the entire load capacitance (Ctotal) while transitioning. Thus the effective capacitance, Cff, lies in the range between Cstep and Ctotal. Kahng and Muddu [3] propose employing an equation which uses the ratio of DLD to DNL, where DLD is the delay of the gate loaded with Ctotal and DNL is the delay of the gate under no load, to compute Ceff in this

5 Ceff = Ctotal - 5( Ctotal - Cstep) + ( Ctotal - Cstep ) x DD/DL

1 + (D LD)/I(DNL)

2.2 Effective Capacitance Under Ramp Input

The effective capacitance calculation for a gate driven by a ramp input parallels the calculation for a gate driven by a step input. For the case of a ramp input, the gate can transition no faster than the ramp time. Thus the analysis begins by finding the voltage waveform at the output of the gate driving a -I model if the gate is modeled by a ramp input source with a series source resistance as shown in Fig. 5. Rs R1 + Cl C2 Vs (t) T TR

-Fig. 5. A Thevenin equivalent for a gate driven by a ramp input loaded with a HI model. In this case, the voltage at the gate output loaded with a I model is

vx(t) = VO x t - Rs(Ci + C2) + 1 + siRIC2 t + 1 I + S2R1C2 x eS2t]

TR L (Sl) 2b2(S1 - S2) (S2) 2b2(S2-SI) J

for t <= TR, where TR is the ramp input rise time. For t > TR,

VX) = O X TV R + (I + s X XRC2) (1 -e-TRs1) X esIt +(I + S2RIC2) X (1 -e-TRs2) X eS2

where bi, b2, si, and S2 are as defined in the previous section. Again, this equation must be itera-tively solved to find the time at which the gate output voltage crosses the fifty percent threshold. Let this time be represented by TH.

As in the case of a step input, the next step is to find Cramp , a capacitor that could replace the H model without changing the time at which the gate output crosses the fifty percent threshold if the gate were replaced by the ramp input voltage source and a linear source resistor.

TH

Cramp = kR

C"'P k2Rs

For TH > TR, computing k2requires iteratively solving the following equation for k2:

0.5 = T (TRk2)/(T) -xek2

TR 9 k2

For Tr <= TR, computing k2 requires solving the following equation for k2:.

k2 = x (I - e-k2)

where

T R

cc = --0.5 x T

TH

For the region where Tn <= TR, an exact solution for k2 can be found iteratively. However, an approximate solution with an arbitrary accuracy can be obtained by noting that the equation for k2

is of the form k2= f(k2). Thus k2= f(f(f(f ...(initial-guess)))). Thus applying the function f to itself

n times will yield an nth order approximation for k2 and eliminate the need for an iterative solu-tion. Using the same functional form as in the case of a step input, Kahng and Muddu calculate Ceff as:

Ceff = Ctotal - 5(Ctotal - Cramp) + (Ctotal - Cramp) x +

1 + (DLD)/(DNL)

3 Calculating Drive Resistance

The drive resistance (RS) of each driver is a function of ramp input time (TR). For a fixed TR, the drive resistance is calculated by fitting a decaying exponential voltage waveform to the tail of the output at the driver:

vR x Ctotal

v(t) = Vdd Xe S

[2] shows that the above equation can best be evaluated at the fifty and ninety percent time points. From this it follows that the drive resistance can be calculated as:

Rs - tQg(Ctotal)-t50(Ctotal) Ctotal x ln(5)

The fifty percent time point (t50) is available via table lookup in a cell library and the ninety

per-cent time point (t90) can be computed by adding t50 and half of the slew time.

4 IF Model Reduction 4.1 Necessity of H Model Reduction

The above algorithm for computing an effective capacitance depends upon the ability to generate a H model which yields the same trip time as the generalized interconnect model. A H model was

chosen to model the interconnect because it is the simplest model which is suitable for effective capacitance calculation. In simplifying a distributed parasitic model, the driving point admittance of the simplified model must be set according to the driving point admittance as seen looking into the distributed model. A H model has three parameters allowing the first three moments of the driving point admittance of the distributed model to be captured. A distributed model cannot immediately be reduced to a one parameter model, consisting of a capacitor. Such a reduction would only allow the first moment of the distributed model to be captured. Thus, the capacitance to which the distributed network would be reduced is the total capacitance. A two parameter model consisting of a resistor in series with a capacitor, as shown in Fig. 6, is also insufficient.

Such a model yields unacceptable results for effective capacitance calculation because it allows for the possibility of the effective capacitance to be negative. This is caused by the lack of a capac-itance connected directly to the output of the driving gate.

Rs RT RC-mcdeb

Cl.

Vs (t) -L - - -

-Fig. 6. A Thevenin equivalent for a gate driving an RC model.

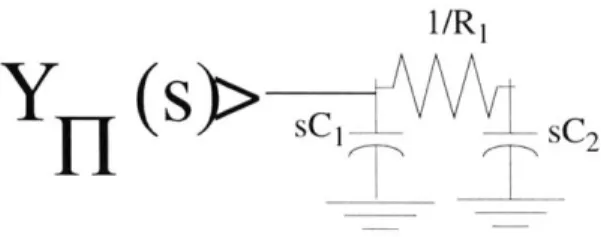

The first step in calculating a H model is to find the driving point admittance (YI(s)) for a generalized H model as shown in Fig. 7.

/R

Y (S) sc,- & -SC

2

Fig. 7. A generalized H model for finding the driving point impedance.

Y (s) = s C

SC1+sRI C2

Using the expansion

= 1-x+x2+...

1 +x

YH(s) can be written as

Y (s) = s(C 1 + C2) - s2(R 1 C22) + s3 (R 1)2(C2)3) +

Only the first three moments are necessary for forming a H model. The three H model parameters are chosen such that the first three moments of the driving point admittance of the original net-work are equal to the first three moments in the above expression.

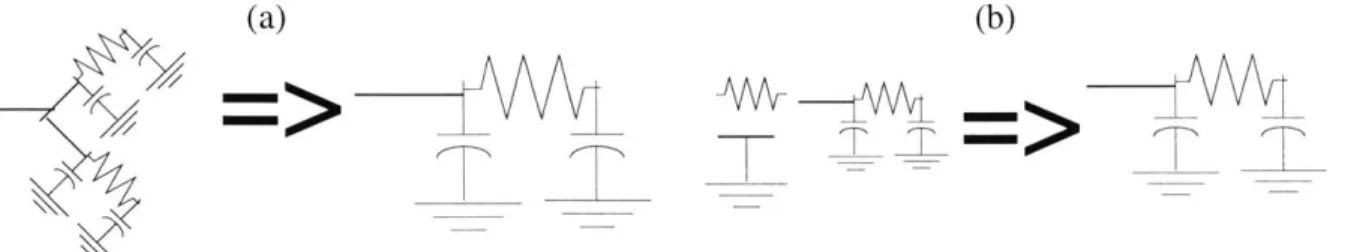

Finding a H model for an arbitrarily complex branching network can be achieved with the aid of two expressions for forming new H models. These two expressions dictate how a new H model

should be formed from two H models in parallel and how a new H model should be formed when replacing a wire with an evenly distributed resistance and capacitance driving a previously formed H model. These two types of processes for forming equivalent H models are illustrated in Fig. 8.

(a) (b)

/W -t

/~l T ~ TT

Fig. 8. (a) Replacing two H models in parallel with a new H model. (b) Replacing a wire in series with an existing H model by a H model.

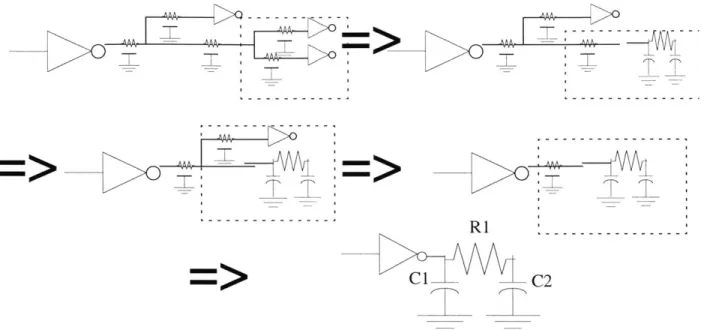

A fan-out network can be viewed as a tree with the root at the output of the driving gate, the leaves at the gates being driven, and nodes occurring at every interconnect branching point. A H model can be formed at every node to replace the subtree rooted at that node using the two types of H model collapsing processes described above. Thus, by forming H models at each node of the tree beginning from the leaves and working up to the root, a H model can be formed which repre-sents the entire fan-out network. An example of this process is depicted in Fig. 9.

LL%

-- -- -- - A--ALA:

R1Z RI Cl_ C2Fig. 9. The process of forming H models at each node (interconnect branching point) in order to arrive at a H model for the entire fan-out network. In each step shown above, a H model replaces the RC elements in the previous dashed box using the two processes depicted in Fig.8.

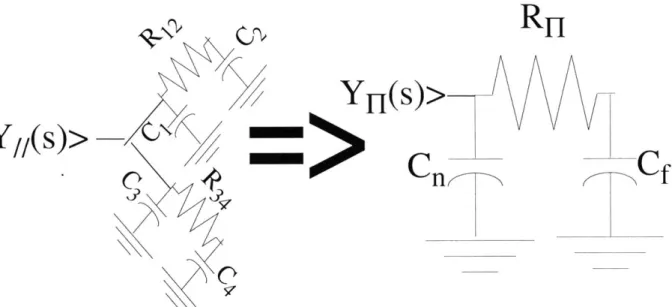

4.2 Collapsing Two H Models in Parallel

Finding a H model to replace two H models in parallel requires finding the first three moments of the admittance as seen looking into two H models in parallel. The new H model which will replace these two H models must have an input admittance with the same first three moments. Fig.

RH

__C>

-C

C

YH(s)>-en

Cf

Fig. 10. A schematic representation of creating a H model from two H models in parallel.

Y//(s) is easily calculated as the sum of the admittances of two H models.

Y (s) = (C1 + C2 + C3 + C4)s-(R12C22 + R3 4 C42)s2 + I(R 122C23 +

By equating the first three moments of Y//(s) with the first three moments of YH(s), RH, Cf, and Cn are calculated as follows,

(R 1?2C?3 + R3 42C43 N2

(R 12 C22+ R34C42)3

R342C43)S3+...

00

Cf = C92+ R34C42)2 S ( R 1'22C2 3 + R3 42C43 )

Cn C+C+C+C4-Cf

This set of algebraic equations is essential to generating H models by traversing up a tree because the new H model parameters do not depend on any higher order moments of the branches. In other words, forming a H model at a point where a network branches only depends upon the H model parameters representing each branch.

4.3 Collapsing a Wire in Series with a H model

The second essential procedure for collapsing any fan-out into a single H model requires replac-ing a wire drivreplac-ing a H model by a new H model. Fig. 11 displays the namreplac-ing conventions employed in the following derivation.

R

1 2

R

RH

Yn(s)>

Yx~)>--i

C1Y

-C2

C

C

>

The wire resistance (R) and the wire capacitance (C) are assumed to be continuously and evenly distributed along the wire. Y,(s), the input admittance for a wire driving a H model, can be calcu-lated by replacing the continuously distributed RC element by a series of N resistors spanning between N grounded capacitors where the magnitudes of the resistances and capacitances are R/N and C/N respectively. In the limit as N tends to infinity, Y,(s) is obtained. Yx(s) can be written as,

Yx(s) = mls+m 2s2+m 3s3 +... where, mi = C+C+Cn f m2 = RCf2 +R(Cn +Cf) 2 + RC(Cn + Cf) + 3RC2 and m3 = Rn2Cf3+ C3R2+ R2C2(Cn +Cf)+2RR (Cn + Cf)(Cf) 2 + 4R2C(Cn + C) 2 + R2(Cn + C) 3+ R RCCf 2

By equating ml, m2, and m3 with the first three moments of YI(s), R12, C2, and C1 are calculated

R = (m3 )2

12 (M2)3

2 (M3)

C1 - rn-C 2

As in the case of collapsing two 11 models in parallel, a H model representation for the net-work being driven by the wire contains all of the information necessary for creating a new H model. This fact ensures that no accuracy is lost in traversing up the tree while forming H models at each node. In the case of an open-ended wire (Cn = 0, R = 0, and Cf = 0), the H model equa-tions reduce to C1 = (1/6) C, C2 = (5/6)C, and R12 = (12/25)R. This set of equations also applies when a wire with resistance (R) and capacitance (C) is driving a gate with an input capacitance of Cin, and C >> Cin or R is sufficiently large. Otherwise, the gate being driven by the wire should be modeled with a H model where Cf = Cin, Cn = 0, and RH = 0.

This section explores the potential for developing an iterationless approach for calculating effective capacitance. Empirically, the following formula approximated the effective capacitance to within 8%:

1

Ceff = Cnear + Cfa r

c + 8.5 x Rpi2 x Cfar Rs x Tramp

An intuitive understanding of this formula can be acquired by examining the limiting cases. In the limit as Tramp tends to infinity, the entire load capacitance will be charged during the input transi-tion, so Ceff = Cnear+Cfar. The limit as Rpi tends to infinity yields a value of Ceff = Cnear because the resistor behaves as an open circuit. The limit as Rpi tends to zero yields a value of Ceff = Cnear + Ctotal because the resistor behaves as a short circuit. This option for approximat-ing Ceff provides the efficiency which a synthesis tool requires while preservapproximat-ing a sufficient accu-racy as observed in Table 1.

6 Experimental Results

This section contains a comparison of the results of the effective capacitance algorithm presented in this report, the empirical model, and the effective capacitance calculated from SPICE simula-tions. The effective capacitance algorithm presented in this paper determines an effective capaci-tance by matching the fifty percent output delay points of the two models. The same criteria is

TABLE 1: Comparison of Ceff Results

Rs Cnear (Q) (fF) 778 200 778 200 778 200 778 200 778 200 778 350 778 300 778 100 778 50 119050 119050 650 200 650 200 372 200 Rpi (Q) 50 100 200 400 600 200 200 200 200 200 400 200 100 100 Cfar (fF) 200 200 200 200 200 50 100 300 350 50 50 200 200 200 Tramp (ns) 1.5 1.5 1.5 1.5 1.5 1.5 1.5 1.5 1.5 1.0 1.0 1.0 1.0 1.0 372 200 300 200 1.0*HSPICE simulations performed for

Ceff(algorithm) %error (fF) 395 390 381 362 338 399 395 357 342 99 99 367 386 391 367

(%)

Ceff(model) %error Ceff(HSPICE)* (fF) -.70 399 -1.66 397 -2.86 389 1.01 362 -3.81 331 .01 399 -.45 397 -.61 376 -1.89 368 3.69 99 3.83 97 -3.28 381 -1.11 395 -.59 391 3.79 342 (%) (fF) .32 .03 -.76 1.17 -5.64 .07 .04 4.70 5.33 3.43 2.63 .54 1.26 -.44 -3.47 398 397 392 358 351 399 397 359 349 96 95 379 390 393 354 a 0.6 ptm technology 7 Conclusions

The techniques proposed in this paper for computing effective capacitance could be embedded in a tight synthesis-analysis loop for gate delay estimation during synthesis. This approach is consid-erably faster than methods employed by static timing analysis tools, yet produces effective capac-itance estimates which are within 5% of those produced by SPICE. For further efficiency with minimal loss of accuracy, the effective capacitance can be calculated with an empirical model. Independent of the effective capacitance calculations presented in this paper, the H model reduction technique provides a methodology to generate H models using only algebraic equations without any loss of accuracy.

REFERENCES

[1] C. Alpert, A. Devgan, S. Quay. "Buffer Insertion with Accurate Gate and Interconnect Delay Computation," DAC 99. pp 479-484.

[2] F. Dartu, N. Menezes and L. Pillegi. "Performance Computation for Precharacterized

CMOS Gates with RC Loads," IEEE Transaction on Computer Aided Design of Inte-grated Circuits and Systems.Vol. 15, No. 5, May 1996.

[3] A. B. Kahng and S. Muddu, "New Efficient Algorithms for Computing Effective Capacitance," ISDR 1998, pp 147-151.