Studiengang Systemtechnik

Vertiefungsrichtung Power & Control

Bachelorarbeit

Diplom 2019

Raphael Gruber

Dozent/in P h i l i p p e Ba r r a d e Experte/Expertin R o d o l f o H o r t aDatum der Abgabe des Schlussberichts

Seite 1

Es handelt sich um den Originalbericht des/der Studierenden.

Ziel des Projekts

Die Implementierung eines Regelungsalgorithmus auf einem digitalen Kontroller (POETIC), um einen dreiphasigen Spannungswechselrichter (AFE) zu regeln, sowie die Erstellung der notwendigen Schaltkreise für die Vor- und Entladephasen.

Methoden | Experimente | Resultate

Um den C-Code des Regelungsalgorithmus und der Zustandsmaschine für einen dreiphasigen Spannungswechselrichter zu implementieren und anschliessend diesen auf dem POETIC-Mikroprozessor zu integrieren, wird das Prinzip der Regelung in Matlab/Simulink mit einem simulierten AFE in PLECS getestet. In diesem Projekt wird eine neue Methode getestet, um externen C-Code in den Echtzeitsimulator Typhoon HIL (hardware-in-the-loop) zu importieren. Der Vorteil dieser entwickelten Methode ist, dass dieser C-Code direkt ohne grosse Veränderungen auf dem POETIC-Mikroprozessor integriert werden kann. Dieser Arbeitsschritt konnte erfolgreich durchgeführt werden und der C-Code konnte mühelos in POETIC integriert werden. Als nächster Schritt wurde der AFE in Typhoon simuliert und mit dem realen POETIC-Mikroprozessor geregelt. Mit verschiedenen durchgeführten Tests konnte der in Typhoon simulierte AFE eine Leistung von 20kVA bidirektional zwischen dem AC-Netz und dem 700V DC-Bus austauschen. Aus Zeitgründen konnte der reale AFE nicht an POETIC angeschlossen werden, jedoch muss lediglich die Verkabelung umgesteckt werden und die Hardware installiert werden.

Regelung eines dreiphasigen

Spannungswechselrichters

Diplomand/in

Raphael Gruber

Diplomarbeit

| 2 0 1 9 |

Studiengang Systemtechnik AnwendungsbereichPower & Control

Verantwortliche/r Dozent/in

Dr Philippe Barrade philippe.barrade@hevs.ch

Grobes Blockschaltbild des Regelungsalgorithmus

oben: PLL-Schaltung (Phase-locked loop)

unten: Stromregelung im dq-Referenzsystem

Spannungswechselrichter (AFE) mit montierter POETIC-Interface Platine. uvw αβ αβ dq PI‐Regler 1/s ua(α) ua(β) ua(q) Θ = ωt uCN uBN uAN + ‐ ω 0 uvw αβ αβ dq i(α) i(β) i(q) ib PI‐Regler + i(d)_ref PI‐Regler + i(q)_ref Lω ‐ ‐ Lω i(d) ua(d) + + + + + ‐ dq αβ αβ uvw ub_ref ua(d)_ref ua(q)_ref sc al e to mo d u la to r

Objectif du pro jet

Implémentation d’un algorithme de réglage pour un contrôleur digital (POETIC), dans le but de réguler un onduleur triphasé (AFE), ainsi que de contrôler les circuits nécessaires à la précharge et la décharge.

Méthodes | Expérie nces | Résultats

Afin d’implémenter du C-Code pour le réglage et la machine d’état dédiés à un onduleur de tension triphasé et puis leur intégration sur le POETIC-microprocesseur, le principe du réglage est testé de manière conventionnelle en Matlab/Simulink avec un onduleur simulé en PLECS. Une nouvelle méthode est testée, qui permet d’importer et pré-tester le C-Code externe dans le simulateur temps réel Typhoon HIL (hardware-in-the-loop). L’avantage de cette nouvelle méthode est que le réglage peut être intégré sur le microprocesseur sans grand changements. Le déport du C-Code sur le microprocesseur a été effectuée aisément et avec succès. Dans l’étape suivante, l’AFE est simulé sous Typhoon, réglé par le POETIC-microprocesseur réel. En exécutant différents tests, l’AFE simulé est capable de transférer de manière bidirectionnelle une puissance de 20kVA entre un bus 700V DC et le réseau AC. Aux raisons de temps, l’AFE réel n’a pas pu être connecté avec le POETIC. Il faut seulement changer le câblage pour mettre en service l’AFE réel.

Regelung eines dreiphasigen

Spannungswechselrichters

Dip lômant

Raphael Gruber

Trava il de dip lôme

| é d i t i o n 2 0 1 9 |

Filière

Systèmes industriels

Domaine d’application

Power & Control

Professeur responsable

Dr Philippe Barrade philippe.barrade@hevs.ch

Schéma bloque du réglage En haut: circuit du PLL (Phase-locked loop)

En bas: régulation du courant en système de référence dq

L’onduleur triphasé (AFE) avec la platine POETIC-Interface. uvw αβ αβ dq PI-Regler 1/s ua(α) ua(β) ua(q) Θ = ωt uCN uBN uAN + - ω 0 uvw αβ αβ dq i(α) i(β) i(q) ib PI-Regler + i(d)_ref PI-Regler + i(q)_ref Lω -Lω i(d) ua(d) + + + + + -dq αβ αβ uvw ub_ref ua(d)_ref ua(q)_ref sc ale to m o d u la to r

Seite 4

Inhalt

1

Einleitung ... 9

2

Pflichtenheft ... 10

3

Aufgabenaufteilung ... 11

4

Beschreibung ... 13

4.1 AFE (Active Front End) ... 13

5

Regelungstechniken & Validierung des Prinzips in Matlab/Simulink ... 15

5.1 Funktionsprinzip des AFE’s, [21] ... 15

5.2 Theorie ... 15

5.2.1 Einleitung ... 15

5.2.2 Unterschwingungsverfahren [4][21] ... 15

5.2.3 Regelungsschleifen, [19][20][22] ... 17

5.3 Zu implementierende Sicherheiten für den AFE ... 21

5.4 DC-AC Vorladephasen und Entladung der DC-Kondensatoren ... 22

5.4.1 Entladung der DC-Kondensatoren ... 22

5.4.2 DC-AC Vorladephasen ... 22

5.4.3 Dimensionierung des Preload-Widerstands ... 24

5.5 Tests: Kontroller (Matlab/Simulink)-Konverter (PLECS-Blockset) ... 27

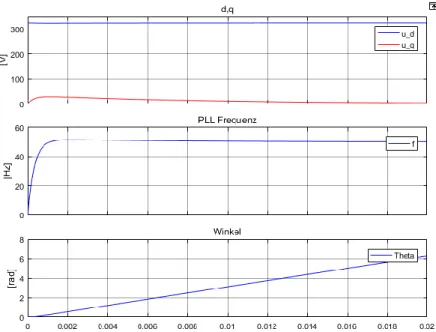

5.5.1 Simulink-Funktionsblöcke (Transformationen und PLL) ... 27

5.5.2 Simulink-Funktionsblöcke (Stromregelung) ... 28

5.5.3 Matlab-Funktionsblöcke (Closed-loop & Zustandsmachine) ... 33

5.5.4 Ergebnisse ... 36

6

Kontroller (Typhoon)-Konverter (Typhoon) ... 37

6.1 Ablauf... 37

6.2 C-Code in Typhoon importieren ... 37

6.2.1 «Advanced C function» Block ... 37

6.2.2 Einschränkungen ... 40

6.3 Simulationen ... 41

6.3.1 Sample-Time Auswahl des PLL-Blocks ... 41

6.3.2 Filterung der Eingangsströme & Reduzierung der Totzeit ... 43

6.3.3 BOOTING der Zustandsmaschine ... 43

6.3.4 Preload- und Entlade-Vorgang) ... 44

6.3.5 PLL mit harmonischen Störungen ... 45

Seite 5

6.3.7 Optimierung der Stromregler ... 47

6.3.8 Komplette Zustandsmaschine ... 47

6.3.9 Typhoon Panel ... 49

6.3.10 Ergebnisse ... 50

7

Kontroller (POETIC)-Konverter (Typhoon) ... 51

7.1 Interface (POETIC-AFE) ... 51

7.2 Analoge Messungen ... 53

7.3 Verstärkungen der Messungen (POETIC mit AFE) ... 53

7.3.1 Verstärkungen der Messungen (POETIC mit Typhoon) ... 54

7.3.2 ADC (Prinzip) ... 56

7.3.3 Typhoon Scaling ... 58

7.3.4 Arbeitsweise des ADC ... 59

7.4 POETIC-Boards (FO-, DI/DO-, Relay-Board) ... 60

7.5 Auswahl der POETIC-Boards ... 61

7.6 Typhoon-Schaltung und DSP Control Center ... 62

7.7 Tests & Ergebnisse ... 64

8

Kontroller (POETIC)-Konverter (AFE) ... 66

9

Arbeitsplan und Zeitmanagement ... 66

10

Schlussfolgerung ... 66

11

Bibliographie ... 67

12

Anhänge ... 70

Tabellenverzeichnis

Tabelle 1: Etappen der verschiedenen Simulationstools ... 12Tabelle 2: Hautpspezifikationen des AFE Moduls, (nachgeschlagen aus [3] S.9) ... 13

Tabelle 3: Übersicht der Referenzsysteme ... 17

Tabelle 4: Übersicht der verschiedenen Widerstandsvarianten des Preload-Widerstands 𝑅𝑃𝑟𝑒𝑙𝑜𝑎𝑑_𝑡𝑜𝑡 ... 25

Tabelle 5: Spannungswerte der DC-Bus Kondensatoren beim Preload. *Diese Zeitpunkte werden in der Zustandsmaschine in POETIC zur Überprüfung des Preload-Vorgangs verwendet. ... 26

Tabelle 6: Konstanten in POETIC für die Kontrolle des Preload-Vorgangs ... 27

Tabelle 7: Verwendetet Simulationsparameter ... 29

Tabelle 8: Übersicht der Etappen: Erweiterung des Konverters und der Regelung in Typhoon ... 37

Tabelle 9: Übersicht der Testschritte für die Optimierung der PLL-Schaltung ... 45

Tabelle 10: Übersicht der Testschritte für die Dimensionierung des Uq-Filters ... 46

Tabelle 11: Übersicht der Testschritte für die Optimierung der Stromregelung. Verwendete PLL-Parameter: (Kp=0.8, Ki=80*T_fast=0.004) ... 47

Tabelle 12: verwendete Fehlermeldungen in Typhoon und in POETIC ... 48

Seite 6

Tabelle 14: Open collector Schaltung, (Quelle alte Diplomarbeit, S. 54, bearbeitet) ... 52

Tabelle 15: Übersicht der Sensoren und ihre Verstärkungen. (R_Shunt=130Ω) ... 53

Tabelle 16: Zusammenfassung der berechneten Typhoon Skalierungen und ihre verwendeten analogen Ausgänge in Typhoon ... 58

Tabelle 17: verwendete Abkürzungen in alphabetischer Reihenfolge ... 71

Tabelle 18: verwendete Softwareprogramme ... 71

Tabelle 19: Liste der Verwendeten Geräten ... 72

Tabelle 20: Stecker J29 des AFE, (nachgeschlagen aus [3] S. 21) ... 74

Tabelle 21: Stecker J9 des AFE[2], (nachgeschlagen aus [3] S. 20) ... 75

Tabelle 22: Liste mit Einschränkungen für in Typhoon importierten C-Code. ... 86

Abbildungsverzeichnis

Abbildung 1:DC-Bus der Schule ... 9Abbildung 2: AFE von teknoCEA, (nachgeschlagen aus [3] S.1) ... 9

Abbildung 3: POETIC mit verschieden Modulkarten ... 10

Abbildung 4: (1) connecteur optique, (2) connecteur SUB-9, (3) connecteur RJ45, (4) connecteur SMA, (nachgeschlagen aus [2] S. 12) ... 10

Abbildung 5: Kontroller in Typhoon, Konverter in Typhoon ... 12

Abbildung 6: OBEN: Kontroller in POETIC, Konverter in Typhoon, UNTEN: Kontroller in POETIC, Konverter: realer AFE ... 12

Abbildung 7: vereinfachtes Funktionsschema des AFE ... 13

Abbildung 8: Funktionsschema des AFE ... 15

Abbildung 9: PLL (Phase-locked loop), [7] S.11 ... 17

Abbildung 10: Prinzipschema der Regelung ... 18

Abbildung 11: Prinzipschema der Regelung (Beispiel) ... 18

Abbildung 12: Prinzipschema der Regelung des AFE ... 19

Abbildung 13: Komplettes Blockschema der Regelungsschleifen, [7] S.13 ... 21

Abbildung 14: Lade- und Entladeschema des AFE, (nachgeschlagen aus [3] S. 15, (bearbeitet))... 22

Abbildung 15: Verschiedene Variante um die DC-Bus Kondensatoren aufzuladen ... 23

Abbildung 16: LTspice Schema der Preload-Schaltung ... 25

Abbildung 17: Die Leistung am Preload-Widerstand ... 26

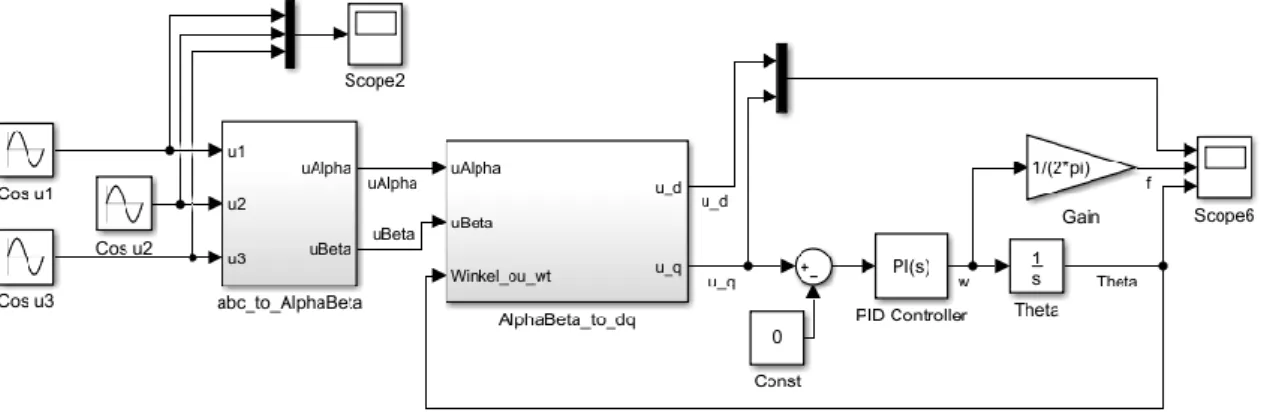

Abbildung 18: PLL-Schaltung ... 27

Abbildung 19: Eingangsspannung, Amplitude 325V ... 28

Abbildung 20: PLL-Verhalten mit (Kp=10, Ki=1'100), Oben: dq-Komponenten, Mitte: PLL Frequenz, unten: Winkel Theta ... 28

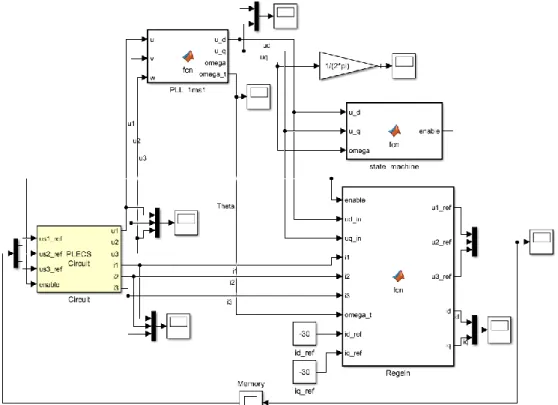

Abbildung 21: links: PLECS Circuit (AFE) Closed-Loop, Mitte: Stromregelung im dq-Referenzsystem, rechts: Skalierung der Referenzspannungen ... 30

Abbildung 22: PLECS Circuit (Leistungsschema AFE), PWM Generierung durch Vergleich des Dreiecksignals und des Sinusreferenzsignals... 30

Abbildung 23: Phasenspannungen und Phasenströme ohne Filter ... 31

Abbildung 24: Referenzspannungen für die PWM-Generierung ... 31

Abbildung 25: PLECS Circuit (Leistungsschema AFE) mit Filter parallel zur Last ... 32

Abbildung 26: Phasenspannungen und Phasenströme mit Filter parallel zur Last ... 33

Abbildung 27: Referenzspannungen für die PWM-Generierung ... 33

Abbildung 28: PLECS Circuit (Leistungsschema AFE), AC-Netz mit Schalter S1,S2 und S3 zuschaltbar ... 34

Abbildung 29: Closed-Loop mit PLL-Block (slow 1ms), Zustandsmaschine-Block (slow 1ms), Stromregelung-Block (fast 50µs) ... 35

Abbildung 30: Auf 0.0 geregelte Uq-Komponente, ermittelte PLL-Frequenz und ermittelter Winkel Theta ... 35

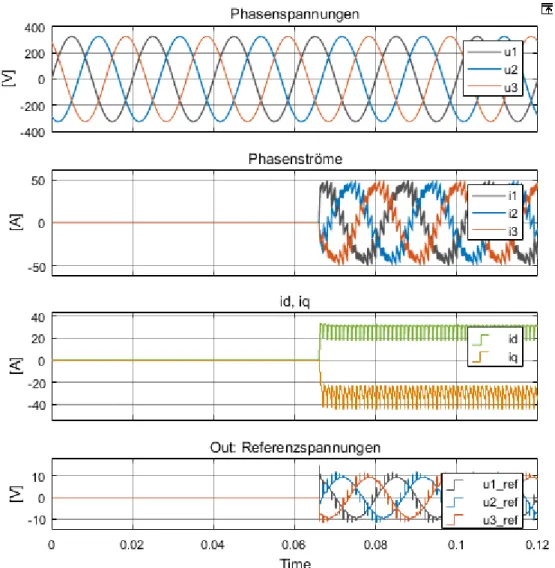

Abbildung 31: Das Prinzip funtkioniert, jedoch enthalten die Phasenströme und ihre dq-Kompenenten Schwingungen... 36

Seite 7

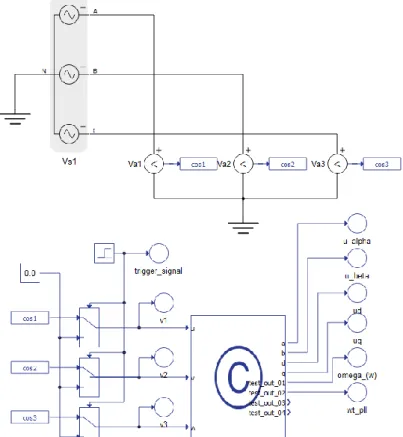

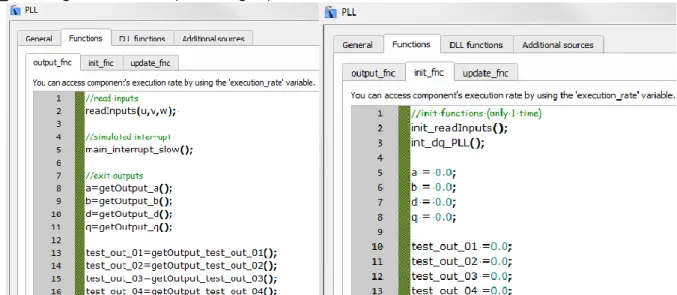

Abbildung 32: Der «Advanced C function» Block, in welchem der C-Code der PLL-Schaltung aufgerufen wird. . 38

Abbildung 33: Angabe des Pfades des zu importierenden C-Codes (.c und .h files) ... 38

Abbildung 34: Deklarierung der Eingangsparameter im «Advanced C function» Block ... 38

Abbildung 35: Deklarierung der Ausgangsparameter im «Advanced C function» Block ... 39

Abbildung 36: links: Das Tab «output_fnc» wird mit der Block eigenen Zykluszeit (T_Sample) durchlaufen, rechts: Das Tab «init_fnc» wird nur am Start ausgeführt. ... 39

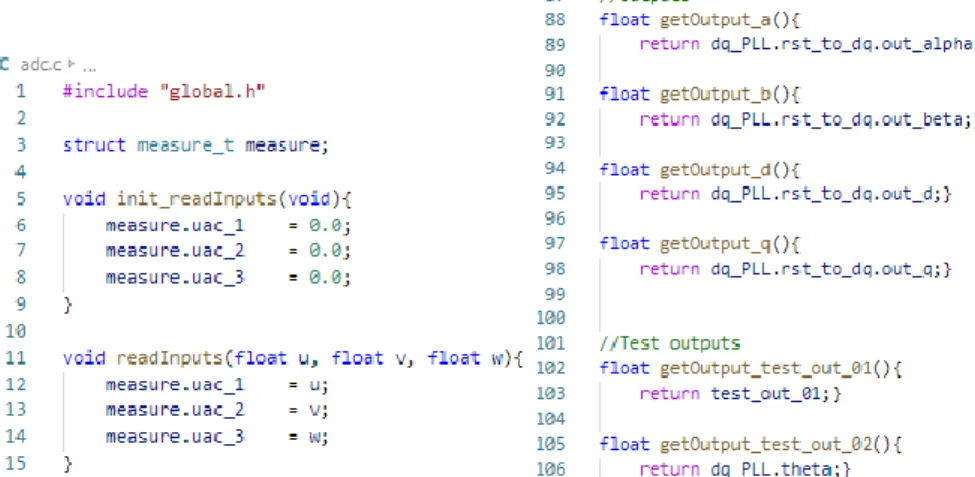

Abbildung 37: Ausschnitte vom C-Code: rechts: Funktionen um die Ausgangsparameter auszugeben, links: Init-Funktion und Init-Funktion um die Eingangsparameter zu lesen. ... 40

Abbildung 38: Funktion des Simulierten Interrupts, in diesem Interrupt können die verschieden Funktionen des C-Codes aufgerufen werden. ... 40

Abbildung 39: Abszisse: [20ms/div], OBEN LINKS: Phasenströme [10A/div], OBEN RECHTS: AC-Netz [100/div], UNTEN LINKS: generierte Referenzspannungen [100V/div], UNTEN RECHTS: rot: ud [100V/div], grün: uq [100V/div], blau: id [20A/div], gelb: iq [20A/div] ... 42

Abbildung 40: Abszisse: [20ms/div], OBEN LINKS: Phasenströme [10A/div], OBEN RECHTS: AC-Netz [100/div], UNTEN LINKS: generierte Referenzspannungen [100V/div], UNTEN RECHTS: rot: ud [100V/div], grün: uq [100V/div], blau: id [20A/div], gelb: iq [20A/div] ... 42

Abbildung 41: Abszisse: [20ms/div], OBEN LINKS: Phasenströme [10A/div], OBEN RECHTS: gelb: omega_(w) [100rad/s/div], AC-Netz [100/div], UNTEN LINKS: generierte Referenzspannungen [100V/div], UNTEN RECHTS: rot: id [20A/div], grün: id [20A/div], blau: ud [100V/div] ... 43

Abbildung 42: Ausschnitt der Typhoon-Schaltung: links: Preload-Widerstand, rechts: Discharge_Relais ... 44

Abbildung 43: Abszisse: [1s/div], grün: externe Busspannung Vdc [200V/div], rot: Spannung Udc über den Kondensatoren [200V/div] ... 44

Abbildung 44: Typhoon Panel: Ersetzt das User-Interface von POETIC (DSP Contorl Center) ... 49

Abbildung 45: Interface zwischen POETIC und AFE ... 51

Abbildung 46: Sammelmeldung der Fehlersignale als open-collector Schaltung (ODER-Schaltung), (Quelle AFE datasheet, S. 13) ... 52

Abbildung 47: Blockschaltbild AFE-POETIC... 53

Abbildung 48: POETIC an Typhoon angeschlossen... 54

Abbildung 49: Störungsanfällige Messung, 10kΩ Widerstände befinden sich auf dem Typhoon-Interface ... 55

Abbildung 50: Störungsrobuste Messung, 10kΩ Widerstände können je nach Anwendung mit Jumper überbrückt werden ... 56

Abbildung 51: ADC Eingangssignal wird in einen digitalen 12Bit Zahlenwert umgeformt ... 56

Abbildung 52: Das Offset wurde wieder entfernt ... 57

Abbildung 53: Auslesung der analogen Messsignale ... 59

Abbildung 54: Mikroprozesser (DSP) kommuniziert über den Backplane Bus mit den verschiedenen POETIC-Boards ... 60

Abbildung 55: links: 2xDI SUB-9 Stecker des AFE’s, rechts: DI und DO SUB-9 Stecker des POETIC ... 61

Abbildung 56: Ausschnitt der CPLD-Logik: Pin Zuweisung des DI/DO Board 0 ... 62

Abbildung 57: Verwendetes DSP Control Center (User-Interface) ... 63

Abbildung 58: LINKS: Pd=14’500W (Id≈30Ap), Pq=0var (Iq≈0Ap), RECHTS: Pd=-14’500W (Id≈-30Ap), Pq=0var (Iq≈0Ap) ... 64

Abbildung 59: LINKS: Pd=14’500W (Id≈30Ap), Pq=14’500var (Iq≈30Ap), RECHTS: Pd=14’500W (Id≈30Ap), Pq=-14’500var (Iq≈-30Ap) ... 65

Abbildung 60: Raumzeiger, [5] S.295 ... 76

Abbildung 61: Raumzeigers in kartesischer Form, [5] S.296 (bearbeitet) ... 77

Abbildung 62: rotierendes dq-Referenzsystem, [7] S.10 (bearbeitet) ... 78

Abbildung 63: Curser @ t=5τ=6.75s ... 81

Abbildung 64: Die DC-Bus Spannung erreicht nicht ganz 700Vdc (@t=5τ:U_Kondo=685.3V, berechnet @t=∞:U_Kondo=689V) ... 81

Abbildung 65: Der Stromverlauf durch den Preload-Widerstand (@t=5τ:I_DC=14.7mA, berechnet @t=∞:I_DC=10.45mA) ... 81

Seite 8 Abbildung 67: links : Inverse Park Transformation (dq >> αβ), rechts : Inverse Clarke Transformation (αβ >>

uvw) ... 82

Abbildung 68: Pythagoras für die Amplitudenberechnung ... 82

Abbildung 69: Abszisse: [20ms/div], OBEN LINKS: grün: u_alpha [100V/div], rot: u_beta [100V/div], OBEN RECHTS: grün: omega_(w) [100rad/s/div], UNTEN LINKS: wt_pll [2rad/div], UNTEN RECHTS: rot: ud [100V/div], grün: uq [100V/div] ... 87

Abbildung 70: Abszisse: [20ms/div], OBEN LINKS: grün: u_alpha [100V/div], rot: u_beta [100V/div], OBEN RECHTS: grün: omega_(w) [100rad/s/div], UNTEN LINKS: wt_pll [2rad/div], UNTEN RECHTS: rot: ud [100V/div], grün: uq [100V/div] ... 87

Abbildung 71: PLL und Stromregelung (Auswahl PLL Sample-Time) ... 88

Abbildung 72: Abszisse: [20ms/div], OBEN LINKS: Phasenströme [10A/div], OBEN RECHTS: AC-Netz [100/div], UNTEN LINKS: generierte Referenzspannungen [100V/div], UNTEN RECHTS: rot: ud [100V/div], grün: uq [100V/div], blau: id [20A/div], gelb: iq [20A/div] ... 89

Abbildung 73: LINKS: ohne Filter (Kp=1.2, Ki =80*T_fast=0.004) keine Harm., RECHTS: ohne Filter (Kp=1.2, Ki=80*T_fast=0.004) 5. Harm 0.1pu ... 90

Abbildung 74: LINKS: PT2 100Hz (Kp=0.8, Ki =80*T_fast=0.004) keine Harm., RECHTS: PT2 100Hz (Kp=0.8, Ki=80*T_fast=0.004) 5. Harm 0.1pu ... 90

Abbildung 75: LINKS: PT2 100Hz (Kp=0.8, Ki =80*T_fast=0.004) 7. Harm 0.1pu., RECHTS: PT2 100Hz (Kp=0.8, Ki=80*T_fast=0.004) 3. & 5. & 7. Harm 0.1pu ... 91

Abbildung 76: ** LINKS: PT1 10Hz (Kp=0.8, Ki =80*T_fast=0.004) 3. & 5. & 7. Harm 0.1pu., RECHTS: PT1 100Hz (Kp=0.8, Ki=80*T_fast=0.004) 3. & 5. & 7. Harm 0.1pu ... 92

Abbildung 77: LINKS: kein Filter (Kp=0.6, Ki =160*T_fast=0.008) keine Harm., RECHTS: kein Filter (Kp=4, Ki=4000*T_fast=0.2) keine Harm. ... 93

Abbildung 78: LINKS: kein Filter (Kp=4, Ki=4000*T_fast=0.2) 5.Harm. 0.05pu, RECHTS: PT1 Filter (Kp=4, Ki=4000*T_fast=0.2) 5.Harm. 0.05pu. ... 93

Abbildung 79: Berechnungen der Verstärkungen in adc.h ... 99

Abbildung 80: Auslesung des ADC’s in adc.c ... 99

Abbildung 81: Anordnung der RJ45-Stecker der analogen Eingänge am POETIC [modified: N45, und Doc AFE_2018] ... 100

Abbildung 82: FO-Pinbelegung: 6 PWM Signalen und das Fault_drivers Signal ... 102

Abbildung 83: Simulierter AFE in Typhoon, der mit POETIC angesteuert wird. ... 107

Seite 9

1 Einleitung

Das Industrieelektronik-Labor der HEI von der HES-SO Wallis will für ihre Aktivitäten im Bereich Forschung und Entwicklung über ein funktionierendes AFE Modul (Active Front End) verfügen. Dieses AFE Modul ist ein dreiphasiger DC/AC Konverter und soll eine Leistung von 20kVA bidirektional zwischen dem AC-Netz und dem schulinternen DC-Bus austauschen (Abbildung 1).

Das auf dem Markt gekaufte AFE Modul (Abbildung 2) ist ein Dreiphasen Spannungswechselrichter und kann mit einer digitalen Steuerungsplattform «POETIC» (Abbildung 3) verbunden werden. POETIC ist eine von der HEI selbst entwickelte Platine mit einem Mikroprozessor, die für verschiede leistungselektronische

Anwendungen verwendet werden kann.

In einer früheren Diplomarbeit wurde eine Interfaceplatine erstellt, die es erlaubt, das AFE Modul mit POETIC zu verbinden. In einer zweiten Diplomarbeit wurde eine weitere Interfaceplatine entwickelt, die die

Verbindung zwischen POETIC und dem Echtzeit-Simulationsgerät «Typhoon» ermöglicht.

Ziel dieser Diplomarbeit der Studienrichtung Systemtechnik in Fachrichtung «Power & Control» ist es, das AFE Modul mit einer Regelungssoftware auszurüsten. Um einen zusätzlichen Schutz zu gewährleisten, sollen Schaltkreise für DC/AC Vorladephasen und das Ein- und Ausschalten implementiert werden.

Bevor der Regelungscode auf POETIC implementiert wird, wird das Prinzip der Regelung mit Matlab/Simulink simuliert und mit der Software PLECS wird der Konverter simuliert. Als zweiter Schritt wird der Konverter in Typhoon simuliert und als neue Methode wird der originale Regelungscode direkt in Typhoon verwendet. Diese Methode ist neu und wird vom Industrieelektronik-Labor zurzeit noch nicht verwendet. Ziel ist es zu testen, wieviel vom originalen C-Code in Typhoon direkt geschrieben werden kann, damit man diesen Code später direkt auf dem POETIC-Mikroprozessor ohne grosse Veränderungen verwenden kann.

Photovoltaik DC-Verbraucher digitaler Kontroller DC-Bus 700V DC+ DC-AC-Netz 3x400V 50Hz 20kVA bidirektional

AFE (DC/AC Konverter)

To do: Regelung Abbildung 1:DC-Bus der Schule

Seite 10 «POETIC» (Power Electronic Controller) ist eine von der HEI selbst entwickelte Platine, die als digitale

Steuerungsplattform dient. POETIC kann für die Regelung von verschiedenen leistungselektronischen Geräten verwendet werden.

Abbildung 3: POETIC mit verschieden Modulkarten

Bei der Entwicklung des POETIC wurde auf die Methode von optischen Steuersignalen für die Ansteuerung der Halbleiter gesetzt, um eine schnelle und störungslose Übertragung zu gewährleisten. Die digitale

Steuerungsplattform besteht aus einem Basisboard mit einem Mikroprozessor und weiteren verschiedenen Ein- und Ausgangsboards die später genauer erklärt werden. POETIC enthält einen 32Bit Mikroprozessor vom Model TMS320F28377S von Texas Instruments mit einer Taktfrequenz von 200MHz.

Dank der verschiedenen modularen Ein- und Ausgangsboards von POETIC ist es möglich, mit vielen

verschieden Signalen zu kommunizieren. Mit der Karte der optischen Ein- und Ausgänge (FO_board:= Fiber optic board) werden die PWM-Signale an den Konverter geschickt. Digitale Ein- und Ausgangssignale

(DI/DO_board) werden mit dem SUB-9 Stecker übertragen. Die analogen Messsignale werden mit dem RJ45-Stecker übertragen und die digital/analog Signale werden mit dem SMA-RJ45-Stecker übertragen. Eine Übersicht der verschiedenen Stecker wird in der Abbildung 4 dargestellt.

Abbildung 4: (1) connecteur optique, (2) connecteur SUB-9, (3) connecteur RJ45, (4) connecteur SMA, (nachgeschlagen aus [2] S. 12)

2 Pflichtenheft

Die verschiedenen Schritte des Projekts, die angegangen werden müssen, sind folgende: • Analyse des AFE’s und der Schnittstellen zwischen AFE und POETIC.

• Analyse der Schnittstellen zwischen Typhoon und POETIC.

• Implementierung von Regelungsalgorithmen und Tests auf dem Echtzeitsimulator Typhoon (Regelung- und Zustandsmaschine).

• Untersuchen, ob die Möglichkeit besteht, den geschrieben Regelungscode in Typhoon direkt auf dem POETIC-Mikroprozessor zu verwenden.

Seite 11

3 Aufgabenaufteilung

Um das Projekt in verschiede Blöcke aufzuteilen und das Zeitmanagement einzuhalten wird ein Zeitplan erstellt (Anhang 3). Es werden Simulationen und Tests auf verschiedenen Simulationstools durchgeführt, bevor der Code auf dem realen PEOTIC-Prozessor und dem realen Konverter getestet wird. Dies hat den Vorteil, dass man den Code mit Vortests validieren kann, ohne dabei bei allfälligem Fehlverhalten die Hardware zu

zerstören.

Zur Überprüfung, ob die gewählte Regelungstechnik überhaupt funktioniert, wird als erster Schritt das zu regelnde System mit dem Softwareprogramm «PLECS-Blockset» annäherungsweise modelliert. Um am Anfang des Projekts Vereinfachungen zu erlauben, wird das Model des zu regelnden Systems vereinfacht dargestellt und erst später wird es genauer modelliert.

Das PLECS-Model wird in Matlab/Simulink eingefügt und die Regelung wird mit Simulink-Blöcken realisiert. Wenn bestätigt ist, dass die gewählte Regelungstechnik funktioniert, werden schrittweise die Simulink-Blöcke durch MATLAB-Funktionsblöcke ersetzt. Somit nähert sich die Implementierung immer mehr der Struktur des C-Codes, die man benötigt, um später den Mikroprozessor des POETIC zu programmieren.

Als nächster Schritt wird das zu regelnde System und die Regelung mit dem Echtzeit-Simulationstool

«Typhoon» des Typs «Hardware-In-the-Loop» Simulation (HIL) getestet. Es muss darauf geachtet werden, dass der für Typhoon geschriebene C-Code so implementiert wird, damit der gleiche C-Code für den POETIC

verwenden kann. Somit muss der Code nur einmal geschrieben werden und es wird Zeit eingespart. Diese Methode ist neu und es soll analysiert werden, inwiefern dies überhaupt möglich ist.

Zum Überprüfen wird der Regelcode auf den POETIC geladen und mit dem auf Typhoon simulierten Konverter verbunden. Um den POETIC mit Typhoon zu verbinden, wird das Interface verwendet, welches in der

Diplomarbeit «Conception d’interface entre simulateur temps réel et plateforme de contrôle numérique» [1] entwickelt wurde.

Zum Schluss wird an den POETIC der reale Konverter (AFE) angeschlossen. Um den POETIC mit dem AFE zu verbinden, wird das Interface verwendet, welches in der Diplomarbeit «Dispositif de contrôle digital pour un convertisseur de type Active Front End» [2] entwickelt wurde. Jedoch reichte die Zeit nicht aus, um den POETIC mit dem realen Konverter (AFE) zu verbinden. An diesem Schritt wird nach der Abgabe des schriftlichen Berichtes weitergearbeitet.

Als Übersicht werden die verschiedenen Simulationsetappen in der Tabelle 1, in der Abbildung 5 und in der Abbildung 6 nochmals dargestellt:

Seite 12 Etappen der verschiedenen Simulationtools

Nr.

Kontroller

Konverter

1 MATLAB/Simulink PLECS-Blockset

2 Typhoon (Echtzeit-Simulation) Typhoon (Echtzeit-Simulation)

3 POETIC Typhoon (Echtzeit-Simulation)

4 POETIC realer AFE

Tabelle 1: Etappen der verschiedenen Simulationstools

Abbildung 5: Kontroller in Typhoon, Konverter in Typhoon

Abbildung 6: OBEN: Kontroller in POETIC, Konverter in Typhoon, UNTEN: Kontroller in POETIC, Konverter: realer AFE Interface

(AFE)

Typhoon

POETIC AFE

POETIC (Typhoon)Interface

Seite 13

4 Beschreibung

Um eine Übersicht über die verschiedenen Geräte und Interfaces zu erhalten, werden diese nachfolgend beschrieben.

4.1 AFE (Active Front End)

Der verwendete AFE (Active Front End) Leistungskonverter vom Typ PCO-20T800SiC ist von der Marke teknoCEA und kann 20kVA bei einer dreiphasigen AC-Ausgangsspannung von 400VRMS und 30ARMS liefern. Weiterer wichtige Spezifikationen sind in der Tabelle 2 aufgelistet.

Beschreibung

Wert

Einheit

dreiphasige Ausgangsspannung 400 [VRMS] Ausgangsstrom 30 [ARMS] Leistung 20 [kVA] Schaltfrequenz 30 [kHz] Umgebungstemperatur 40 [°C] DC-Bus Spannung 800 [V]

Tabelle 2: Hautpspezifikationen des AFE Moduls, (nachgeschlagen aus [3] S.9)

Die drei aktiven Halbbrücken des AFE werden in diesem Projekt so verwendet, dass man einen aktiven DC/AC Konverter erhält (Abbildung 7). Dieser Konverter wird auch als dreiphasigen 2-Punkt Wechselrichter genannt, weil jede Halbrücke in Bezug auf das Mittlere Eingangspotenzial (0) genau zwei verschieden

Spannungspotenziale annehmen kann. In den drei Halbbrücken befinden sich keine Dioden, sondern Mosphets, die von extern angesteuert werden können. Deshalb wird der Konverter als «aktiv» bezeichnet.

DC+

DC-AFE (DC/AC Konverter) AC-Netz

(0) N (0) digitaler Kontroller 6 PWM To do: Regelung

Abbildung 7: vereinfachtes Funktionsschema des AFE

Auf der DC-Seite kann eine DC-Bus Spannung von 700VDC angeschlossen werden. Der dreiphasige Konverter erzeugt daraus eine dreiphasige AC-Spannung. Der AFE ist in der Lage den Leistungsfluss in beide Richtungen zu leiten. Somit ist der Konverter bidirektional und arbeitet als Gleichrichter, wenn der Leistungsfluss von der AC Seite zur DC Seite fliesst. Umgekehrt arbeitet der AFE als Wechselrichter, wenn der Leistungsfluss von der

Seite 14 DC Seite zur AC Seite fliesst. Da der DC/AC-Konverter aktiv angesteuert wird, kann die Leistung und der

Leistungsfakor angepasst werden.

Um den DC/AC-Konverter zu regeln, führt der AFE dem Entwickler folgende Messungen zurück: • drei AC-Ströme

• drei unabhängige AC-Spannungen • DC-Bus Spannung

• positive DC-Bus Mittelspannung • DC-Bus Strom

• Temperatur der Halbleiter

Die Halbleiter können mit sechs PWM-Signale angesteuert werden und es gibt eine Fehlermeldung

«Fault_drivers», falls ein Problem mit den Halbleitern auftritt. Zudem können acht Relais angesteuert werden, um die DC- und AC-Vorladephasen und das Ein- und Ausschalten des Konverters zu steuern. Mit einem

zusätzlichen Signal «Relay_Discharge» können die Kondensatoren auf der DC-Seite entladen werden, um gefährliche Restspannungen nach dem Ausschalten zu vermeiden.

Seite 15

5 Regelungstechniken & Validierung des Prinzips in Matlab/Simulink

5.1 Funktionsprinzip des AFE’s, [21]

Um die DC-Spannung in eine AC-Spannung umzuwandeln, werden drei Halbbrücken mit zwei Mosphets eingesetzt. Die zwei Mosphets einer Halbbrücke arbeiten im Gegentakt und leiten somit nie beide gleichzeitig. Sonst würde es einen Kurzschluss der DC-Spannung geben.

Der Mittelpunkt jeder Halbbrücke kann deshalb nur die Spannung +Ud/2 (oberers Mosphet leitend) oder – Ud/2 (unterers Mosphet leitend) in Bezug auf das mittlere Eingangspotenzial (0) annehmen (siehe Abbildung 8). DC+ DC-(0) (0) N A B C a b c UAN,BN,CN ULa,Lb,Lc URa,Rb,Rc Ua,b,c UN 0 Ua0 Uab Ubc Uca 0 .5 UDC 0 .5 UDC UDC IDC Ia Ib Ic

Abbildung 8: Funktionsschema des AFE

Die AC-Last besteht aus einer Entkopplungsinduktivität und einer in Stern geschalteter Gegenspannung, wobei der Sternpunkt nicht angeschlossen wird. Die Gegenspannung ist in diesem Projekt das vorhandene Netz. Somit schwebt das Spannungsniveau des offenen Sternpunktes in Bezug auf den Mittelpunkt (0) des

Eingangspotentials. Der offene Sternpunkt kann verschiedene Potentiale in Bezug auf (0) annehmen. Das hat der Vorteil das weniger Stromoberschwingungen entstehen und die Wechselströme Sinusförmiger sind.

5.2 Theorie

5.2.1 Einleitung

In diesem Projekt wird das Unterschwingungsverfahren gewählt, weil die Ausgangsströme ein gutes Spektrum liefern und sich stark einem Sinus annähern.

Um eine einfachere Regelung zu implementieren, werden die AC-Messsignale mathematisch vom dreiphasigen AC-Referenzsystem (fixes Dreiphasensystem) in ein DC-Referenzsystem (rotierendes Zweiphasensystem) umgewandelt. Somit erhält man DC-Signale, die viel einfacher zu regeln sind als AC-Signale. Nach der Regelung im DC-Referenzsystem werden die Signale wieder in das dreiphasige AC-Referenzsystem zurückberechnet. Diese Transformationen in die verschiedenen Referenzsysteme wird später ausführlich erklärt.

5.2.2 Unterschwingungsverfahren [4][21]

Die in den nachfolgenden Berechnungen verwendeten Ausdrücke und Grössen beziehen sich auf die Abbildung 8 und die Abbildung 13.

Mit dem Unterschwingungsverfahren können dreiphasige sinusförmige Ausgangsspannungen erzeugt werden, indem der Konverter mit einer hohen Schaltfrequenz F getaktet wird.

Seite 16 Die Halbleiter werden mit der PWM (Pulse width modulation) Modulationsmethode angesteuert. Dazu werden drei sinusförmige Referenzspannungen mit einem Dreiecksignal verglichen. Die Hauptaufgabe in dieser

Diplomarbeit besteht darin, die passendent Referenzspannungen einzuspeisen, um das gewünschte Verhalten des Konverters zu erzielen.

• sinusförmige Referenzspannungen 𝒖𝒙__𝒓𝒆𝒇:

Die drei sinusförmigen Referenzspannungen 𝑢𝑎__𝑟𝑒𝑓, 𝑢𝑏__𝑟𝑒𝑓, 𝑢𝑐__𝑟𝑒𝑓 haben die Amplitude 𝑈̂𝑟𝑒𝑓 und die

Frequenz f (𝜔 = 2𝜋𝑓). Die Frequenz 𝑓 ist die Frequenz der zu erzeugenden Wechselspannung und beträgt in diesem Projekt 50Hz. Die drei Referenzspannungen sind zueinander um 120° verschoben: 𝑢𝑥__𝑟𝑒𝑓= 𝑈̂𝑟𝑒𝑓∗ sin(𝜔𝑡 + 𝜑𝑢+ 𝐷) mit 𝑥 = 𝑎, 𝑏, 𝑐

für a: 𝐷 = 0° für b: 𝐷 = −120° für c: 𝐷 = 120° • Dreiecksignal 𝒖𝒕𝒓𝒊:

Das Dreiecksignal hat eine Amplitude von 𝑈̂𝑡𝑟𝑖 und eine Frequenz F im kHz-Bereich. Die Phasenlage ist

beliebig und die Frequenz ist in diesem Projekt 20kHz.

Das PWM Signal wird mit einem Komparator erzeugt. Die Mosphets einer Halbbrücke müssen so geschaltet werden, damit sich die Spannungen 𝑢𝑥0 (für x = a, b, c) wie folgt verhalten:

𝑢𝑥__𝑟𝑒𝑓> 𝑢𝑡𝑟𝑖 → 𝑢𝑥0 = + 𝑈𝐷𝐶 2 𝑢𝑥__𝑟𝑒𝑓< 𝑢𝑡𝑟𝑖 → 𝑢𝑥0 = − 𝑈𝐷𝐶 2

Der Modulationsgrad 𝑚(0 ≤ 𝑚 ≤ 1) ist das Verhältnis der Amplituden zwischen der Referenzspannung und des Dreiecksignals:

𝑚 =𝑈̂𝑟𝑒𝑓 𝑈̂𝑡𝑟𝑖

Mithilfe des Modulationsgrades kann die Grundschwingungsamplitude 𝐴 der erzeugten Wechselspannung von 0 bis 12𝑈𝐷𝐶 eingestellt werden:

Seite 17 𝒖𝒂,𝒃,𝒄= 𝐴 ∗ sin(𝜔𝑡 + 𝜑𝑢+ 𝐷) = 𝑚 ∗ 𝑈𝐷𝐶 2 ∗ sin(𝜔𝑡 + 𝜑𝑢+ 𝐷) mit: für a: 𝐷 = 0° für b: 𝐷 = −120° ua_ref für c: 𝐷 = 120°

Die Frequenzanteile entstehen nur bei höheren Frequenzen und das Spektrum sieht wie folgt aus: 𝑛 ∗ 𝐹 ± 𝑣 ∗ 𝑓(𝑛 = 1,2,3, … 𝑢𝑛𝑑𝑣 = 0,1,2,3, … )

Die Oberschwingungen befinden sich bei Vielfachen der Schaltfrequenz F und die Seitenbänder befinden sich bei Vielfachen der Grundschwingungsfrequenz f.

Das Ziel des zu implementierenden Regelungsalgorithmus ist es, die drei oben beschriebenen Referenzsignale 𝒖𝒂,𝒃,𝒄 im digitalen Kontroller zu berechnen, um die gewünschten PWM-Signale zu generieren.

5.2.3 Regelungsschleifen, [19][20][22]

5.2.3.1 Transformationen

In diesem Abschnitt wird erklärt, wie man Raumzeiger mathematisch von einem dreiphasigen AC-Referenzsystem in ein DC-AC-Referenzsystem und reziprok transformiert. Es wird an dieser Stelle nur eine

Übersicht von den verschiedenen Transformationen gezeigt (Tabelle 3). Die genauen Berechnungen werden im Anhang 6 ausführlich erklärt. [5][6][18]

AC-Referenzsystem DC-Referenzsystem fixes Dreiphasensystem (uvw-Referenzsystem) >> Clarke Transformation Fixes Zweiphasensystem (αβ-Referenzsystem) >> Park Transformation Mit ω rotierendes Zweiphasensystem (dq-Referenzsystem) <<inverse Clarke Transformation <<inverse Park Transformation Tabelle 3: Übersicht der Referenzsysteme

5.2.3.2 PLL (Phase-locked loop)

Damit man die Park Transformation und ihre inverse Transformation berechnen kann, muss man genau die Frequenz des Dreiphasensystems kennen. Um diese Frequenz genau bestimmen zu können, muss man sich mit einem PLL (Phase-locked loop) auf das Netz aufsynchronisieren (Abbildung 9).

Der PLL ist eine Regelung, die im fixen αβ-Referenzsystem mit dem rotierenden Raumzeigers 𝑢𝑠 versucht, das dq-Referenzsystem zu beschleunigen.

Ziel ist es, das dq-Referenzsystem mit der gleichen Winkelgeschwindigkeit 𝜔 = 2𝜋𝑓 zu drehen, wie der Raumzeigers 𝑢𝑠.

Dies erreicht man, indem man mit einem PI-Regler die q-Komponente auf null regelt. Somit versucht der Regler immer, dass sich der Raumzeigers 𝑢𝑠 genau auf der d-Komponente liegt. Wenn dieser Fall eingetroffen ist, ist der Regler im stationären Bereich. Man sagt, dass der PLL eingehängt ist oder dass man auf das Netz aufsynchronisiert ist. uvw αβ αβ dq PI-Regler 1/s ua(α) ua(β) ua(q) Θ = ωt uBN ua(d) + -ω 0

Seite 18 Der Ausgang des PI-Reglers liefert die Winkelgeschwindigkeit und wenn man dieses integriert, erhält man den benötigten Winkel Theta für die Park Transformation. Wenn der PLL auf das Netz aufsynchronisiert ist, ist die d-Komponente genau die Amplitude der Phasenspannung des Netzes.[16][17]

5.2.3.3 Modellierung des Systems

Um das System gut regeln zu können, muss zuerst das System mit einem Model beschrieben werden. Je genauer das System modelliert wird, desto besser ist das Regelverhalten.

Im Idealfall berechnet man die inverse Funktion 𝐺 des zu regelnden Systems 𝐹 und somit kann das System einfach geregelt werden. Dafür muss das zu regelnde System bekannt sein und mit mathematischen

Gleichungen darstellbar sein. Die inverse Funktion 𝐺 wird direkt vor das System 𝐹 gestellt, wie in Abbildung 10 dargestellt ist [8]. F = K System G = 1/K x y ySollwert x

Abbildung 10: Prinzipschema der Regelung

Wenn man ein beliebiges Ausgangssignal 𝑦 erhalten will, kann man direkt diesen Wert als 𝑦𝑆𝑜𝑙𝑙𝑤𝑒𝑟𝑡 vorgeben.

Da sich das Systems 𝐹 und die inverse Funktion 𝐺 kompensieren, wird direkt das Ausgangssignal 𝑦 ermittelt. 𝑌𝑆𝑜𝑙𝑙𝑤𝑒𝑟𝑡∗

1

𝐾∗ 𝐾 = 𝑦 𝑌𝑆𝑜𝑙𝑙𝑤𝑒𝑟𝑡 = 𝑦

Als Beispiel kann eine elektrische Schaltung mit einem Widerstand betrachtet werden (Abbildung 11). Der Strom 𝐼 ist vom Eingangssignal 𝑈 und vom System 𝑅1 abhängig:

𝐼 =1 𝑅∗ 𝑈 F = 1/R System G = R U I ISollwert U R I U

Abbildung 11: Prinzipschema der Regelung (Beispiel)

Wenn das System 𝐹 =1

𝑅 bekannt ist und die inverse Funktion 𝐺 = 𝑅 berechnet wird, kann der gewünschte

Ausgangstrom 𝐼 direkt mit einem Sollwertstrom 𝐼𝑆𝑜𝑙𝑙𝑤𝑒𝑟𝑡 vorgegeben werden.

Das gleiche Prinzip wird auch in diesem Projekt angewendet. Der DC/AC Konverter wird modelliert (Wie in Abbildung 8: Funktionsschema des AFE) und mit mathematischen Gleichungen beschrieben. Die inverse Funktion des Systems wird im Kontroller programmiert. Die in den nachfolgenden Berechnungen verwendeten Ausdrücke und Grössen beziehen sich auf die Abbildung 8 und die Abbildung 13. Für die Modellierung des Systems wurde folgende Quelle verwendet: [7] S. 10-14 und [5].

Seite 19 Ziel ist es, der Strom 𝑖𝑎,𝑏,𝑐 in den Induktivitäten vorzugeben, damit man die Spannung über der Induktivität

und somit auch die Phasenspannung 𝑢𝑎,𝑏,𝑐 regeln kann. In der Modellierung ist der Strom 𝑖𝑎,𝑏,𝑐 von der

Phasenspannung 𝑢𝑎,𝑏,𝑐, von der Netzphasenspannung 𝑢𝐴𝑁,𝐵𝑁,𝐶𝑁 und vom Spannungsabfall 𝑅𝑎,𝑏,𝑐∗ 𝑖𝑎,𝑏,𝑐 über

den Widerständen abhängig.

𝑖𝑎,𝑏,𝑐 =

1

𝐿∫(𝑢𝑎,𝑏,𝑐− 𝑢𝐴𝑁,𝐵𝑁,𝐶𝑁− 𝑅𝑎,𝑏,𝑐𝑖𝑎,𝑏,𝑐) ∗ 𝑑𝑡

Um die inverse Funktion im Kontroller zu berechnen, wird die Modellierung des Systems umgeschrieben und die Phasenspannungen 𝑢𝑎,𝑏,𝑐 werden isoliert:

𝑢𝑎,𝑏,𝑐 = 𝑅 ∗ 𝑖𝑎,𝑏,𝑐+ 𝐿

𝑑𝑖𝑎,𝑏,𝑐

𝑑𝑡 + 𝑢𝐴𝑁,𝐵𝑁,𝐶𝑁

Um die Schreibweise zu vereinfachen, werden die Berechnungen und Skizzen nur noch für eine Phase erklärt. Für die restlichen Phasen gilt analog das Gleiche. Für eine Phase gilt:

𝑢𝑎= 𝑅 ∗ 𝑖𝑎+ 𝐿

𝑑𝑖𝑎

𝑑𝑡 + 𝑢𝐴𝑁

Somit erhält man wie vorher beschrieben, eine Modellierung des Systems und die inverse Funktion des Systems davor. System F Inverses System G ua_ref ua iSollwe rt ia uAN_geme ssen To do (Kontroller)

Abbildung 12: Prinzipschema der Regelung des AFE

Jedoch erweist sich der Term mit der Ableitung als schwierig. Die Ableitung stellt die Steigung einer Funktion dar. Um diese Steigung berechnen zu können, benötigt man einen zukünftigen und der vorherige

Funktionswert. Da eine Ableitung zur Instabilität neigt und der zukünftige Funktionswert nicht einfach ermittelt werden kann, wird eine alternative Lösung verwendet. Um dieses Problem zu umgehen, wird ein PI-Regler eingesetzt.

Das inverse System wird später im Kontroller implementiert. Jedoch werden alle Ein- und Ausgangssignale des Kontrollers in ein rotierende dq-Referenzsystem transformiert, damit die Regelungsschleifen mit DC-Signalen und nicht mit AC-Signalen arbeiten können.

Die Gleichung des Kontrollers wird mit der Clarke-Transformation in ein αβ-Referenzsystem transformiert: 𝑢𝑎,𝑏,𝑐 = 𝑅 ∗ 𝑖𝑎,𝑏,𝑐+ 𝐿 𝑑𝑖𝑎,𝑏,𝑐 𝑑𝑡 + 𝑢𝐴𝑁,𝐵𝑁,𝐶𝑁 → 𝑢𝑎(αβ) = 𝑅𝑖(αβ)+ 𝐿 𝑑𝑖(αβ) 𝑑𝑡 + 𝑢𝐴𝑁(αβ)

Mit der Park-Transformation wird das fixe αβ-Referenzsystem schliesslich in ein rotierendes

dq-Referenzsystem transformiert. Das dq-dq-Referenzsystem rotiert mit einer Winkelgeschwindigkeit von 𝜔 = 2𝜋𝑓 der Netzphasenspannung.

Seite 20 𝑢𝑎(αβ)= 𝑅𝑖(αβ)+ 𝐿 𝑑𝑖(αβ) 𝑑𝑡 + 𝑢𝐴𝑁(αβ) → 𝑢𝑎(αβ)𝑒𝑗𝜔𝑡= 𝑅𝑖(αβ)𝑒𝑗𝜔𝑡+ 𝐿 𝑑 𝑑𝑡(𝑖(αβ)∗ 𝑒 𝑗𝜔𝑡) + 𝑢 𝐴𝑁(αβ)𝑒𝑗𝜔𝑡 𝑢𝑎(αβ)𝑒𝑗𝜔𝑡 = 𝑅𝑖(αβ)𝑒𝑗𝜔𝑡+ 𝐿 𝑑𝑖(αβ) 𝑑𝑡 ∗ 𝑒 𝑗𝜔𝑡+ 𝐿𝑖 (αβ)∗ 𝑗𝜔𝑒𝑗𝜔𝑡+ 𝑢𝐴𝑁(αβ)𝑒𝑗𝜔𝑡

Die Drehung mit 𝑒𝑗𝜔𝑡 wandelt die Gleichung in das dq-Referenzsystem um: 𝑢𝑎(dq)= 𝑅𝑖(dq)+ 𝐿

𝑑𝑖(dq)

𝑑𝑡 + 𝑗𝜔𝐿𝑖(dq)+ 𝑢𝐴𝑁(dq)

Die Gleichung im dq-Referenzsystem kann in Real- und Imaginärteil aufgespalten werden. Der Ausdruck 𝑗𝜔𝐿𝑖(dq) wird wie folgt ausmultipliziert:

𝑗𝜔𝐿𝑖(dq) = 𝑗𝜔𝐿(𝑖(𝑑)+ 𝑗𝑖(𝑞)) = 𝜔𝐿(𝑗𝑖(𝑑)− 𝑖(𝑞)) = 𝜔𝐿(−𝑖(𝑞)+ 𝑗𝑖(𝑑))

Somit ist der Realteil (d-Komponente),

−𝜔𝐿𝑖(𝑞)

und der Imaginärteil (q-Komponente):

𝜔𝐿𝑖(𝑑)

Die Kompletten Gleichungen für die d- und q-Komponenten sind die folgenden: { 𝑢𝑎(d) = 𝑅𝑖(d)+ 𝐿 𝑑𝑖(d) 𝑑𝑡 − 𝜔𝐿𝑖(𝑞)+ 𝑢𝐴𝑁(d) 𝑢𝑎(𝑞) = 𝑅𝑖(𝑞)+ 𝐿 𝑑𝑖(q) 𝑑𝑡 + 𝜔𝐿𝑖(𝑑)+ 𝑢𝐴𝑁(q)

Wie vorhin schon erwähnt, sind die Terme mit der Ableitung problematisch und werden deshalb durch einen PI-Regler ersetzt. Die ersten zwei Terme werden als ein System der 1. Ordnung betrachtet. Dieses RL-System wird mit einem PI-Regler geregelt und die zwei letzten Terms werden als Feed-Forward dazu addiert.

{𝑢𝑢𝑎(d)__𝑟𝑒𝑓= 𝑅𝑒𝑔(𝑠)∗ (𝑖(𝑑)__𝑟𝑒𝑓− 𝑖(𝑑)) − 𝜔𝐿𝑖(𝑞)+ 𝑢𝐴𝑁(d)

𝑎(q)__𝑟𝑒𝑓 = 𝑅𝑒𝑔(𝑠)∗ (𝑖(𝑞)__𝑟𝑒𝑓− 𝑖(𝑞)) + 𝜔𝐿𝑖(𝑑)+ 𝑢𝐴𝑁(q)

Der Integrator des PI-Regler ist einfach zu implementieren. Es reicht alle vorgängigen Funktionswerte zu kennen und die Fläche unter der Funktionskurve auszurechnen.

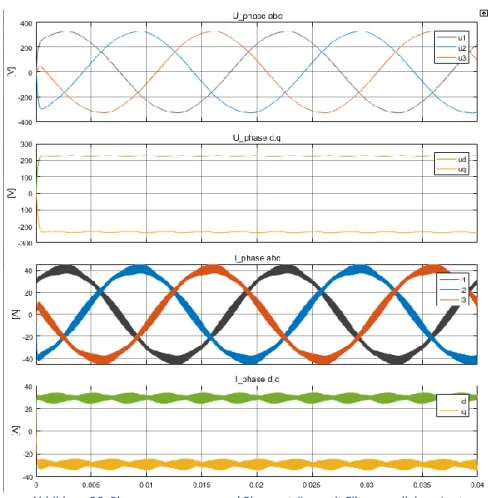

In der Abbildung 13 werden die Transformationen, die PLL Regelschleife und die Gesamtregelschleife als Blockschaltbild dargestellt. Die Ausgangsgrössen 𝑢𝑎__𝑟𝑒𝑓, 𝑢𝑏__𝑟𝑒𝑓𝑢𝑛𝑑𝑢𝑐__𝑟𝑒𝑓 werden für die Erzeugung der

Seite 21 uvw αβ αβ dq PI-Regler 1/s ua(α) ua(β) ua(q) Θ = ωt uCN uBN uAN + -ω 0 uvw αβ αβ dq i(α) i(β) i(q) ib PI-Regler + i(d)_ref PI-Regler + i(q)_ref Lω -Lω i(d) ua(d) + + + + + -dq αβ αβ uvw ub_ref ua(d)_ref ua(q)_ref sc ale to m o d u la to r

Abbildung 13: Komplettes Blockschema der Regelungsschleifen, [7] S.13

Die Regelschleife erfordert, dass man die drei Phasenströme 𝑖𝑎,𝑏,𝑐 und die drei Netzphasenspannung 𝑢𝐴𝑁,𝐵𝑁,𝐶𝑁

misst. Die PLL-Regelschleife wird für die Frequenz- und Winkelbestimmung benötigt.

Mithilfe des bestimmten Winkels können die verschiedenen Transformationen vorgenommen werden. Im DC-Referenzsystem wird schliesslich mithilfe der gemessen und transformierten Strömen mit einem PI-Regler die richtigen Spannungen berechnet. Diese werden wieder rücktransformiert und ins AC-Referenzsystem ins System eingespiesen.

5.3 Zu implementierende Sicherheiten für den AFE

Der Hersteller des AFE Moduls gibt verschiedene Sicherheitsmassnahmen vor, die zwingend notwendig sind. Diese sind im Konverter noch nicht vorhanden und müssen vom Entwickler selbst entwickelt werden. Folgende Sicherheiten müssen softwaremässig oder hardwaremässig implementiert werden:

• Preload-Vorgang des DC-Buses

• Kontrollalgorithmus, der kontrolliert, ob die DC-Bus Preload-Vorgang richtig verläuft. • Kontrolle ob eine Überspannung beim DC-Bus vorhanden ist und eventuelles Eingreifen.

• Kontrolle damit die Temperatur der Halbleiter nicht über 100°C steigt. Bei 150°C werden die Mosphets zerstört.

• Cross-conduction Sicherheit und Totzeit der Mosphets

• Sicherheitsablauf bei Fehlverhalten der Mosphets («Fault_drivers» Meldung)

Der Begriff «Cross-conduction» bedeutet, dass die beiden Mosphets einer Halbbrücke gleichzeitig leiten. In diesem Fall entsteht ein Kurzschluss und es fliessen sehr grosse Ströme, die die Halbleiter zerstören können. Deshalb muss man sicherstellen, dass die Mosphets einer Halbbrücke nie gleichzeitig leiten.

Deswegen wird später in der CPLD des POETIC’s mit logischen Gatter eine Verriegelung erstellt, die sichergestellt, dass die Mosphets einer Halbbrücke nie gleichzeitig angesteuert werden. Jedoch leiten die Mosphets nach ihrer Abschaltung immer noch eine bestimmte Zeit weiter, bevor sie den Strom blockieren. Dies kann auch zur «Cross-conductione» führen und die Mosphets zerstören. Deshalb wird eine Totzeit in den PWM-Signalen von 0.5𝜇𝑠 eingefügt, damit diese Ausschaltzeit der Halbleiter berücksichtigt wird.

Seite 22

5.4 DC-AC Vorladephasen und Entladung der DC-Kondensatoren

5.4.1 Entladung der DC-KondensatorenDer DC-Bus ist an zwei in Serie geschalteten Elektrolyt-Kondensatoren von 2700µF/500V angeschlossen. Somit halbiert sich die Gesamtkapazität auf 1350µF. Um die Kondensatoren Spannung auszugleichen und ein

Entladen zu garantieren, sind zwei 33kΩ Widerstände fix parallel dazu eingebaut.

R_Preload Preload Relais

Abbildung 14: Lade- und Entladeschema des AFE, (nachgeschlagen aus [3] S. 15, (bearbeitet))

Mit dem Steuersignal «Relay_Discharge» kann die Entladung mit zwei Relais zusätzlich von extern gesteuert werden. Diese zwei «discharge-Relais» haben «normally closed» Kontakte, damit auch bei einem plötzlichen Spannungsausfall die DC Spannung auf eine ungefährliche Spannung entladet wird. Die zwei Relais schalten je vier 10kΩ Widerstände parallel zu den Kondensatoren, damit sich der Entladewiderstand von 66kΩ auf 4’647Ω reduziert.

𝑅𝑑𝑖𝑠𝑐ℎ𝑎𝑟𝑔𝑒= [33𝑘Ω + 33𝑘Ω]//[(𝑣𝑖𝑒𝑟10𝑘Ωparallel) + (𝑣𝑖𝑒𝑟10𝑘Ωparallel)] = 4′647Ω

In obiger Gleichung bedeuten die zwei Divisionsstriche «//», dass die Widerstände parallelgeschaltet sind. Nach Angaben des Herstellers entladen sich die Kondensatoren mit einer maximalen DC Spannung von 800V vollständig innert 36.7s (nach 6τ). Der maximale Entladestrom beträgt in diesem Fall:

𝐼𝑚𝑎𝑥= 𝑈𝐷𝐶 𝑅𝑑𝑖𝑠𝑐ℎ𝑎𝑟𝑔𝑒 = 800𝑉 4′647Ω= 172𝑚𝐴 5.4.2 DC-AC Vorladephasen

Um die Kondensatoren des Busses zu laden, gibt es verschiede Möglichkeiten (siehe Abbildung 15). Die DC-Kondensatoren können zum Beispiel durch die Dioden des Konverters von der Seite des AC-Netzes geladen werden (Variante 3). Dies setzt voraus, dass die Spannung des AC-Netzes immer vorhanden ist und dass die Spannung des DC-Buses nicht zwingend sein da sein muss, aber da sein kann. In dieser Variante kann man mit Hilfe des AC-Netzes einen DC-Bus erstellen.

Seite 23

Variante 1

Variante 2

Variante 3

Abbildung 15: Verschiedene Variante um die DC-Bus Kondensatoren aufzuladen

Die DC-Kondensatoren können auch von der DC-Seite her geladen werden (Variante 1 & 2). Dies setzt voraus, dass die Spannung des DC-Busses immer vorhanden sein muss und dass die Spannung des AC-Netzes nicht zwingend sein da sein muss, aber da sein kann. Wenn die AC-Spannung vorhanden ist, bedeutet das, dass der AFE am normalen AC-Netz des EW’s (Elektrizitätswerk) angeschlossen ist. Hingegen wenn keine AC-Spannung vorhanden ist, bedeutet das, dass am AFE zum Beispiel an einen Motor angeschlossen ist.

Bei der Variante 3 arbeitet der Konverter als Gleichrichter und die Kondensatoren werden über drei

Vorladewiderstände von der AC-Seite aufgeladen. Zudem muss kontrolliert werden, dass der DC-Bus erst mit der richtigen Spannung dazu geschaltet wird. Der Vorteil von dieser Variante ist es, dass auch ohne

Anwesenheit der DC-Bus Spannung der Konverter in Betrieb genommen werden kann. Dieses Vorgehen wird in der Realität meistens verwendet.

Jedoch am einfachsten und mit am wenigsten Aufwand verbundener Variante ist es, die Kondensatoren von der DC-Seite aufzuladen. Es wird angenommen, dass die DC-Bus Spannung immer anwesend ist und die

Seite 24 Kondensatoren deshalb immer von der DC-Seite aufgeladen werden können. Zusätzlich wird angenommen, dass das AC-Netz auch immer vorhanden ist und somit die Versorgung der Relais- und Schützsteuerung auch von diesem AC-Netz bezogen werden kann. Dies entspricht nicht der Realität, aber aus Zeitgründen wird diese Variante gewählt.

Zudem wird die Variante 2 der Variante 1 vorgezogen, weil in der Variante 2 mit einem Relais direkt der Konverter vom DC-Bus getrennt werden kann.

5.4.3 Dimensionierung des Preload-Widerstands

Bei der Dimensionierung des Preload-Widerstands muss auf zwei wichtige Punkte geachtet werden (s. Abbildung 14). Als erstens gilt es zu beachten, dass die Peak-Leistung am Preload-Widerstand möglichst klein gehalten wird. Das erlaubt, einen kleineren und somit günstigeren Leistungswiderstand einzusetzen. Diese Bedingung verlangt aber, dass der Widerstandswert hoch gewählt werden muss, was wiederum Nachteile mit sich bringt.

Ein grosser Widerstandswert bringt eine lange Vorladezeit mit sich. Zudem fliesst gleichzeitig zum Preload-Vorgang ein kleiner Entladestrom von den DC-Bus Kondensatoren durch die zwei in Serie geschalteten 33kΩ Widerstände, der mit steigender DC-Bus Spannung immer grösser wird. Dieser Entladestrom fliesst auch durch den Preload-Widerstand und verursacht am Ende des Preload-Vorgangs einen Spannungsabfall über diesem. Dieser Spannungsabfall bleibt bestehen und somit können die DC-Bus Kondensatoren nie ganz bis auf 700V aufgeladen werden. Zudem muss beim Betätigen des Preload-Relais mit dieser Spannungsdifferenz das Relais geschaltet werden, was einen Strompeak auf der DC-Seite zur Folge hat.

Um all diesen Bedingungen Rechnung zu tragen, wurden eine verschiedene Anzahl von in Serie geschaltenen 1kΩ Leistungswiderstände untersucht, um einen Preload-Widerstand 𝑅𝑃𝑟𝑒𝑙𝑜𝑎𝑑__𝑡𝑜𝑡 zusammenzubauen. Die

Leistung der ausgewählten Leistungswiderstände vom Typ LPR50 1k J (1kΩ, 50W) und vom Typ LPR100 1k J (1kΩ, 100W) kann während 5 Sekunden um das 5-fache überschritten werden (Datasheet im Anhang 7). Von folgenden untersuchten Varianten wurde die Variante 3 mit nur einem Leistungswiderstand ausgewählt:

• Variante 1: 3 ∗ 1𝑘𝛺 = 3𝑘𝛺 • Variante 2: 2 ∗ 1𝑘𝛺 = 2𝑘𝛺 • Variante 3: 1 ∗ 1𝑘𝛺 = 1𝑘𝛺

Die Begründung der Auswahl und die Berechnungen werden nachfolgend beschrieben. Die Berechnungen werden mittels der ausgewählten Variante 3 erklärt (𝑅𝑃𝑟𝑒𝑙𝑜𝑎𝑑__𝑡𝑜𝑡 = 1𝑘𝛺):

Die Peak-Leistung am Preload-Widerstand tretet beim Einschaltmoment des Preload-Vorgangs auf, wenn die DC-Bus Kondensatoren vollständig entladen sind. Die Kondensatoren können im Einschaltmoment als

Kurzschluss betrachtet werden. Deswegen können die zwei in Serie geschaltenen 33kΩ Widerstände 𝑅𝐸𝑛𝑡𝑙𝑎𝑑𝑒𝑛

in dieser Phase vernachlässigt werden. Der Peak-Strom beträgt somit. 𝐼̂𝐷𝐶 =

𝑈𝐷𝐶

𝑅𝑃𝑟𝑒𝑙𝑜𝑎𝑑__𝑡𝑜𝑡

=700𝑉

1𝑘𝛺 = 0.7𝐴 Die Peak-Leistung am Widerstand beträgt:

𝑃̂𝑅 = 𝑅𝑃𝑟𝑒𝑙𝑜𝑎𝑑__𝑡𝑜𝑡∗ 𝐼̂𝐷𝐶 2

= 1𝑘𝛺 ∗ (0.7𝐴)2= 490𝑊

Am Ende des Preload-Vorgangs können die zwei in Serie geschalteten 33kΩ Widerstände nicht mehr vernachlässigt werden. Zu diesem Zeitpunkt fliesst durch diese zwei Entladewiderstände und durch den Preload-Widerstand einen Entladestrom 𝐼𝑐𝑜𝑛𝑠𝑡 und verursacht über dem Preload-Widerstand einen

Spannungsabfall 𝑈∆ von bis zu 10.45V:

𝐼𝑐𝑜𝑛𝑠𝑡 =

𝑈𝐷𝐶

𝑅𝑃𝑟𝑒𝑙𝑜𝑎𝑑__𝑡𝑜𝑡+ 2 ∗ 𝑅𝐸𝑛𝑡𝑙𝑎𝑑𝑒𝑛

= 700𝑉

Seite 25 𝑈∆= 𝑅𝑃𝑟𝑒𝑙𝑜𝑎𝑑__𝑡𝑜𝑡∗ 𝐼𝑐𝑜𝑛𝑠𝑡 = 1𝑘𝛺 ∗ 10.45𝑚𝐴 = 10.4𝑉

Der Preload-Vorgang ist nach ca. 5τ abgeschlossen:

5τ = 5 ∗ 𝑅𝑃𝑟𝑒𝑙𝑜𝑎𝑑__𝑡𝑜𝑡∗ 𝐶 = 5 ∗ 1𝑘Ω ∗ 1′350μF = 6.75𝑠

Die Resultate der der verschiedenen Resultate befindet sich in der Tabelle 4.

Variante 1 Variante 2 Variante 3

𝑹𝑷𝒓𝒆𝒍𝒐𝒂𝒅_𝒕𝒐𝒕 𝟑 ∗ 𝟏𝒌𝜴 = 𝟑𝒌𝜴 𝟐 ∗ 𝟏𝒌𝜴 = 𝟐𝒌𝜴 𝟏 ∗ 𝟏𝒌𝜴 = 𝟏𝒌𝜴

𝑰̂𝑫𝑪 0.23A 0.35A 0.7A

𝑷̂ pro Widerstand 54W 122.5W 490W

Nennleistung pro Widerstand

50W 50W 100W

𝑰𝒄𝒐𝒏𝒔𝒕 10.14mA 10.29mA 10.45mA

𝑼∆ 30.43V 20.58V 10.4V

Ladezeit 20.25s 13.5s 6.75s

Preis 3 ∗ 6𝐶𝐻𝐹 = 18𝐶𝐻𝐹 2 ∗ 6𝐶𝐻𝐹 = 12𝐶𝐻𝐹 𝟖𝑪𝑯𝑭

Tabelle 4: Übersicht der verschiedenen Widerstandsvarianten des Preload-Widerstands 𝑅𝑃𝑟𝑒𝑙𝑜𝑎𝑑_𝑡𝑜𝑡

Für den Preload-Vorgang wurde die Variante 3 ausgewählt, weil nur ein Leistungswiderstand benötigt wird, der Spannungsabfall 𝑈∆ über dem Preload-Widerstand klein ist und die Peak-Leistung nicht grösser ist als 5x

die Nennleistung ist. Zudem ist die Überschreitung der Nennleistung nur von kurzer Dauer.

Die maximal erreichbare Kondensatorenspannung 𝑈𝐾𝑜𝑛𝑑𝑜__𝑚𝑎𝑥 beträgt bei dieser Variante ca. 689V.

𝑈𝐾𝑜𝑛𝑑𝑜__𝑚𝑎𝑥= 𝑈𝐷𝐶__𝐵𝑢𝑠− 𝑈∆= 700𝑉 − 10.4𝑉 ≈ 689𝑉

Bei der Erstellung der Zustandsmaschine muss dieser Wert berücksichtigt werden und der Preload-Vorgang muss kontinuierlich an verschiedenen Zeitpunkten überprüft werden.

Die Spannungswerte beim Zeitpunkt der Überprüfung werden mit der Gleichung der Kondensatoren approximativ berechnet und in einer LTspice-Simulation validiert:

𝑈(𝑡)= 𝑈0∗ (1 − 𝑒− 𝑡 𝜏)

Mit der maximal erreichbaren Spannung 𝑈0 von 689V, die momentane Kondensatorspannung 𝑈(𝑡), und mit

der Zeitkonstante τ = 𝑅𝑃𝑟𝑒𝑙𝑜𝑎𝑑__𝑡𝑜𝑡∗ 𝐶 = 1𝑘Ω ∗ 1′350μF = 1.35𝑠.

Seite 26 Die ausgeführten Simulationen im LTspice (Abbildung 16) bestätigen die Berechnungen. Die Graphen des Stromes 𝐼𝐷𝐶 und der Kondensatorespannung 𝑈𝐾𝑜𝑛𝑑𝑜 befinden sich im Anhang 8. Bei den Simulationen sind die

berechneten Werte nicht ganz erreicht worden, weil die Kondensatoren zum Zeitpunkt 𝑡 = 5𝜏 = 6.75𝑠 noch nicht zu 100% geladen sind.

Der Spitzenstrom beträgt 0.7A und fällt danach auf einen konstanten Entladestrom von 14.7𝑚𝐴(@𝑡 = 5𝜏)ab (berechnet @𝑡 = ∞: 𝐼𝐷𝐶 = 10.45𝑚𝐴).

Die Spannung über den DC-Bus Kondensatoren ladet sich bis auf 685.3𝑉(@𝑡 = 5𝜏) auf (berechnet @𝑡 = ∞: 𝑈𝐾𝑜𝑛𝑑𝑜 = 689𝑉).

Die Peak-Leistung des Preload-Widerstandes beträgt am Anfang kurzzeitig 500W (siehe Abbildung 17) und fällt danach innert 1.5 Sekunden unter die nominale Leistung des Preload-Widerstandes von 100W. Die maximale Überschreitung von 5x die Nennleistung des Widerstandes während von 5 Sekunden wird somit nicht

überstiegen.

Abbildung 17: Die Leistung am Preload-Widerstand

Die Berechnung ist nur approximativ, weil zeitgleich die Kondensatoren über die 33kΩ Widerstände entladen werden (Tabelle 5). Zeitpunkt t nach dem Einschalten 𝑼(𝒕) (Approximative Berechnung) 𝑼(𝒕) LTspice-Simulation In POETIC: Kontrollpunkte 𝒕 = 𝟏𝒔* 360V 364V 𝑈(𝑡)> 320V 𝒕 = 𝟐𝒔* 533V 536V 𝑈(𝑡)> 490V 𝒕 = 𝟑𝒔* 614V 617V 𝑈(𝑡)> 590V 𝒕 = 𝟒𝒔 ∗ 653V 655V 𝑈(𝑡)> 620V 𝒕 = 𝟔. 𝟕𝟓𝒔 684V 685V 𝒕 = 𝟖𝒔 687V 688V MIN_PRELOAD_TIME

Tabelle 5: Spannungswerte der DC-Bus Kondensatoren beim Preload. *Diese Zeitpunkte werden in der Zustandsmaschine in POETIC zur Überprüfung des Preload-Vorgangs verwendet.

In POETIC wurde der Zeitpunkt der Kontrollpunkte mit einer Sicherhetsmarge bestimmt, weil das Schliessen des AFE-Relais und des DC-Relais mit Verzögerungen verbunden sind.

Seite 27 Basierend auf diesen Messungen werden folgende Konstanten für die Zustandsmaschine definiert (siehe Tabelle 6):

Konstanten der Zustandsmaschine in POETIC

MIN_PRELOAD_TIME 𝑡 = 8𝑠

BUS_DC_PRELOAD_MIN 𝑈𝐷𝐶__𝑚𝑖𝑛= 640𝑉

PRELOAD_TIMEOUT 𝑡 = 11𝑠

Tabelle 6: Konstanten in POETIC für die Kontrolle des Preload-Vorgangs

5.5 Tests: Kontroller (Matlab/Simulink)-Konverter (PLECS-Blockset)

Das Prinzip der in den vorherigen Kapiteln beschriebenen Theorie über den Regelungsalgorithmus und er Zustandsmaschine wird mit nachfolgenden Matlab/Simulink Simulationen überprüft.

5.5.1 Simulink-Funktionsblöcke (Transformationen und PLL)

Das Prinzip und das Verhalten der PLL-Schaltung wird in Simulink simuliert, um die Funktionsweise zu überprüfen. Da später diese Transformation mit der Programmiersprache C programmiert werden, werden eigene Transformations-Blöcke erstellt. Die Implementierung dieser Blöcke basiert auf der Clark- und Parktransformation. Einfachheitshalber wird ein symmetrisches Dreiphasensystem ohne Neutralleiter

betrachtet, damit die Nullkomponente des Nullsystems (composante homopolaire) weggelassen werden kann. Um die PLL-Schaltung zu testen werden drei Cosinus-Signale mit einer Amplitude von 325V, die je 120°

zueinander verschoben sind, eingespiesen (siehe Abbildung 18 und Abbildung 19). Die d-Komponente wird auf 0 geregelt und das System stabilisiert sich nach ca. 20ms. Für die Regelung wird ein PI-Regler mit der Gleichung 𝐺(𝑠)= 𝐾𝑝+ 𝐾𝑖∗

1

𝑠 verwendet (𝐾𝑝= 10, 𝐾𝑖 = 1′100).

Die Frequenz und der Winkel Theta stabilisieren sich ca. nach 2ms (siehe Abbildung 20). Somit kann sich der PLL erfolgreich auf das AC-Netz synchronisieren. Diese Schaltung liefert dem Mikroprozessor die Frequenz, der Winkel Theta und die Amplitude des AC-Netzes (d-Komponente) für weitere Berechnungen.

Einfachheitshalber wird ein störungsfreies symmetrisches Dreiphasensystem in die PLL-Schaltung

eingespiesen. Später im Bericht werden Harmonische Störungen berücksichtigt, was zur Folge hat, dass man diverse Filter einbauen muss.

Simulationsparameter: (Solver: Variable-step, Auto-solver, Max step size: 0.05e-3, relative tolerance 1e-3)

Seite 28

Abbildung 19: Eingangsspannung, Amplitude 325V

Abbildung 20: PLL-Verhalten mit (Kp=10, Ki=1'100), Oben: dq-Komponenten, Mitte: PLL Frequenz, unten: Winkel Theta 5.5.2 Simulink-Funktionsblöcke (Stromregelung)

Um nur den Closed-Loop mit der Stromregelung zu testen, wird am Anfang auf die Zustandsmaschine und auf die dreiphasige Gegenspannung verzichtet. An der Stelle der dreiphasigen Gegenspannung wird eine Passive Last eingesetzt.

Somit kann nicht mit einer PLL-Schaltung auf das AC-Netz synchronisiert werden. Deshalb wird der Winkel Theta wieder mit einer Rampe simuliert.

Für ein präzises Modell des AFE’s zu erstellen, werden die Grössen und Dimensionen des originalen AFE’s verwendet. Die Grösse der Entkopplungsinduktivität und deren Widerstand wird für einen Strom von 30Arms ausgewählt (𝐿 = 444𝜇𝐻, 𝑅 = 45𝑚Ω). Diese Werte wurde von einer Messung in einer früheren Diplomarbeit entnommen, [2] Seite 50.

Mit einer Leistung des AFE’s von 20kW und einer Phasenspannung der Last von 230V wird der in Stern geschalteter Lastwiderstand pro Phase auf 7.9Ω dimensioniert.

𝑃𝑡𝑜𝑡= 3 ∗ 𝑈𝑝ℎ2 𝑅𝐿 𝑅𝐿 = 𝑈𝑝ℎ2 1 3 𝑃𝑡𝑜𝑡 =(230𝑉) 2 1 3 20𝑘𝑊 = 7.9Ω

An diesem Arbeitspunkt beträgt der Laststrom pro Phase ca. 30Arms: 𝑃𝑡𝑜𝑡= 3 ∗ 𝑈𝑝ℎ∗ 𝐼𝑝ℎ 𝐼𝑝ℎ = 1 3 𝑃𝑡𝑜𝑡 𝑈𝑝ℎ = 1 3 20𝑘𝑊 230𝑉 = 29𝐴𝑟𝑚𝑠 ≈ 30𝐴𝑟𝑚𝑠

Seite 29 Eine Übersicht der verwendeten Simulationsparameter befindet sich in der Tabelle 7.

Beschreibung

Wert Einheit

Entkopplungsinduktivität 444 μH

Widerstand der Entkopplungsinduktivität 45 mΩ

Kapazität des DC-Kondensators 2700 uF

DC-Spannung 700 Vdc

𝑷𝒕𝒐𝒕: Leistung 20 kW

𝑼𝒑𝒉: Phasenspannung (Last) 230 Vrms

𝑹𝑳: Lastwiderstand 7.9 Ω

𝑰𝒑𝒉: Laststrom 30 Arms

Tabelle 7: Verwendetet Simulationsparameter

Die Grundschwingungsamplitude 𝐴 der erzeugten Wechselspannung hängt wie folgt vom Modulationsgrad und der DC-Spannung ab:

𝐴 = 𝑚 ∗𝑈𝐷𝐶 2 𝑚 = 𝐴 ∗𝑈1

𝐷𝐶

2

Für die Generierung der drei Referenzspannungen wird ein Dreiecksignal mit einer Amplitude von 𝑈̂𝑡𝑟𝑖 = 10𝑉

gewählt. Der Modulationsgrad 𝑚 ist definiert durch: 𝑚 =𝑈̂𝑟𝑒𝑓

𝑈̂𝑡𝑟𝑖

Bevor das unskalierte Referenzsignal 𝑢𝑟𝑒𝑓__𝑆𝑜𝑙𝑙𝑤𝑒𝑟𝑡 mit dem Dreiecksignal verglichen werden kann, muss es

zuerst mit dem Faktor 110𝑉 2∗700𝑉 skaliert werden. 𝑢__𝑟𝑒𝑓 = 𝑚 ∗ 𝑈̂𝑡𝑟𝑖 = 𝑢𝑟𝑒𝑓__𝑆𝑜𝑙𝑙𝑤𝑒𝑟𝑡∗ 1 𝑈𝐷𝐶 2 ∗ 𝑈̂𝑡𝑟𝑖 = 𝑢𝑟𝑒𝑓__𝑆𝑜𝑙𝑙𝑤𝑒𝑟𝑡∗ 10𝑉 1 2 ∗ 700𝑉

Die erstellte Schaltung der Stromregelung in Simulink basiert auf den Gleichungen des Kapitels: 5.2.3.3 Modellierung des Systems

{𝑢𝑢𝑎(d)__𝑟𝑒𝑓= 𝑅𝑒𝑔(𝑠)∗ (𝑖(𝑑)__𝑟𝑒𝑓− 𝑖(𝑑)) − 𝜔𝐿𝑖(𝑞)+ 𝑢𝐴𝑁(d)

𝑎(q)__𝑟𝑒𝑓 = 𝑅𝑒𝑔(𝑠)∗ (𝑖(𝑞)__𝑟𝑒𝑓− 𝑖(𝑞)) + 𝜔𝐿𝑖(𝑑)+ 𝑢𝐴𝑁(q)

Zurzeit wird in den Simulationen im Term ±𝜔𝐿𝑖(𝑞) noch eine fixe Frequenz von 50𝐻𝑧 verwendet. Diese

Frequenz muss später von der PLL-Schaltung geliefert werden.

Bei den folgenden Simulationen werden einfachheitshalber wieder die Transformationsblöcke der Simulink-Bibliothek verwendet. Zudem ist es von Vorteil, wenn der Closed-Loop zuerst mit einer

Entkopplungsinduktivität von 10𝑚𝐻 simuliert wird, bevor die reale Induktivität von 444𝜇𝐻 verwendet wird. Mit einer grösseren Induktivität wird die Stromvariation 𝑑𝑡𝑑𝑖 verkleinert und das System verhaltet sich träger. Somit ist das System stabiler und es kann besser getestet werden.

Der Stromregler wird mit folgenden Parameter dimensioniert (mit 𝐿 = 444𝜇𝐻): 𝐾𝑝__𝑖𝑑 = 𝐾𝑝__𝑖𝑞 = 25, 𝐾𝑖__𝑖𝑑 = 𝐾𝑖__𝑖𝑞= 70

Simulationsparameter (Abbildung 21, Abbildung 22):

• Sollwerte: 𝑖𝑑__𝑟𝑒𝑓= 30𝐴, 𝑖𝑞__𝑟𝑒𝑓= −30𝐴. Somit wird eine Amplitude von √𝑖𝑑__𝑟𝑒𝑓2+ 𝑖𝑑__𝑟𝑒𝑓2=

42.4𝐴 oder 30𝐴𝑟𝑚𝑠 erreicht.

Seite 30

Abbildung 21: links: PLECS Circuit (AFE) Closed-Loop, Mitte: Stromregelung im dq-Referenzsystem, rechts: Skalierung der Referenzspannungen

Seite 31 Das System ist stabil und die Stromsollwert werden schnell erreicht (Abbildung 23, Abbildung 24). Jedoch sind die Phasenspannungen und die Phasenströme und ihre dq-Komponenten gestört und oszillieren. Auch die generierten Referenzspannungen für die PWM Erzeugung sind stark gestört.

Abbildung 23: Phasenspannungen und Phasenströme ohne Filter

Abbildung 24: Referenzspannungen für die PWM-Generierung

Um die Störungen zu verringern, wird parallel zum Lastwiderstand ein Kondensator platziert. Dieser

Kondensator bildet mit der Entkopplungsinduktivität einen LC-Filter 2.Ordung. Die Grenzfrequenz 𝑓𝑟 des Filters

wird eine Dekade tiefer als die Kommutierungsfrequenz von 20kHz gewählt. Die Grenzfrequenz des LC-Filters wird wie folgt definiert:

Seite 32 𝑓𝑟 =

1

2𝜋√𝐿𝐶= 2

′000𝐻𝑧

Der Kondensator wird auf 14𝜇𝐹 dimensioniert, somit beträgt die tatsächliche Grenzfrequenz 2′019𝐻𝑧. 𝐶 =1 𝐿( 1 2𝜋𝑓𝑟 ) 2 = 1 444𝜇𝐻( 1 2𝜋 ∗ 2′000𝐻𝑧) 2 = 14.2𝜇𝐹 ≈ 14𝜇𝐹 𝑓𝑟__𝑟𝑒𝑎𝑙 = 1 2𝜋√𝐿𝐶= 1 2𝜋√444𝜇𝐻 ∗ 14𝜇𝐹= 2 ′019𝐻𝑧

Abbildung 25: PLECS Circuit (Leistungsschema AFE) mit Filter parallel zur Last

Das System ist wieder stabil und die Stromsollwert werden schnell erreicht. Neu sind die Phasenspannungen gefiltert und dadurch weniger gestört. Jedoch sind die Phasenströme und die generierten

Referenzspannungen nicht besser (Abbildung 26, Abbildung 27).

Somit eignet sich dieser Filter gut um die Ausgangsspannung zu filtern, aber nicht um die Stromregelung zu verbessern.

Seite 33

Abbildung 26: Phasenspannungen und Phasenströme mit Filter parallel zur Last

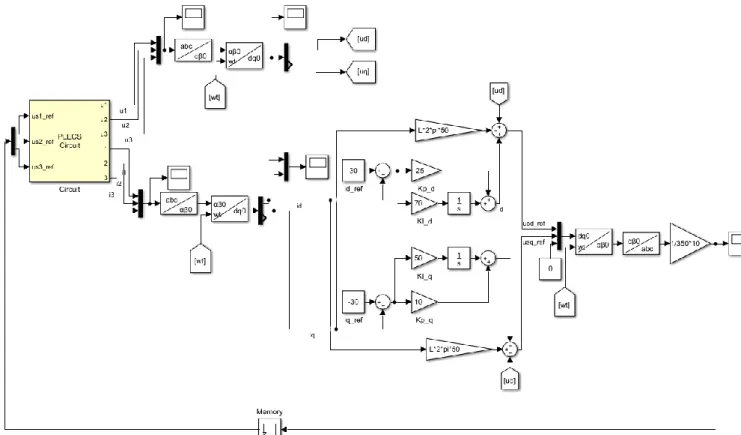

Abbildung 27: Referenzspannungen für die PWM-Generierung 5.5.3 Matlab-Funktionsblöcke (Closed-loop & Zustandsmachine)

Um sich der Struktur der C Programmiersprache weiter zu nähern, wird die Schaltung wie in Kapitel 5.5.2 Simulink-Funktionsblöcke (Stromregelung) in Matlab-Funktionsblöcke umgeschrieben. Jedoch wird in dieser Simulation die passive Last mit LC-Filter durch eine Dreiphasige Gegenspannung ersetzt (Abbildung 28, Abbildung 29). Mit einer kleinen Zustandsmaschine wird nach der Synchronisation des PLL’s auf das AC-Netz, der AFE mit dem AC-Netz verbunden.

Damit die verschiedenen Prozesse mit unterschiedlichen Geschwindigkeitsanforderungen klar unterteilt werden, werden mehrere Blöcke erstellt. Jeder Block kann mit einer anderen Abtastrate durchlaufen werden. Die Stromregelung wird in einen schnellen Block (𝑇𝑠𝑎𝑚𝑝𝑙𝑒__𝑓𝑎𝑠𝑡 = 50𝜇𝑠) integriert, weil der AFE mit 20kHz kommutiert und sich der zu regelnde Strom in den Entkopplungsinduktivitäten schnell ändert.

Weil die Zustandsmaschine nur für die verschieden Betriebszustände, den Ablauf und die Schaltung der Relais verantwortlich ist, reicht es, wenn sie mit einer Abtastrate von 𝑇𝑠𝑎𝑚𝑝𝑙𝑒__𝑠𝑙𝑜𝑤 = 1𝑚𝑠 betrieben wird.

Seite 34 Die PLL-Schaltung wird zu Beginn für Testzwecke auch mit einer langsamen Abtastrate durchlaufen

(𝑇𝑠𝑎𝑚𝑝𝑙𝑒__𝑠𝑙𝑜𝑤 = 1𝑚𝑠).

Weil die Ud- und Uq-Komponenten nach der Synchronisation des PLL’s nicht mehr schnell ändern, wird die PLL-Schaltung auch mit einer langsamen Abtastrate durchlaufen (𝑇𝑠𝑎𝑚𝑝𝑙𝑒__𝑠𝑙𝑜𝑤 = 1𝑚𝑠).

Das Matlabskript der Schaltung und der Code der Zustandsmaschine ist im Anhang 10. Die Regelparameter der PLL-Schaltung sind 𝐾𝑝= 2.0, 𝐾𝑖= 0.1 (Sample-Time ist in 𝐾𝑖 inbegriffen) und der Code befindet sich in

Anhang 10. Die Regelparameter der Stromregelung sind 𝐾𝑝__𝑖𝑑 = 𝐾𝑝__𝑖𝑞 = 6.0, 𝐾𝑖__𝑖𝑑= 𝐾𝑖__𝑖𝑞= 0.2

(Sample-Time ist in 𝐾𝑖 inbegriffen) und der Code befindet sich auch im Anhang 10. Die

Solver: (Variable-step, Auto-solver, Max step size: 1e-6, relative tolerance 1e-3)

Seite 35

Abbildung 29: Closed-Loop mit PLL-Block (slow 1ms), Zustandsmaschine-Block (slow 1ms), Stromregelung-Block (fast 50µs)

Das Resultat der PLL-Schaltung mit einer langsamen Abtastrate hat ein stabiles Verhalten und liefert nach 20ms eine konstante und stabile Frequenz (Abbildung 30). Jedoch liefert die PLL-Schaltung nur jede Millisekunde einen neuen Winkel Theta, was für die Stromregelung negative Auswirkungen mit sich bringt. Nach jeder Periode wird der Winkel Theta um 2𝜋 reduziert, um die Datengrösse der Variable nicht zu übersteigen. Es ist besser dem Winkel bei jeder Periode 2𝜋 zu subtrahieren, anstatt den Winkel auf 0.0 zu reseten. Somit wird immer genau 2𝜋 Radiant abgezogen und es entsteht kein Fehler.

Abbildung 30: Auf 0.0 geregelte Uq-Komponente, ermittelte PLL-Frequenz und ermittelter Winkel Theta

In der ersten Phase der folgenden Simulation synchronisiert sich der PLL auf das Netz und in der zweiten Phase wird die Stromregelung eingeschaltet (Abbildung 31). Das Prinzip funktioniert wieder erfolgreich, jedoch sind die Phasenströme und ihre dq-Kompenenten gegenüber dem vorherigem Kapitel gestört. Dies ist auf die langsame Berechnung des Winkels Theta zurückzuführen, welcher für die Transformationen in der Regelschlaufe benötigt wird.

Seite 36

Abbildung 31: Das Prinzip funtkioniert, jedoch enthalten die Phasenströme und ihre dq-Kompenenten Schwingungen. 5.5.4 Ergebnisse

Der DC/AC Konverter wurde im Programm PLECS-Blockset im Open Loop getestet und es wurde dessen Verhalten untersucht. Das Grundprinzip der Regelung wurde danach mit Simulink-Blöcken simuliert. Somit konnte die ganze Regelschlaufe (Transformationen, PLL, Stromregelung) im Closed Loop vereinfacht analysiert werden. Die Regler könnten gut eingestellt werden und die Regelung liefert gute Ergebnisse.

Danach wurden die Simulink-Blöcke in Matlabfunktions-Blöcke umgeschrieben und der gleiche Ablauf nochmals ausgeführt. Das ganze System funktioniert wieder. Jedoch ist das Regelverhalten leicht instabil und das System enthält Schwingungen. Es wurde festgestellt, dass ein Fehler bei der Wahl der Sample-Time des PLL-Blocks gemacht wurde. Die Schwingungen sind auf die langsame Berechnung des Winkels Theta zurückzuführen, welcher für die Transformationen in der Regelschlaufe benötigt wird.

Zusammenfassend kann bestätigt werden, dass das Prinzip der PLL-Schaltung und der Stromregelung funktioniert und dass ein Fehlverhalten festgestellt wird, wenn eine zu langsame Sample-Time für den PLL-Block gewählt wird. Deshalb werden die zukünftigen Simulationen mit Typhoon durchgeführt und das Problem mit der Sample-Time wird dort genauer untersucht.

![Abbildung 13: Komplettes Blockschema der Regelungsschleifen, [7] S.13](https://thumb-eu.123doks.com/thumbv2/123doknet/14335528.498606/23.892.106.839.84.507/abbildung-komplettes-blockschema-regelungsschleifen-s.webp)