UNIVERSITY DE

SHERBROOKE

Faculte de genie

Departement de genie electrique et genie informatique

ETUDE ET FABRICATION DE TRANSISTORS MONO-ELECTRONIQUES A

TEMPERATURE D'OPERATION ETENDUE

These de doctorat es sciences appliquees

Special ite : genie electrique

Composition du jury

Dr. Arnaud Beaumont

Dr. Jacques Beauvais

Dr. Serge Charlebois

Dr. Dominique Drouin

Dr. Abdelkader Souifi

Christian DUBUC

Sherbrooke (Quebec), CANADA

Decembre 2008

1*1

Library and

Archives Canada

Published Heritage

Branch

395 Wellington Street Ottawa ON K1A0N4 CanadaBibliotheque et

Archives Canada

Direction du

Patrimoine de I'edition

395, rue Wellington Ottawa ON K1A0N4 CanadaYour file Votre reference ISBN: 978-0-494-48545-3 Our file Notre reference ISBN: 978-0-494-48545-3

NOTICE:

The author has granted a

non-exclusive license allowing Library

and Archives Canada to reproduce,

publish, archive, preserve, conserve,

communicate to the public by

telecommunication or on the Internet,

loan, distribute and sell theses

worldwide, for commercial or

non-commercial purposes, in microform,

paper, electronic and/or any other

formats.

AVIS:

L'auteur a accorde une licence non exclusive

permettant a la Bibliotheque et Archives

Canada de reproduire, publier, archiver,

sauvegarder, conserver, transmettre au public

par telecommunication ou par Plntemet, prefer,

distribuer et vendre des theses partout dans

le monde, a des fins commerciales ou autres,

sur support microforme, papier, electronique

et/ou autres formats.

The author retains copyright

ownership and moral rights in

this thesis. Neither the thesis

nor substantial extracts from it

may be printed or otherwise

reproduced without the author's

permission.

L'auteur conserve la propriete du droit d'auteur

et des droits moraux qui protege cette these.

Ni la these ni des extraits substantiels de

celle-ci ne doivent etre imprimes ou autrement

reproduits sans son autorisation.

In compliance with the Canadian

Privacy Act some supporting

forms may have been removed

from this thesis.

Conformement a la loi canadienne

sur la protection de la vie privee,

quelques formulaires secondaires

ont ete enleves de cette these.

While these forms may be included

in the document page count,

their removal does not represent

any loss of content from the

thesis.

Canada

Bien que ces formulaires

aient inclus dans la pagination,

il n'y aura aucun contenu manquant.

"The potential for single-electronics is no longer a

question of physics but of fabrication."

- Christoph Wasshuber

SOMMAIRE

Ce travail porte sur le developpement d'un procede de fabrication de transistor

mono-electronique {single-electron transistor, SET). II dresse un portrait de l'etat de Part actuel et

met en lumiere un manque dramatique de marge d'operation dans le fonctionnement de ces

dispositifs. Cette problematique est presentee comme une des limites majeures aux espoirs de

developpement commercial de cette technologie. La these propose d'aller chercher la marge de

manoeuvre manquante par un procede de fabrication qui exploite le controle des dimensions

verticales des dispositifs. Les resultats montreront que si les approches actuelles 2D semblent

avoir atteint leurs limites physiques, l'approche 3D permet d'acceder a des temperatures

d'operation encore insoupconnees jusqu'a present. L'impact est important, puisqu'une analyse

de la these conclura que, raerae en tenant compte des pires fluctuations du procede de

fabrication, les SETs issus du concept 3D conservent une marge d'operation appreciable. La

gamme de temperature d'operation obtenue est semblable aux transistors a effet de champ

conventionnels (field effect transistor, FET) et on peut penser qu'il serait ainsi possible

d'utiliser les deux technologies simultanement sur un meme substrat afin de creer de nouvelles

fonctionnalites issues de cette technologie hybride SET/FET.

Mots-cles: transistor, mono-electronique, temperature d'operation, nanotechnologie,

REMERCIEMENTS

Je tiens a remercier mes co-directeurs, les professeurs Jacques Beauvais et Dominique

Drouin. En me proposant cette grande aventure, ils m'ont permis non seulement d'explorer un

sujet fascinant, mais aussi d'aller decouvrir des ressources personnelles encore insoupconnees.

Je leur suis reconnaissant de m'avoir fait cheminer dans le monde de la recherche et je

m'incline devant autant de patience.

Je remercie egalement la formidable equipe du CRN . En s'efforcant de maintenir un

laboratoire securitaire et efficace, elle m'a permis d'evoluer dans les meilleures conditions.

Merci a Jean Beerens pour ces innombrables depannages, aux techniciens et techniciennes

(Caroline Roy, Guillaume Bertrand, Pierre Lafrance et ceux et celles que j'oublie) pour leur

support professionnel.

Une these n'etant pas une these sans de nombreuses discussions de corridors, je

remercie les philosophes qui m'ont epaule : Arnaud Beaumont en particulier, Serge Charlebois,

Etienne Grondin, Vincent Aimez et tous les autres.

Merci enfin a ma famille, avec laquelle je n'ai pas toujours pu passer assez de temps.

Merci a Nancy, Emile et Aurelie pour leurs eternels encouragements.

II y a souvent des hauts et des bas, mais, tout comme le courant de drain d'un SET, ces

oscillations sont positives et nous font progresser.

TABLE DES MATIERES

CHAPITRE 1 : INTRODUCTION 1

CHAPITRE 2 : ASPECTS THEORIQUES DE LA CONCEPTION DES SETS 9

2.1 La physique de base du SET 9

2.2 Revue de l'etat de l'art 19

2.3 Cahier des charges 28

2.4 Choix du concept 32

2.5 Choix technologiques 33

CHAPITRE 3 : DESCRIPTION DU PROCEDE DE FABRICATION 39

3.1 Survol du procede de fabrication 39

3.2 Etude des parametres de fabrication 50

CHAPITRE 4 : MODELISATION DES DISPOSITIFS 70

4.1 Role de la modelisation 70

4.2 Etablissement des parametres physiques des jonctions 71

4.3 Modelisation a haute temperature pour SETs 76

4.4 Plage de validite de la modelisation orthodoxe a haute temperature 96

CHAPITRE 5 : MARGE D'OPERATION ET AMELIORATIONS POSSIBLES 97

5.1 Temperature maximale d'operation 97

5.2 Optimisation de la marge d'operation 99

5.3 Limites ultimes du procede 106

5.4 Ameliorations possibles et integration CMOS 107

CONCLUSION 118

ANNEXE A 122

LISTE DES ABREVIATIONS

BER : Bit Error Rate, pour taux d'erreur de bit

CMP : Chemical Mechanical Polishing, pour polissage mecanique-chimique

EBL : Electron Beam Lithography, pour lithographie par faisceau d'electrons

FET : Field Effect Transistor, pour transistor a effet de champ

ITRS : International Technology Roadmap for Semiconductors, pour plan strategique

international pour le developpement de semi-conducteurs.

MTJ : Multiple Tunneling Junction, pour jonctions multiples a effet tunnel

RIE : Reactive Ion Etching, pour gravure par ions reactifs

SET : Single Electron Transistor, pour transistor mono-electronique a electrons

SHT : Single Hole Transistor, pour transistor mono-electronique a trous

SOI: Silicon On Insulator, pour silicium sur isolant

LISTE DES FIGURES

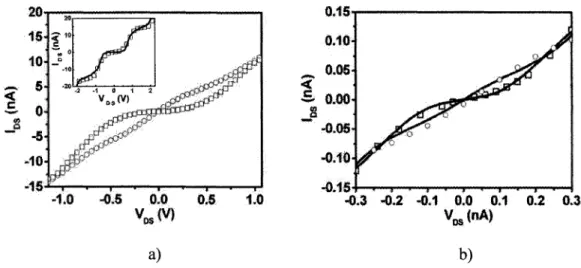

Figure 2.1 a) Representation d'un SET a couplage capacitif et b) sa version schematique 9 Figure 2.2 a) Exemple de courbe de reference IDS-VDS en blocage de Coulomb a temperature Ti b) la meme courbe avec 0.5e charge induite sur Pilot par l'effet de la grille et c) la courbe de reference a temperature T2 » Ti. d) Exemple de courbe de reference IDS-VGS (VDS ~ 0 V) a

temperature Ti = 6xlO"4Ec e) a T2 = 0.2EC et f) a T3 = 0.3Ec 16

Figure 2.3 a) Diagramme des bandes d'energie en blocage de Coulomb pour un SET

metallique (niveau de Fermi dans la bande de conduction), b) Alignement des bandes d'energie

lorsque VDs > VTH favorisant la conduction par effet tunnel de la source au drain 17

Figure 2.4 a) Diagramme a carreaux. Les nombres dans les carreaux montrent Petat de charge

de Pilot. Les nombres separes par une virgule illustrent une transition successive d'etat, b) Un

exemple d'extraction possible de parametres du SET a partir du diagramme a carreaux 18

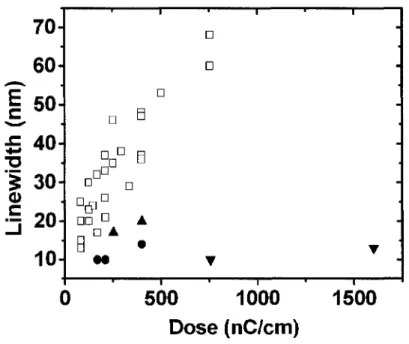

Figure 2.5 La methode d'evaporation a angle de Dolan 21 Figure 2.6 La methode d'oxydation locale de fil de silicium 26 Figure 2.7 La methode de CMP communement appelee damascene 34

Figure 4.1 Graphique d'emission Schottky selon Ln(J/T2) vs E1/2 a 336 K 73

Figure 4.2 Donnees en mode Fowler-Nordheim selon ln(J/E2) vs 1/E a 300K 74

Figure 4.3 Graphique de ®o vs m obtenu en combinant les equations 4.2 et 4.4 75 Figure 5.1 Evolution de la conductance d'un SET en fonction de la temperature

(VDs=100mV) 98

Figure 5.2 Evolution de Ec avec le parametre LiSiand pour des SETs avec grille arriere

{back-gate) 101 Figure 5.3 Distribution des temperatures maximales d'operation selon la variation aleatoire des

parametres du tableau 5.1 avec un controle de 5 % (noir), 10 % (blanc), 20 % (gris) et 30 %

(barres obliques) 104

Figure 5.4 Approche proposee pour la fabrication d'une grille de surface. DQ represente la

distance entre Pilot du SET et la grille 108

Figure 5.5 Vue geometrique des differentes capacitances constituants CG : a) Ci, b) C2 et c) C3.

Figure 5.6 Prototype preliminaire de grille de surface. W

G= 2 um approximativement 112

Figure 5.7 Integration des SETs a un precede CMOS. On reconnait les etapes de fabrication du

SET de b) a e) qui sont les seules deviations des etapes CMOS standards a) et f) 115

Figure 5.8 Integration des SETs a un precede CMOS. Etapes usuelles du precede CMOS :

g)-h) lithographie et gravure des contacts, i) depot de la barriere, j) remplissage des contacts et k)

LISTE DES TABLEAUX

Tableau 2.1 Aper9u des valeurs de capacitance d'ilot selon Likharev 23

Tableau 2.2 Resume du cahier des charges 32

Tableau 2.3 Resume du concept de SET retenu 33

Tableau 2.4 Resume des choix technologiques 38

Tableau 4.1 Resume des caracteristiques physiques du systeme Ti/TiOx

76

Tableau 5.1 Les etapes critiques du precede nanodamascene 100

Tableau 5.2 Sommaire des effets de trois methodes pour augmenter Tmax

105

Tableau 5.3 Calcul estimatif de la capacitance CG de la grille de surface 111

Tableau 5.4 Evaluation numerique de CG selon differentes approches 112

CHAPITRE 1 : INTRODUCTION

La presente these porte sur l'etude et la fabrication de transistors mono-electroniques

{Single-Electron Transistor, SET) demontrant une grande marge de temperature d'operation. La

marge d'operation chez le SET est une caracteristique fondamentale de celui-ci et ce, pour deux

raisons. D'abord, parce que la physique qui sous-tend le fonctionnement des SETs fait en sorte

qu'ils sont tres sensibles a leur procede de fabrication, ce qui influence de facon notable leur

marge d'operation. Ensuite, parce que, comme pour la plupart des transistors et autres

dispositifs electroniques, l'obtention d'une marge d'operation valable est un critere

incontournable qui decide de la viabilite commerciale du produit. Cet etat de fait sera mis en

evidence dans les paragraphes qui suivent, apres avoir effectue une courte retrospective.

L'historique et le developpement du SET, de meme que le role qu'il pourrait etre appele

a jouer dans un proche futur, invitent a la comparaison avec son equivalent traditionnel: le

transistor a effet de champ {Field Effect Transistor, FET). Pour ce dernier, il s'est ecoule pres

de 20 ans entre les premiers brevets de principes [Lilienfeld, 1930] et l'annonce d'une

fabrication reussie en laboratoire par Bell Labs en 1948. Ce delai fut generalement attribue au

manque de moyens techniques permettant la fabrication d'un prototype. La premiere

commercialisation du transistor, generalement attribue a la division Regency de la compagnie

Idea, eut lieu en 1954, soit environ cinq ans apres le premier prototype. Ce fut le debut d'une

On peut identifier les premiers balbutiements de la science mono-electronique aux

premieres interrogations portant sur les augmentations de resistance dans les films granulaires

tres minces [Gorter, 1951]. Cette piste s'est poursuivie pendant dix ans [Landauer, 1962], puis

25 [Kulik et coll., 1975], jusqu'a Penonce, 35 ans plus tard [Averin et coll., 1986], du concept

de conduction mono-electronique par effet tunnel (single-electron tunneling), tel qu'on le

connait aujourd'hui. La premiere observation experimentale de ce mecanisme de conduction

eut lieu a peu pres au meme moment [Averin et coll., 1985; Fulton et coll., 1987]. Jusqu'a ce

stade, on peut pretendre que les routes des SETs et des FETs ont ete semblables et peu

differentes des autres domaines de la science, souvent compliquees par une technologie encore

trop primitive. Cet etat de fait etait d'autant plus evident dans le domaine de la

mono-electronique, a cause des tres faibles dimensions des dispositifs a fabriquer. Les futurs

paragraphes et chapitres montreront en effet qu'il fallait, au debut des travaux sur les SETs,

gerer a la fois des dimensions sous-microniques et des temperatures cryogeniques, ce qui en

faisait un domaine techniquement tres complexe. Ce lien qui fait en sorte que le SET doit etre

de petite dimension pour pouvoir augmenter sa temperature d'operation represente un theme

important de cette these et sera detaille intensivement dans les pages qui suivent. II faut done

souligner que les premiers SETs etaient essentiellement des dispositifs cryogeniques et que les

premieres demonstrations d'operation a temperature ambiante (300 K) ne sont apparues que

vers la fin des annees 90 [voir par exemple, Takahashi et coll., 1995]. On peut ici percevoir une

cassure entre revolution rapide du FET, du laboratoire vers la commercialisation, et

l'historique du SET. II aura fallu seulement cinq ans au FET pour etre fabrique a la chaine,

alors qu'aujourd'hui, 20 ans apres le premier prototype, la vie commerciale du SET n'est

facteurs qui freinent Ie developpement des SETs.

II faut, a ce stade, se rememorer les etapes typiques du cycle de vie d'un dispositif

electronique. D'une idee, de laquelle suit generalement un prototype, on prouve le concept.

Ensuite, les caracterisations physiques et electriques etablissent les marges d'operation. Puis, la

fabrication de petits lots de dispositifs apporte les premieres statistiques qui mesurent le

rendement du procede. Suivent ensuite les tests de fiabilite, la mise en production et

eventuellement, le declin et le remplacement du produit. En revenant sur une base historique,

on s'apercoit que le cheminement du SET a ete a peu pres standard jusqu'a la demonstration du

prototype. II s'est produit par la suite une fracture ou les marges d'operation n'ont pas ete

etablies. Les methodes de fabrication, trop lentes et peu repetables, ont fait en sorte qu'un

volume insuffisant de SETs a ete produit, annulant du meme coup l'analyse statistique des

rendements de fabrication. Sans avoir franchi ces etapes essentielles, on comprend mieux

pourquoi le SET n'a pu quitter le laboratoire comme l'a si bien fait le FET. Le danger qui

guette maintenant le SET est un desinteressement naturel de la part de la communaute

scientifique, phenomene qui survient bien souvent quand une technologie tarde trop pour percer

et s'etablir clairement dans un creneau du marche. Dans ce cas precis, on assiste souvent a une

baisse du nombre d'articles publies dans le domaine et done, a un ralentissement encore plus

marque dans la progression du cycle de vie mentionne precedemment. II est, en ce sens,

legitime de se demander si e'est vraiment ce qui attend le SET.

La piste d'une reponse a cette question se trouve dans le contexte humain du

developpement du SET. II faut se souvenir qu'a Pepoque ou le SET a pris son envoi, un vent

d'enthousiasme soufflait sur ce nouveau dispositif qui promettait de declencher la nouvelle

revolution du transistor. La reduction d'echelle des FETs, qui portait a elle seule la majeure

partie du progres technologique en micro-electronique depuis 20 ans, commencait a

s'essouffler quelque peu. Chaque nouvelle generation, plus petite en taille, apportait avec elle

son lot de problemes, de la trop grande consommation d'energie aux fuites d'oxyde de grille,

en passant par les capacites parasites des interconnections. Les theoriciens faisaient meme

planer le spectre d'effets quantiques indesirables dans le canal, a mesure que le nombre

d'electrons y diminuait. Le SET se presentait done en sauveur et promettait de regler tous ces

problemes en meme temps. II s'agissait d'un dispositif qui utilisait les phenomenes quantiques

de conduction a son avantage, qui consommait tres peu d'energie et qui semblait fonctionner de

mieux en mieux si on en diminuait la taille. Les rejouissances furent toutefois de courte duree

et une certaine deception commenca a s'installer dans la decennie suivant la presentation du

SET en 1987. Certes, la temperature d'operation allait passer de quelques milli Kelvin a celle

de P azote liquide, puis a la temperature ambiante. De plus, la theorie se raffina et on crea des

modeles et des simulateurs pour aider le design de circuits complexes. Mais, ces dix annees

exposerent aussi de nouvelles limites. La principale concerne Putilisation du SET pour

remplacer totalement le FET dans une famille equivalents de logique mono-electronique a etat

de voltage. On a realise assez tot que le SET, pour localiser ses electrons sur son ilot, a besoin

de resistances de jonction superieures a environ 25 kOhms, ce qui equivaut a des constantes de

temps RC elevees, resultant en un dispositif, somme toute, assez lent. De plus, le gain des SETs

est relativement faible et leur hypersensibilite aux charges environnantes {background charges)

fait en sorte que leur tension de seuil varie beaucoup dans le temps, et d'un dispositif a l'autre.

pour les circuits numeriques conventionnels a etat de voltage. Qui plus est, les quelques succes

accumules par les SETs dans la decennie concernaient des standards de courant ou des

voltmetres ultra-sensibles, ce qui etait per9u comme des niches beaucoup trop specialises pour

obtenir un facteur d'impact perceptible. On a done reoriente le SET vers un domaine ou il

pourrait exceller de par ses faibles dimensions et de par la possibilite de Putiliser en extreme

haute densite : les circuits de memoire. Tres tot, des architectures sont apparues pour proposer

des circuits insensibles aux charges parasites et ou le gain et la vitesse ne sont plus des facteurs

limitants. Les circuits de memoire sont done un champ prometteur pour les SETs, mais encore

une fois, la fabrication n'est encore qu'au stade de prototypage. On ne peut done dire

precisement si la cadence de developpement du SET a ralenti depuis les dix dernieres annees,

car le travail s'est passablement reoriente. Certains pourraient cependant etre en droit de se

demander si le futur des SETs se resumera seulement en des circuits de memoire.

La reponse a cette question est: probablement non. On sent en effet, depuis quelques

annees, un regain de recherche vers d'autres architectures, surtout depuis que Ton s'est resigne

a ne pas remplacer completement les FETs par des SETs. En effet, plusieurs groupes de

recherche ont convenu qu'une approche hybride, combinant les deux technologies SET et FET

sur un meme substrat, pourrait procurer non seulement des fonctionnalites utiles et innovatrices

[voir par exemple Nishiguchi et coll., 2006; Uchida et coll., 2003], mais aussi une transition

plus graduelle vers une nouvelle generation de nanocircuits. Cette architecture n'evitera

cependant pas au SET son passage oblige vers le cycle mentionne precedemment, notamment

en ce qui a trait a l'etablissement d'une marge d'operation. Ce dernier point, d'une importance

de la marge d'operation des SETs est vue dans cette these comme le prochain defi a relever

pour prouver que le SET peut encore etre un dispositif commercialement viable. Les questions

de volume de fabrication, de rendement et de fiabilite sont importantes, mais la marge

d'operation revet un caractere special a cause d'une caracteristique particuliere du SET,

discutee au paragraphe suivant.

Le concept d'energie de charge du SET sera defini au chapitre suivant. Disons

simplement, pour le moment, que pour observer un effet transistor, le SET doit posseder une

energie de charge superieure aux fluctuations thermiques de son environnement. Or, cette

energie de charge est fortement liee au procede de fabrication, car chaque deviation d'une etape

du procede peut entrainer une augmentation de la capacitance totale du SET, et done, une

reduction de son energie de charge. En bref, une deviation de procede a un effet different sur un

FET que sur un SET. Une augmentation de capacitance peut faire devier le comportement d'un

FET, mais elle fait diminuer la temperature d'operation du SET jusqu'a un point ou l'on ne

peut plus observer d'effet transistor. Si on croit que l'approche hybride FET/SET est une voie

serieuse pour le futur, il faut done, pour la soutenir, proposer un concept de SET ayant des

proprietes tres strictes. Tout d'abord, il faut que le SET partage des materiaux et des techniques

de fabrication compatibles avec les FETs et avec les precedes de haut volume des lignes de

fabrication au silicium qui sont deja en place. Ensuite, et il s'agit sans doute du point le plus

important, il faut que le SET possede une marge d'operation compatible avec le FET. Pour le

SET, cette marge concerne la temperature minimale d'operation. Un concept prometteur de

SET doit etre en mesure de permettre les deviations normales et inevitables des cibles des

etapes de fabrication du dispositif, tout en garantissant une temperature d'utilisation minimale

compatible avec le FET. C'est ce concept que proposera cette these.

Les objectifs poursuivis dans ce travail s'exposent en trois parties. D'abord, il faudra

definir un concept de SET qui sache repondre au cahier des charges du projet et il faudra

ensuite faire la preuve du concept en fabriquant quelques dispositifs. Ce cahier des charges fera

Pobjet d'une section importante de cette these. Deuxiemement, il faudra que les prototypes

permettent d'observer un effet transistor et done, que leur energie de charge Ec so it superieure

aux fluctuations thermiques keT de l'environnement. 11 faudra que la caracterisation des

prototypes permettent de quantifier cette condition, a savoir trouver x dans 1'equation

Ec > xkeT. Enfin, il sera necessaire de quantifier la marge de manoeuvre de ce concept de SET

en termes de temperature minimale d'operation. Cette temperature devra supporter un scenario

severe de deviations de parametres de fabrication et rester compatible avec le domaine

d'operation des FETs.

D'entree de jeu, il est clair que ces objectifs demanderont des solutions de fabrication

radicalement innovatrices. Degager une marge d'operation demandera une approche qui devra

augmenter le controle sur les dimensions du SET. II sera demontre dans cette these que la cle

pour y arriver residera dans un controle tridimensionnel de l'espace du SET, jusqu'ici utilise

dans un espace bidimensionnel seulement.

Les pages qui suivent sont organisees en quatre chapitres qui survolent les etapes

chronologiques du travail fait en laboratoire. Dans la premiere partie (qui couvre les deux

premiers chapitres), le cahier des charges sera etabli et un bref survol des aspects theoriques

guidant ces specifications sera expose. Cette partie est importante puisqu'elle comportera des

reflexions sur les precedes existants et elle remettra en question certaines methodes et criteres

largement utilises depuis les dernieres annees. Suivra ensuite la presentation du precede de

fabrication. Cette partie contiendra les details des etapes du precede de fabrication propose.

Bien que plus mecanique, cette section n'en presentera pas moins les innovations majeures

responsables des performances des dispositifs proposes. La deuxieme demie du travail

englobera les deux derniers chapitres ou des dispositifs seront constants et ou des resultats

experimentaux seront disponibles. Aussi, les caracterisations y seront analysees en fonction du

cahier de charges. Le dernier chapitre presentera des ajustements ou des ameliorations a

envisager pour progresser vers la prochaine etape du cycle de vie des dispositifs, soit Panalyse

statistique du rendement du precede. Dans cette partie du travail, il faudra simuler des

deviations de precedes. II faudra egalement calculer si les SETs developpes dans cette these, et

qui subissent ces fluctuations, peuvent encore fonctionner dans une gamme de temperatures

compatibles avec les FETs. Ces simulations ameneront des conclusions cruciales dans ce

travail. Elles devront etres basees sur des donnees experimentales obtenues a des temperatures

au-dessus de 300 K. Les resultats de cette demarche meneront logiquement a une conclusion ou

la cohesion des aboutissements des chapitres sera analysee, afin d'en degager une voie

principale qui pourra resumer l'ensemble du travail de cette these.

CHAPITRE 2 : ASPECTS THEORIQUES DE LA CONCEPTION DES SETS

2.1 La physique de base du SET

La physique qui explique le comportement des SETs est connue depuis plusieurs annees

deja. Tout lecteur desirant connaitre l'origine exacte de la derivation des equations directrices

peut maintenant avoir acces a plusieurs livres de reference [Grabert et coll., 1992; Wasshuber,

2001 ; Averin et coll., 1991b]. II faut cependant, dans ce chapitre, rappeler la physique de base

des SETs, car ces principes seront repris tout au long du travail. lis se doivent done d'etre

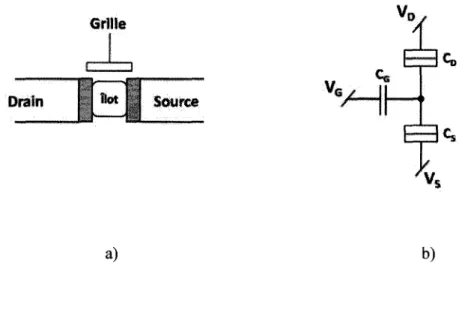

etablis clairement au depart. La figure 2.1 montre une representation d'un SET a couplage

capacitif. Les SETs a couplage resistif ne seront pas traites dans ce travail. Les

Grille

x

r ~ l r DrainV

6i/ II L

tI

\%a) b)

SETs a couplage capacitif sont constitues des memes trois electrodes que les FETs, a savoir la

source, le drain et la grille. Un ilot central conducteur est situe entre la source et le drain. II est

isole de ceux-ci par une mince couche dielectrique qui agit comme jonction a effet tunnel. Sous

certaines conditions, des porteurs peuvent done traverser ces barrieres d'energie de la source a

Pilot, puis de Pilot au drain, assurant ainsi un courant appele courant de drain (IDS)- La troisieme electrode, la grille, est situee pres de Pilot et y est separee par une couche dielectrique

isolante. La grille influence Petat du dispositif en induisant des charges sur Pilot central. On

dira que Pilot et les electrodes forment en fait un systeme a trois capacitances : la capacitance

de source (Cs), la capacitance de drain (Co) et la capacitance de grille (CG). A cela, peut

s'ajouter, dans certains cas, une capacitance parasite distribute Co (stray capacitance). La

somme de ces capacitances represente la capacitance totale CT du SET. Lorsque Pilot est

electriquement neutre a sa surface, il est facile d'y apporter un electron par la source. Avec un

electron en surplus, Pilot montre une charge nette de -e oil e est une charge elementaire de

1.6xl0"19 C. Quoique petite a Pechelle humaine, cette charge n'en cree pas moins un tres fort

champ electrique. En fait, ce champ depend inversement de la surface de Pilot au carre

(application directe du theoreme de Gauss). Si les dimensions de Pilot sont de Pordre de

quelques nanometres, le champ resultant est de plusieurs centaines de kilovolts par centimetre.

Ce champ est alors amplement suffisant pour repousser toute tentative d'ajouter un autre

electron a Pilot. C'est en quelque sorte cette force qui permet au SET d'agir comme

interrupteur de courant (transistor). II y parvient en bloquant les porteurs qui pourraient

traverser sur Pilot par effet tunnel. Bien qu'intuitive, cette facon de mesurer la capacite de

blocage du SET n'est pas pratique. II faut plutot voir Pilot comme une capacitance que Pon

qu'aurait a fournir une source externe pour charger le systeme est:

Ec = e2/ CT (2-1)

II faut souligner ici que la litterature emploie souvent Ec/2 comme energie de charge, entite qui

constitue en fait Penergie de charge classique d'une capacitance a plaques paralleles. II faut

done etre prudent dans la comparaison des energies de charge faite entre differentes etudes qui

font usage de l'une ou l'autre de ces valeurs de Ec sans plus de formalites.

II sera important de garder a l'esprit certains facteurs d'echelle tout au long des

discussions sur les SETs. Les lois physiques qui decriront le comportement du SET dependront

de l'ordre de grandeur de la taille de Pilot central de celui-ci. L'apparition de niveaux discrets

d'energie est possible chez un SET (voir exemple de calculs a PAnnexe A). On appelle parfois

ces SETs point quantique {quantum dot) ou atome artificiel. Dans ce cas particulier, on emploie

habituellement la notion d'energie d'addition EA pour decrire Penergie de charge de Pilot.

Dans la plupart des cas, on fait Papproximation :

EA = EC + EK (2-2)

En ce qui a trait aux cas qui nous interessent, Penergie cinetique quantique EK de Pelectron

ajoute a Pilot est celle d'un gaz d'electrons degenere. Ici, l'expression gaz degenere veut dire

que Pon s'attend a ce que la temperature d'utilisation des SETs soit de beaucoup inferieure a la

=

h

!( 3

2 !n ) !

t

2m

v'

ou h est la constante de Planck reduite, m est la masse des electrons et n est la densite des

electrons. L'energie EK est donnee par :

E

K = , \ (

2-

4)

ou V est le volume de Pilot et g(eF) est la densite d'etats sur la surface de Fermi. On reconnaitra

que E

Kvarie selon l'inverse de la densite d'etat, ce qui represente en fait la difference d'energie

entre deux etats voisins. Cette valeur est souvent appelee energie de separation {energy

splitting) dans la litterature et est denotee AE. II ne faudra done pas s'etonner de rencontrer

l'equation 2-2 sous la forme EA = Ec + AE. Notons que Pequation 2-4 deviendra importante

lors de la discussion sur les SETs metalliques et sur les SETs semi-conducteurs, a cause des

differences de densite d'etat entre ces deux types de materiaux.

Afin de poursuivre le survol de la physique du SET, il faut a present proceder a

quelques hypotheses simplificatrices. 11 faut tout d'abord ignorer pour le moment la

discretisation des niveaux d'energie. Dans ce cas, on assume que Ec » EK, ce qui simplifiera

l'analyse du taux de l'effet tunnel discute plus loin. Ensuite, on ignorera les phenomenes de

transport coherent et simultane de plus d'un electron (cotunneling) a travers les barrieres. Cette

hypothese est a peu pres exacte si la resistance RT des jonctions du SET est superieure a un

quanta de resistance. Pour les cas non-supraconducteurs, on aura :

R

T» h / e

2~ 2 5 . 8 k O h m s (2-5)

Cette derniere equation est importante. Elle peut etre interpretee comme le niveau « d'opacite »

de jonction necessaire pour localiser les porteurs sur un Hot particulier a un instant particulier,

condition necessaire au fonctionnement du SET. Cette condition supprime done 1'incertitude

quantique de la position des electrons. C'est pour cette raison que les SETs ne peuvent pas, a

proprement parler, etre consideres comme des dispositifs electroniques quantiques {quantum

electronic device).

Les simplifications presentees au paragraphe precedent sont a la base d'une theorie

appelee theorie orthodoxe, presentee pour un cas particulier d'abord [Kulik et coll., 1975], puis

generalised ensuite aux SETs [Averin et coll., 1991b]. La conclusion fondamentale de la theorie

orthodoxe se rapporte au taux de l'effet tunnel sur Pilot d'un SET : il y aura effet tunnel si le

saut d'un electron sur Pilot diminue Penergie e

2/C

Tdu systeme. Comme il est facile de calculer

Petat d'energie d'un systeme avant et apres une hypothetique conduction par effet tunnel, il est

done possible de determiner a Pavance si de telles conductions seront favorisees ou non. A

partir de ce principe inclus dans une structure de Monte Carlo, des simulateurs de SETs ont ete

crees. Ces derniers expliquent quantitativement les resultats de SETs metalliques et donnent un

bon apercu qualitatif du comportement des SETs semi-conducteurs. II etait necessaire de

presenter ici ces simplifications, car elles seront souvent sous-entendues dans les chapitres

suivants lorsqu'il sera question d'analyse selon le cadre de la theorie orthodoxe.

Les calculs qui determineront si un effet tunnel est favorable ou non au bilan

energetique du SET se font souvent avec des valeurs de charge fractionnaire sur Pilot. II ne

faudra pas s'etonner de rencontrer des fractions de charge elementaire dans P etude des SETs,

meme si les theories des livres de reference ont etabli depuis longtemps que e est la plus petite

charge discrete possible. Ceci s'explique par le fait qu'en science mono-electronique, on parle

plutot de charge transferee que de bilan de charge nette absolue. Cette charge transferee peut

prendre n'importe quelle valeur continue. Les jonctions tunnel des SETs peuvent etre vues

comme une barriere d'energie qui bloque la conduction libre des porteurs provenant de la

source ou du drain. Le nombre d'electrons qui s'accumule a la jonction peut prendre n'importe

quelle valeur, puisque que celui-ci est proportionnel a la tension appliquee a la jonction. Le

volume pres de la jonction est done occupe par un nuage de charges decentralisees formant en

fait une sorte de dipole electrique. Lorsqu'on analyse le nombre d'electrons dans ce volume par

rapport aux atomes fixes positifs de Pelectrode, on concoit que ce rapport peut effectivement

prendre la forme d'une charge nette fractionnaire quelconque. C'est cette charge qui est appelee

charge transferee et c'est celle-ci qui est utilisee pour calculer l'energie electrostatique du

systeme. Cette energie sera utilisee pour determiner le taux de transfer! des electrons par effet

tunnel. On comprendra mieux alors que « transistor mono-electronique » ne veut pas dire qu'il

n'y a qu'un seul electron sur Pilot du SET. II s'agit plutot d'un dispositif mettant en lumiere

1'effet que peut avoir Pajout d'une seule charge elementaire sur un Tlot qui peut toutefois en

Cette section a etabli la majorite des concepts qui guideront les calculs de conception du

SET. II faut cependant ajouter ici une derniere condition tres importante a l'observation des

SETs. II faut, en effet, garantir que les fluctuations thermiques ne viendront pas bouleverser

l'ordre et le nombre d'electrons sur Pilot du SET. II faut que Penergie d'addition soit

dominante selon:

EA » kBT (2-6)

ou ke est la constante de Boltzmann et T, la temperature du systeme. La determination d'un

ratio EA / kBT utile sera tres important dans cette these pour poser d'autres hypotheses,

notamment sur la marge d'operation des SETs a P etude. La litterature essaie souvent de fixer

une valeur x a ce ratio selon :

x = EA/ (toT) (2-7)

La plupart des travaux sur les SETs enoncent les equations 2-5 et 2-6 comme etant les deux

conditions necessaires a l'observation de Peffet transistor chez un SET.

Les SETs peuvent etres polarises de plusieurs facons. Dans le cas d'une utilisation en

source commune, la grille agit comme Pelectrode qui controle le courant de drain. La theorie

orthodoxe prevoit en effet que seulement certaines valeurs de tensions de grille placent le

trouve en blocage de Coulomb (Coulomb blockade). Ce blocage survient quand la charge de a)

4

b)A

c) d) e) t)Figure 2.2 a) Exemple de courbe de reference IDS-VDS en blocage de Coulomb a temperature T] b) la meme courbe avec 0.5e charge induite sur Pilot par l'effet de la grille et c) la courbe de reference a temperature T2 » TV d) Exemple de courbe de reference IDs-VGs (VDS ~ 0 V) a

temperature Ti = 6xlO~4Ec e) a T2 = 0.2EC et f) a T3 = 0.3Ec.

Pilot Q est -ell < Q < ell. Dans ce cas, tout effet tunnel sur Pilot n'est pas favorable, puisqu'il

augmenterait Penergie totale du systeme. La figure 2.2 montre les courbes typiques IDS-VDS et IDS-VGS de tels SETs.

La figure 2.2a montre le blocage de Coulomb ou aucun courant de drain ne circule sur

tension de seuil

(VTH),les bandes d'energie sont suffisamment abaissees pour rendre favorable

<Po

source M o t 111 drain source Tlot Wm- drain

a)

b)

Figure 2.3 a) Diagramme des bandes d'energie en blocage de Coulomb pour un SET

metallique (niveau de Fermi dans la bande de conduction), b) Alignement des bandes

d'energie lorsque VDS > VTH favorisant la conduction par effet tunnel de la source au

drain.

une circulation de courant (voir figure 2.3). La pente de la courbe

IDS-VDStend alors vers la

valeur de la resistance de jonction totale du SET. Lorsqu'une charge e(n+l/2) avec

n= ... -2, -1, 0, 1, 2, ... est induite sur Pilot, la theorie orthodoxe prevoit que le blocage de

Coulomb est totalement supprime (figure 2.2b). On considere alors le SET en mode de

conduction (ON mode). L'augmentation de la temperature montree a la figure 2.2c peut aussi

annuler le blocage de Coulomb, d'ou Pimportance de l'equation 2-6. La courbe

IDS-VGSmontree (figure 2.2d a faible VDS) represente bien le caractere periodique que provoque la

tension de grille. La tension VGS induit tour a tour sur Pilot des etats de charge qui favorisent

ou non la conduction par effet tunnel, selon une periode e/Co- Les figures 2.2e et 2.2f exposent

P effet destructif de la temperature sur les oscillations du courant de drain.

Une representation exposant a la fois les courbes IDS-VDS et IDS-VGS sur un meme graphique est parfois employee. II s'agit des diagrammes en carreaux (diamond plot) ou

diagrammes de stabilite (stability plot) qui utilisent differents tons de couleur proportionnels a

IDS (OU parfois a dIDs/dVDs) pour chaque combinaison des coordonnees des abscisses (VGS) et

des ordonnees (VDS). Ce graphique necessite la prise de beaucoup de mesures, mais peut servir a extraire plusieurs parametres, une fois termine. Un exemple est montre a la figure 2.4.

vD(v) ValeurdedJ/dl/ 5 a) T MS 10 4 ^ ^ • ( 1 / C j + l / Q + l/Co) e/Q* (1/2-Q/CJ b)

Figure 2.4 a) Diagramme a carreaux. Les nombres dans les carreaux montrent l'etat de

charge de l'ilot. Les nombres separes par une virgule illustrent une transition successive d'etat, b) Un exemple d'extraction possible de parametres du SET a partir du diagramme a carreaux.

II faut noter au passage une subtilite dans la polarisation du SET. On dira qu'elle est

directement au drain. La polarisation sera symetrique quand une tension Vi de V

Ds/2 sera

appliquee au drain et qu'une tension V2 de

-VDS/2sera appliquee a la source. L'effet principal

de la polarisation symetrique est qu'elle permet d'appliquer le meme champ electrique sur les

jonctions de drain et de source, peu importe la charge sur l'ilot. En pratique, Putilisation de la

polarisation symetrique dans un circuit utile necessite la creation de deux sources de

polarisation differentes ce qui n'est pas toujours commode. Le type de polarisation du SET

influence son diagramme de stabilite en changeant les pentes des cotes des motifs en carreaux

qui constituent le diagramme. II faut en general tenir compte du type de polarisation lors de la

modelisation de l'effet du champ electrique sur le courant tunnel, comme discute au chapitre 4.

De plus, le SET lui-meme peut etre symetrique (Rs = RD, CS = Co) ou non. Ce qui, jumele avec

les deux types de polarisation presentes precedemment, generera potentiellement plusieurs

caracteristiques courant-tension, parfois tres differentes selon chaque combinaison.

2.2 Revue de 1'etat de l'art

Cette section est une des plus importantes, car elle analyse les generations de SETs

presentes et passees et extrait de cette etude des criteres de conception qui auront un impact

direct sur les transistors fabriques dans cette these. La demarche a d'abord ete historique et a

permis de recenser la majeure partie des approches techniques utilisees par les meilleurs

procedes de fabrication. Cette etape a ete cruciale, car elle a identifie des lignes de pensee

quelque peu arbitraires qui ont influence les procedes de fabrication publies depuis les dix

dernieres annees. C'est en partie en questionnant ces dogmes que les directions du present

travail ont emerge. De ces lignes directrices sont nees, dans un deuxieme temps, les

loin. Le concept de SET developpe ici a egalement tenu compte de la disponibilite des

equipements et materiaux du laboratoire, ainsi que des contraintes de temps. Ces facteurs ayant

ete optimises pour maximiser les chances d'atteindre les objectifs fixes.

Comme mentionne precedemment, des les annees 50 et 60, on connaissait l'existence de

la conduction par saut dans les films granulaires. Evaporer de minces couches de metal etait

tout ce qui etait necessaire pour observer ces phenomenes a basse temperature. La nature creait

le reste en faisant litteralement croitre, durant le depot des films, des ilots de taille

microscopique agglomeres les uns contre les autres. On peut affirmer que les premiers travaux

etaient bases presque exclusivement sur des films metalliques. Un bouleversement majeur allait

cependant couper court a ces approches granulaires. II survint dans les annees 70, avec

P apparition de la lithographie, qui orienta du coup les chercheurs vers des structures

artificielles ou Ton pouvait faconner et positionner soi-meme des motifs de taille

micrometrique. Le raffinement de ces travaux coi'ncida avec l'epoque des predictions

theoriques qui sous-entendaient l'existence possible du SET et on attribua aussitot a la

lithographie la tache de fabriquer des SETs. II etait clair cependant que Ton devait disposer de

jonctions de quelques centaines de nanometres, resolution qui depassait largement les quelques

microns des meilleures machines disponibles a l'epoque. L'idee originale de P evaporation a

angle [Dolan, 1977] allait changer les choses, lorsqu'elle fut reprise pour demontrer le SET en

laboratoire [Fulton, 1987]. Avec cette methode, une couche metallique est evaporee au travers

d'un masque de resine de quelques microns de resolution, suspendu au-dessus de la surface du

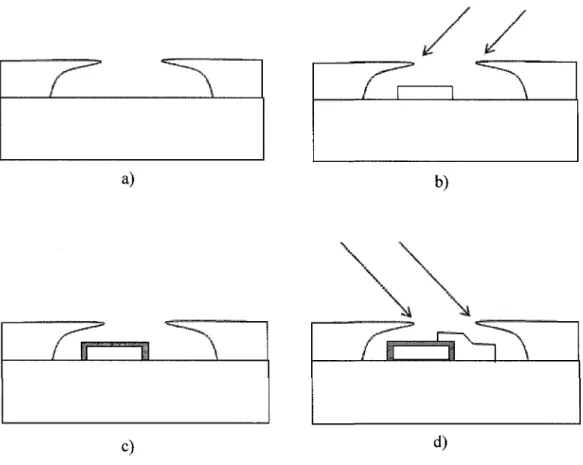

a) b)

c) d)

Figure 2.5 La methode d'evaporation a angle de Dolan.

puis, une deuxieme couche de metal est deposee avec un angle legerement different au travers

du meme masque suspendu. Cet angle deplace la projection de la deuxieme couche de metal de

quelques centaines de nanometres par rapport a la premiere couche oxydee. II y a done

superposition sur quelques centaines de nanometres de deux films metalliques separes par un

mince dielectrique, comme montre a la figure 2.5d. Les jonctions tunnel du SET sont formees

par cette superposition (overlap). Cette methode fut employee pendant de nombreuses annees

et a permis de valider plusieurs concepts theoriques de la mono-electronique. Jusqu'a cette

employe. Tous ces dispositifs etaient cryogeniques souventjusqu'a quelques millikelvins. Les

meilleurs SETs fabriques par la methode de Dolan ont pu atteindre 77 K et meme un peu plus.

L'evaporation a angle permettait un bon controle sur les parametres de la couche dielectrique

ainsi que sur 1'emplacement et le nombre de jonctions creees. Ce controle etait important, car

on s'efforcait de demontrer, a l'epoque, les principes des boites, pompes et registres

mono-electroniques (box, pump, turnstile) ainsi que les effets des jonctions multiples (multiple tunnel

junctions, MTJ) [pour des exemples de ces dispositifs, voir entre autres Lafarge et coll., 1991,

Kim et coll., 2003, Tsukagoshi et coll., 1998 et Nakazato et coll., 1995]. Pour effectuer ces

tests, il fallait fabriquer, de facon controlee, un certain nombre de jonctions. Une jonction dans

les cas de la boite, deux pour un SETs et une matrice lineaire de N jonctions dans le cas des

MTJs. Comme on croyait durant ces annees remplacer le FET par le SET, on fabriqua aussi un

grand nombre de portes logiques elementaires (AND, NAND, XOR, etc.). Etant donne qu'il

fallait bien controler la localisation des jonctions, on utilisait la plupart du temps Pevaporation

a angle et on demontrait le principe de fonctionnement des circuits avec des mesures prises a

des temperatures cryogeniques [voir par exemple Heij et coll., 2001].

La lithographie se raffinant, et avec l'apparition de la lithographie par faisceau

d'electrons, on a cru qu'il serait possible de proceder a une reduction d'echelle des SETs, un

peu comme on l'avait fait avec les FETs. Likharev publia cependant en 1999, une revue

complete des SETs [Likharev, 1999], dans laquelle il souligna que la lithographie ne pourrait

probablement jamais produire de SETs performants. L'une de ses courbes, dont les valeurs sont

reproduites au tableau 2.1, est devenue tres connue et employee dans plusieurs articles par la

cas generique avec un ilot spherique conducteur dont 10 % de la surface etait occupee par les

jonctions avec un coefficient dielectrique de 4. L'article avan9ait que pour remplacer un FET

par un SET, il faudrait Ec > 100kBT. Pour une operation a 300 K (Ec > 2600 meV), le tableau

2.1 montre que l'on doit viser une taille d'llot bien inferieure a 1 nm, ce qui en fait une cible

quasi impossible a atteindre en lithographic Dans le meme article, on presentait le travail de la

lithographie par microscope a effet tunnel {scanning tunneling microscope, STM), vu comme

l'outil de lithographie ultime. Les SETs metalliques fabriques par STM avaient de loin les

meilleures caracteristiques et fonctionnaient a 300 K. Par contre, on soulignait le fait que les

STMs ne sont que des outils de laboratoire tres lents et sans voie connue vers la fabrication en

volume. L'article de Likharev eut une influence importante avec deux repercussions notables.

D'abord, il montrait que la taille utile des SETs pourrait etre inferieure a 1 nm, ce qui suggerait

que la lithographie avait atteint ses limites. Ensuite, il envisageait que la seule facon d'obtenir

des SETs performants etait d'utiliser des objets de taille nanometrique reguliere, deja faconnes

par la nature comme des nanoparticules, des films granulaires, des grappes d'atomes

auto-alignes {self-aligned atom clusters) ou encore des boules de carbone {buckyballs).

Tableau 2.1 Apercu des valeurs de capacitance d'ilot selon Likharev

M

<• ( Cn|):K'it;iiHT de l"ilo1 \ )••'•• ( a K )100

10

1

2

60

700

80

3

0.2

* Ec = ez/(2C)Depuis les annees 50, les etudes mono-electroniques etaient executees sur des films

metalliques avec des dimensions ou Ec » E

Ket ou E

A~ E

c. Cependant, la densite d'etats plus

faible des semi-conducteurs augmente sensiblement E

K(comme vu a l'equation 2-4). L'usage

de semi-conducteurs constitue done un moyen d'augmenter EA sans reduction de taille, grace a

la contribution de ER. Le silicium est tout indique pour cette tache, puisqu'il est compatible

avec les equipements en place dans l'industrie. Les gaz bidimensionnels dans les

semi-conducteurs composes (ex.: GaAs, AlGaAs, etc.) sont aussi une possibility quoique moins

attrayante, pour la fabrication par l'industrie en place, majoritairement orientee en silicium.

L'article de Likharev faisait cependant une mise en garde a ce sujet: 1'utilisation de SETs en

silicium ou crees par nanoparticules amene une difflculte supplemental. Afin d'assurer la

conduction electrique des SETs fabriques en nanoparticules, en boules de carbone ou par

grappes d'atomes, il faut fabriquer des electrodes de contact pour lesquelles il sera impossible

de savoir le nombre de particules contactees. Les films granulaires ont egalement un probleme

de reproductibilite car on ne controle pas le nombre et la forme des tlots. Pour le silicium et les

SETs fabriques sur semi-conducteur, le confinement profond et la discretisation des niveaux

d'energie amenent des difficultes majeures dans l'analyse des resultats. La principale difficulte

provient du fait que le taux d'effet tunnel des porteurs n'est plus simplement lie au changement

d'energie E

c, comme vu precedemment. Toutes ces approches comportent done un caractere

imprevisible et non-repetable comparativement aux SETs metalliques qui sont beaucoup plus

reguliers et qui sont decrits quantitativement par la theorie orthodoxe. Leur conduction est

reguliere, notamment en ce qui a trait aux oscillations I

DS-

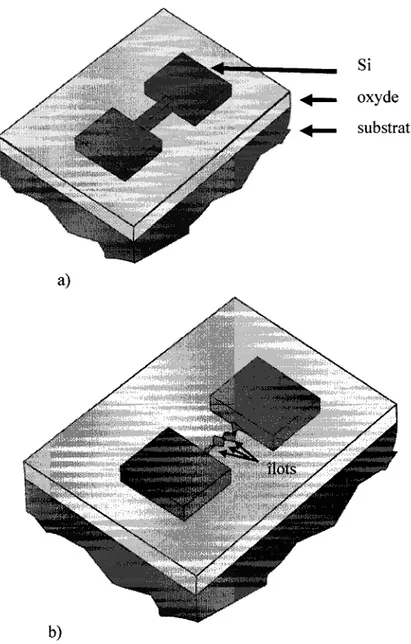

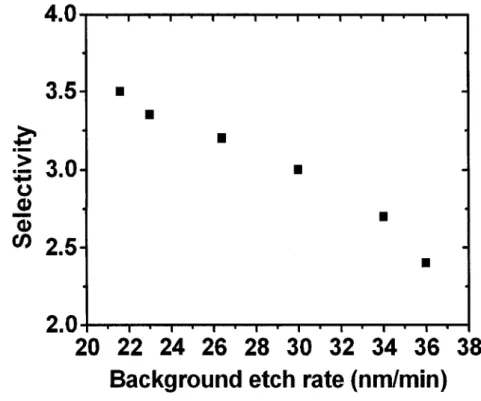

structures creees sur substrat de silicium sur isolant {silicon on insulator, SOI). Ces approches

comportent beaucoup d'etapes de fabrication. En utilisant un substrat SOI aminci pour obtenir

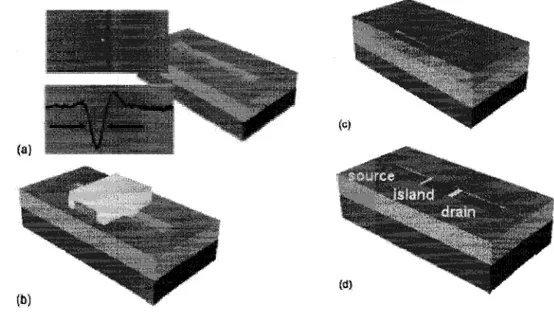

quelques dizaines de nanometres de silicium, on definit un motif etroit par lithographie par

faisceau d'electrons et gravure plasma {reactive ion etching, RIE) comme montre a la figure

2.6a. Ce fil est ensuite aminci encore une fois par une autre etape de gravure liquide et il est

oxyde dans une fournaise. II en resulte des oxydations locales, en etranglement du fil de

silicium, qui forment une chaine de petits llots (figure 2.6b). Le nombre d'ilots est inconnu, de

meme que Pepaisseur du dielectrique des jonctions. La forme des ilots n'est pas previsible,

mais leur taille est souvent estimee a moins de 5 nm. Ces dispositifs sont parfois fabriques a

partir de silicium de type p ce qui en fait des SHTs {single-hole transistor). Ces dispositifs ont

des gains superieurs a 1'unite et presentent des caracteristiques uniques, comme des resistances

differentielles negatives et des pics de conduction dans leur courbe IDS-VDS- Leur caractere est souvent imprevisible, mais ils auront toujours des pics d'oscillations dans leur courbe IDS-VGS et IDS-VDS- De nouveaux types de circuits ont ete proposes pour utiliser ces transistors, notamment en logique et en memoire statique [Saitho et coll., 2004]. A partir d'un certain

nombre d'hypotheses et d'approximations, on a estime, chez les bons dispositifs sur silicium,

une energie EA autour de 0.57 eV avec Ec = e2/2CT = 0.22 eV et EK= 0.35 eV [Miyaji et coll.,

2006]. La capacite Cj est done de 0.73 aF. Comme la plupart des precedes presenters dans la

litterature, les donnees au-dessus de 300 K ne sont pas disponibles pour les dispositifs au

silicium. Leur marge d'operation reste done a etablir, ce qui les place au meme stade

d'avancement que le reste de la technologie SETs.

Figure 2.6 La methode d'oxydation locale de fil de silicium.

Likharev dans son contexte (les valeurs du graphique sont montrees au tableau 2.1). Cet article

etait une revue generate des SETs et cette courbe etait utile pour fixer les ordres de grandeur

dont on peut parler en technologie mono-electronique. Les possibilites des dispositifs sont trop

nombreuses et trop complexes pour rapporter tous les cas a une sphere conductrice et a ses

dimensions souhaitables. Base sur ces hypotheses, on ne peut done pas affirmer que la

lithographie est sans avenir. La lithographie amene un controle et une reproductibilite

necessaire a une potentielle commercialisation. Que dire ensuite des estimations sur ce que doit

etre la valeur de EA dans P equation 2-6? Dans l'expression EA » xkBT, la litterature publie des

valeurs de x qui varient sur plusieurs ordres de grandeur [voir par exemple Saitho et coll., 2002

ou Nakazato et coll., 1994]. Ce calcul est pourtant primordial, car la valeur de x fixe une

contrainte importante sur la taille de l'Tlot. Beaucoup d'articles de la litterature [voir par

exemple Takahashi et coll., 2002] affirment par exemple que puisque x doit supposement se

situer au minimum autour de 10, et si T = 300 K, alors la taille de Pilot a partir du graphique de

Likharev doit etre necessairement inferieure a 2 nm. Pour x = 100, la taille de Pilot devrait etre

inferieure a 1 nm. En se fiant a ce resultat, les SETs n'ont done peu ou pas d'avenir, car tres

peu de technologies peuvent arriver a ces dimensions. Heureusement, la justification pour

x = 10 ou x = 100 n'a pas encore ete demontree avec des dispositifs et des circuits utiles. En

fait, il n'y a probablement pas de reponse unique a la valeur de x, car elle depend de

Papplication visee par les SETs. Les fluctuations thermiques ont des consequences desastreuses

sur les SETs, car elles peuvent, entre autres, donner Penergie suffisante a un electron de Pilot

pour surmonter la barriere d'energie des jonctions de facon aleatoire. Ce comportement mene a

des consequences bien differentes dependamment de Papplication. II peut par exemple prendre

la forme de courant de fuite statique dans une application logique alors qu'il engendrera un

taux d'erreur de bit (bit error rate, BER) dans un circuit de memoire. Dans ce cas precis par

exemple, le BER montre un comportement exponentiel avec EA. Si on veut remplacer une

technologie FET qui offre un bit d'erreur a tous les trois ans, il faudra une valeur de x d'au

marge de securite qui doit completement eliminer la queue de la courbe gaussienne de

distribution energetique des electrons de Pilot. La conclusion sur la valeur de x est qu'il ne faut

pas abandonner le developpement des SETs en supposant une valeur de x. II faut d'abord

fabriquer des SETs avec assez de marge d'operation pour batir un nombre suffisant de circuits

et d'applications sur lesquelles on mesurera et etablira des specifications precises pour x.

Enfin, le dernier point de la revue de Petat de l'art des SETs concerne le choix de la

plateforme: metallique ou semi-conducteur. Bien qu'une theorie orthodoxe etendue existe

[Averin et coll., 1991a] pour tenir compte de la separation des niveaux d'energie, il n'en

demeure pas moins que la vaste majorite des simulateurs numeriques et des macro-modeles

(ex.: modeles SPICE) fonctionnent pour des dispositifs qui peuvent etre decrits par la simple

theorie orthodoxe. Ce point rejoint une des conclusions de la revue de Likharev ou celui-ci

soulignait Pimportance de developper des SETs qui fonctionnent dans le regime Ec > EK, ce

qui est le cas pour la vaste majorite des SETs metalliques. II faut se rappeler que la capacite

d'utiliser les macro-modeles pour developper les nouvelles architectures hybrides SET/FET est

un atout majeur.

2.3 Cahier des charges

A la lumiere de la revue de la section precedente, des choix techniques ont ete faits pour

guider le travail de cette these. Tout d'abord, la plateforme sera metallique. Cependant, les

methodes de fabrication retenues devront pouvoir s'appliquer egalement aux semi-conducteurs.

beaucoup mieux supported en ce qui a trait aux outils de design et de modelisation de circuits,

ce qui est un atout considerable vers la route de la commercialisation. Le deuxieme choix

technologique sera l'utilisation de la lithographie par faisceau d'electrons {electron beam

lithography, EBL). Cette technologie mature a fait ses preuves et est compatible avec

l'industrie, si on en limite 1'usage aux sections critiques du dispositif, ceci a cause de la relative

lenteur de la technique. Elle permettra egalement de fournir un controle sur le nombre et la

localisation des jonctions. Une approche auto-alignee reduira les risques d'erreur du procede.

Le troisieme choix concerne le dielectrique. II devra etre obtenu thermiquement afin d'en

optimiser la qualite et le controle sur l'epaisseur. Quatriemement, le choix de la grille. Cette

derniere pourra etre une grille arriere {back-gate) pour demontrer le concept, mais la these

devra proposer une option pour obtenir des grilles de surface. Cinquiemement, il importe a ce

stade de fixer un ordre de grandeur pour les valeurs de capacite a atteindre. Comme mentionne

precedemment, les meilleurs SETs metalliques ont ete realises par lithographie STM pour des

capacitances totales de l'ordre de 0.70 aF [Matsumoto et coll., 1996]. Cette gamme de valeurs

de CT sera done l'objectif a atteindre. Notons cependant que ces SETs ne sont pas des

dispositifs utiles, car l'epaisseur de leur barriere dielectrique est trop importante. En effet,

celle-ci depend de la resolution laterale du STM, qui se situe entre 15 nm et 25 nm. Les probabilites

d'effet tunnel sont tres faibles a ces fortes epaisseurs. Le courant de drain des SETs avec les

meilleures capacitances se situe alors dans les centaines de femto amperes. Des courants

jusqu'a trois ordres de grandeur plus Aleves seraient souhaitables afin de charger les

capacitances des interconnections qui contactent les differents SETs d'un circuit pratique.

Puisque chaque deviation d'une etape de procede risque d'augmenter CT, un effort devra

Les paragraphes precedents, comme la vaste majorite de la litterature sur les SETs, ont

porte un grand soin a preciser les dimensions maximales des transistors. Mais qu'en est-il de la

taille minimale des SETs? Cette question peut paraitre insolite apres avoir tant parle de la haute

resolution requise pour un fonctionnement au-dessus de 300 K. La litterature sur ce sujet est

pratiquement inexistante [pour un article effleurant la question voir Lutwyche et coll., 1994].

Pourtant, il ne faut pas oublier que la tension de seuil du blocage de Coulomb, qui determine

l'etat ouvert (on state) de l'etat ferme (offstate), decoule, chez le SET, de l'energie de charge et

done de la taille du transistor. Tout dependant comment le SET est utilise dans un circuit, cette

tension de seuil peut devenir un facteur critique. La valeur des resistances de jonction, guidee

par l'equation 2-5, doit etre garantie dans toute la plage des voltages jusqu'a la tension de seuil.

Si celle-ci est trop elevee du a un SET trop petit, un regime de fort champ electrique sera

atteint, bien avant le point de tension de seuil. Or, a fort champ electrique, la conduction par

mecanisme de Fowler-Nordheim peut dominer et resulter en une diminution de la resistance

des jonctions qui dissipera immediatement le blocage de Coulomb et annulera l'effet transistor.

Les dimensions du SET sont done un compromis entre la tension de seuil resultante et les

caracteristiques des barrieres de potentiel des jonctions. Cette notion d'ingenierie des jonctions

est une contribution importante amenee par cette these et permet de mieux comprendre les

mecanismes de conduction du SET, comme montre au chapitre 4. Les caracteristiques des

jonctions, comme la hauteur de leur barriere d'energie et leur epaisseur, represented la

premiere limite a la taille minimale des SETs. La deuxieme limite concerne l'ordre de grandeur

des tensions de seuil a cibler. Si le SET est de tres faibles dimensions, la tension de seuil sera

electroniques est en constante diminution depuis 30 ans afin de conserver des champs

electriques constants a mesure que l'on diminue les dimensions des designs. Ceci diminue les

fuites de courant et done, les pertes d'energie. On imagine mal faire le maillage d'un circuit

hybride SET/FET avec des tensions de seuil de FETs plus d'un ordre de grandeur inferieur a

celles des SETs. Cette discussion apporte done les deux derniers criteres du cahier des charges.

La tension de seuil VTH des SETs sera definie comme la tension du blocage de Coulomb

( VTH= ellCj) et devra etre compatible avec l'ordre de grandeur des tensions de seuil des FETs

du ITRS roadmap. Selon la version 2006 du roadmap [ITRS, 2006], les VTH sont

approximativement de 170 mV. On prendra pour acquis qu'aucune combinaison de tension

inferieure a VW2 ne pourra placer le SET en mode de conduction et qu'aucune valeur

superieure a 2VTH ne pourra le basculer en mode ferme ou en mode Fowler-Nordheim.

La cible a atteindre pour une barriere d'energie adequate (hauteur de barriere Oo) des

jonctions n'est a peu pres pas discutee dans la litterature. Pourtant, il ne faut pas negliger son

role dans la conception du SET d'ou, encore une fois, 1'importance du concept d'ingenierie des

jonctions. Le potentiel Oo/e devra etre suffisamment eleve pour garantir les valeurs de RT sur

toutes les plages de tensions pratiques du SET (specification de Oo minimal). La resistance des

jonctions fluctuera si la tension d'operation du SET devient beaucoup plus grande que Oo/e.

Toutefois, comme le courant d'effet tunnel diminue avec l'accroissement de Oo, il sera

egalement important de garantir une valeur maximale de barriere d'energie pour conserver des

ordres de grandeur utiles de courant IDs. Afin de garantir le fonctionnement du dispositif

autour de sa valeur de VTH, la cible de Oo sera pour cette raison etablie a eVm < Oo <

Tableau 2.2 Resume du cahier des charges.

Ciiii'ivs ( luiix

Plateforme

Metallique

Creation de la structure

Lithographie par faisceau d'electrons.

Structure auto-alignee.

Dielectrique de jonction

Epaisseur controlee par oxydation thermique

Type de grille

Grille arriere (back-gate) avec option sur grille de

surface

Capacite totale pour marge d'operation CT < 0.70 aF

Courant de drain

IDS> lpA

Tension de seuil VTH

VTH = g/2Cx (le plus pres possible du ITRS roadmap)

Potentiel de barriere On/e

VTH < O0/e < 2VTH2.4 Choix du concept

La methode de P evaporation a angle a ete la plus utilisee jusqu'a maintenant et a

montre des resultats remarquables et une grande simplicite. Cependant, cette methode en est

une capable d'atteindre le regime des capacitances totales de l'ordre de Pattofarad. Comme un

des objectifs de cette these est de degager une marge de manoeuvre pour les SETs, il sera

necessaire dans ce cas de developper une methode capable d'atteindre le regime sous-attofarad

(subattofarad). Degager une marge de manoeuvre en pouvant operer au-dessus de 300 K est un

defi important auquel il faudra appliquer un concept de fabrication radicalement innovateur,

tout en garantissant une certaine robustesse.

Le concept retenu vise a exercer un controle tridimensionnel sur le SET. Jusqu'a

present, les approches bidimensionnelles ont mis beaucoup de pression sur la lithographie qui

devait controler, a elle seule, toutes les dimensions critiques du dispositif. En apportant un

controle tridimensionnel, on relaxera les contraintes en lithographie, ce qui aura pour effet de

rendre les technologies de lithographie actuelles utilisables pour les dispositifs

mono-electroniques de pointe. L'evaporation a angle permet difficilement de controler le

chevauchement des deux couches qui forment pourtant l'essentiel de la capacite de jonction.

Un controle tridimensionnel permettrait de supprimer ce chevauchement et d'obtenir des

jonctions purement planaires. II en resulterait une diminution significative de la capacitance

totale du SET et une elevation proportionnelle de la temperature d'operation.

Tableau 2.3 Resume du concept de SET retenu.

MiTi-N

Idee directrice

( l n i i \

Utilisation d'un precede qui depose une couche

metallique, suivi de l'oxydation de celle-ci, puis du

depot d'une autre couche metallique. Le precede cree un

chevauchement qui sera par la suite elimine, creant ainsi

des jonctions planaires de tres faible capacitance.

Atout majeur

En controlant la troisieme dimension (epaisseur) de

l'espace, il est possible de relaxer les criteres de

resolution dans les deux autres dimensions. Ceci permet

d'etendre la duree de vie utile de la lithographie dans les

precedes SET.

2.5 Choix technologiques

La lithographie se definit en general selon les axes x et y qui represented

respectivement la longueur et la largeur des motifs sur le substrat. L'axe vertical des z sert

surtout a mesurer les elements affectant la troisieme dimension des substrats, comme

Pepaisseur des depots de couches minces ou la profondeur des gravures plasma. Le controle

a) b) c)

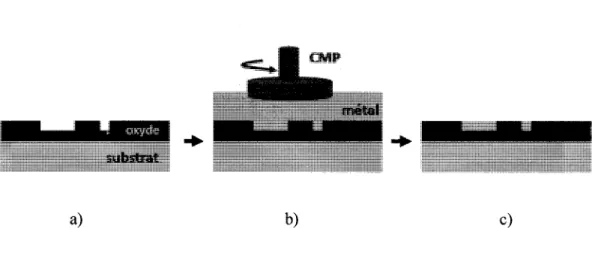

Figure 2.7 La methode de CMP communement appelee damascene.

reduire les variations topographiques des circuits en technologie FET. Ces techniques reposent

principalement sur le polissage physico-chimique {chemical mechanical polishing, CMP) de

differentes couches, qu'elles soient metalliques, semi-conductrices ou dielectriques. Ces

methodes constituent un bon choix pour le present travail. Elles sont relativement matures

[Perry, 1998], bien documentees et compatibles avec la production a haut volume. II s'agirait,

dans ce cas bien precis, de CMP metallique pour respecter la plateforme choisie du cahier des

charges. Ce type de polissage se fait habituellement avec une matrice d'oxyde sur laquelle

s'appuie mecaniquement le polissage. Une tranchee est fabriquee dans la couche d'oxyde de

silicium (figure 2.7a), puis un depot metallique y est depose de facon a recouvrir l'ensemble du

substrat, y compris la tranchee. Le substrat est ensuite pose contre une table rotative (figure

2.7b) sur laquelle est colle un tapis (polishing pad). Une pate de particules en suspension

(slurry) est repandue sur le tapis et agit comme agent abrasif pour amincir l'echantillon jusqu'a

la couche d'oxyde. Le depot metallique est entierement retire, sauf dans la tranchee qui

![Figure 2.2 a) Exemple de courbe de reference IDS-VDS en blocage de Coulomb a temperature T] b) la meme courbe avec 0.5e charge induite sur Pilot par l'effet de la grille et c) la courbe de reference a temperature T 2 » TV d) Exemple de courbe de refer](https://thumb-eu.123doks.com/thumbv2/123doknet/3313826.95445/27.921.211.766.196.639/exemple-reference-coulomb-temperature-induite-reference-temperature-exemple.webp)