Multimodal Implantable Neural Interfacing Microsystem

Thèse

Masoud Rezaei

Doctorat en génie électrique

Philosophiæ doctor (Ph. D.)

Résumé

Afin d’étudier le cerveau humain dans le but d’aider les patients souffrant de maladies neurologiques, on a besoin d’une interface cérébrale entièrement implantable pour permettre l’accès direct aux neu-rones et enregistrer et analyser l’activité neuronale. Dans cette thèse, des interfaces cerveau-machine implantables (IMC) à très faible puissance basées sur plusieurs circuits et innovations de systèmes ont été étudiées pour être utilisées comme analyseur neuronal. Un tel système est destiné à recueillir l’activité neuronale émise par centaines de neurones tout en les activant à la demande en utilisant des moyens d’actionnement tels que l’électro- et / ou la photo-stimulation. Un tel système doit fournir plusieurs canaux d’enregistrement, tout en consommant très peu d’énergie, et présente une taille extrêmement réduite pour la sécurité et la biocompatibilité. Typiquement, un microsystème d’interfaçage avec le cerveau comprend plusieurs blocs, tels qu’un bloc analogique d’acquisition (AFE), un convertisseur analogique-numérique (ADC), des modules de traitement de signal numé-rique et un émetteur-récepteur de données sans fil. Un IMC extrait les signaux neuronaux du bruit, les numérise et les transmet à une station de base sans interférer avec le comportement naturel du sujet. Cette thèse se concentre sur les blocs analogiques d’acquisition à très faible consommation à utiliser dans l’IMC. Cette thèse présente des frontaux avec plusieurs stratégies innovantes pour consommer moins d’énergie tout en permettant des données de haute résolution et de haute qualité.

Premièrement, nous présentons une nouvelle structure frontale utilisant un schéma de réutilisation du courant. Cette structure est extensible à un très grand nombre de canaux d’enregistrement, grâce à sa petite taille de silicium et à sa faible consommation d’énergie. L’AFE à réutilisation de courant proposée, qui comprend un amplificateur à faible bruit (LNA) et un amplificateur à gain programmable (PGA), utilise une nouvelle topologie de miroir de courant entièrement différentielle utilisant moins de transistors et améliorant plusieurs paramètres de conception, tels que la consommation d’énergie et du bruit, par rapport aux mises en œuvre de circuit d’amplificateur de réutilisation de courant précédentes.

Ensuite, dans la deuxième partie de cette thèse, nous proposons un nouveau convertisseur sigma-delta multicanal qui convertit plusieurs canaux indépendamment en utilisant un seul amplificateur et plusieurs condensateurs de stockage de charge. Par rapport aux techniques conventionnelles, cette méthode applique un nouveau schéma de multiplexage entrelacé, qui ne nécessite aucune phase de réinitialisation pour l’intégrateur lors du passage à un nouveau canal, ce qui améliore sa résolution.

Lorsque la taille des puces n’est pas une priorité, d’autres approches peuvent être plus attrayantes, et nous proposons une nouvelle stratégie d’économie d’énergie basée sur un nouveau convertisseur sigma-delta à très basse consommation conçu pour réduire la consommation d’énergie. Ce nouveau convertisseur utilise une architecture basse tension basée sur une topologie prédictive innovante qui minimise la non-linéarité associée à l’alimentation basse tension.

Abstract

Studying brain functionality to help patients suffering from neurological diseases needs fully im-plantable brain interface to enable access to neural activities as well as read and analyze them. In this thesis, ultra-low power implantable brain-machine-interfaces (BMIs) that are based on several inno-vations on circuits and systems are studied for use in neural recording applications. Such a system is intended to collect information on neural activity emitted by several hundreds of neurons, while acti-vating them on demand using actuating means like electro- and/or photo-stimulation. Such a system must provide several recording channels, while consuming very low energy, and have an extremely small size for safety and biocompatibility. Typically, a brain interfacing microsystem includes several building blocks, such as an analog front-end (AFE), an analog-to-digital converter (ADC), digital sig-nal processing modules, and a wireless data transceiver. A BMI extracts neural sigsig-nals from noise, digitizes them, and transmits them to a base station without interfering with the natural behavior of the subject. This thesis focuses on ultra-low power front-ends to be utilized in a BMI, and presents front-ends with several innovative strategies to consume less power, while enabling high-resolution and high-quality of data.

First, we present a new front-end structure using a current-reuse scheme. This structure is scalable to huge numbers of recording channels, owing to its small implementation silicon area and its low power consumption. The proposed current-reuse AFE, which includes a low-noise amplifier (LNA) and a programmable gain amplifier (PGA), employs a new fully differential current-mirror topology using fewer transistors. This is an improvement over several design parameters, in terms of power consumption and noise, over previous current-reuse amplifier circuit implementations.

In the second part of this thesis, we propose a new multi-channel sigma-delta converter that converts several channels independently using a single op-amp and several charge storage capacitors. Com-pared to conventional techniques, this method applies a new interleaved multiplexing scheme, which does not need any reset phase for the integrator while it switches to a new channel; this enhances its resolution.

When the chip area is not a priority, other approaches can be more attractive, and we propose a new power-efficient strategy based on a new in-channel ultra-low power sigma-delta converter designed to decrease further power consumption. This new converter uses a low-voltage architecture based on an innovative feed-forward topology that minimizes the nonlinearity associated with low-voltage supply.

Table des matières

Résumé iii

Table des matières vi

Liste des tableaux viii

Liste des figures ix

List of Symbols xii

Introduction 1

1.1 Presentation of the project . . . 2

1.2 Literature Review : Low-noise Amplifier Design . . . 3

1.3 Literature Review : Filter Stage and Second-gain Stage . . . 7

1.4 Literature Review : Analog to Digital Converters . . . 8

1.4.1 Successive Approximation Register ADC (SAR) . . . 10

1.4.2 Sigma Delta Converter . . . 11

1.5 Literature Review : Optimizing Brain Machine Interface . . . 13

1.6 Thesis Outline and Summary of the Contributions . . . 14

2 A Low-Power Current-Reuse Analog Front-End for High-Density Neural Recor-ding Implants 16 Résumé . . . 16

Abstract . . . 17

2.1 Introduction . . . 17

2.2 CURRENT REUSE ANALOG FRONT END OVERVIEW . . . 18

2.2.1 Principle of Current-Reuse Amplifier . . . 19

2.2.2 Noise Analysis . . . 20

2.2.3 Proposed Current-Reuse Amplifier Design . . . 21

2.2.4 Current-Reuse AFE Design . . . 22

2.2.5 Parasitic Input Capacitors Analysis . . . 24

2.2.6 Implementation of Current-Reuse PGA . . . 26

2.2.7 Noise and Power Efficiency Factors Analysis . . . 27

2.3 Measurement Results . . . 29

2.3.1 Measured Performances . . . 29

2.3.2 In-Vivo Recording Results . . . 31

3 A TDM-Σ∆ Converter with Time-Interleaved Oversampling for High-Density Neu-ral Implants 34 Résumé . . . 34 Abstract . . . 35 3.1 Introduction . . . 35 3.2 System Overview . . . 37 3.2.1 Conventional TDM Σ∆ Converter . . . 37

3.2.2 Time-Interleaved Oversampling TDM Σ∆ Converter . . . 39

3.3 Time-Interleaved Oversampling Σ∆ System Design . . . 40

3.3.1 Switched-Capacitor Op-amp Sharing . . . 41

3.3.2 Dynamic Comparator and Switches . . . 42

3.3.3 Clock Sequence Generator . . . 42

3.4 Measurement Results . . . 43

4 A 110-nW in-Channel Sigma-Delta Converter for Large-Scale Neural Recording Implants 46 Résumé . . . 46

Abstract . . . 46

4.1 Introduction . . . 47

4.2 Circuit Design. . . 50

4.3 Simulation and Implementation Results . . . 52

4.4 Conclusion . . . 54

Conclusion 56

Publication List 58

Liste des tableaux

2.1 Summarized performance of the LNA and comparison . . . 32

4.1 Summary of performance of the proposed circuit against technology corners. . . 54

Liste des figures

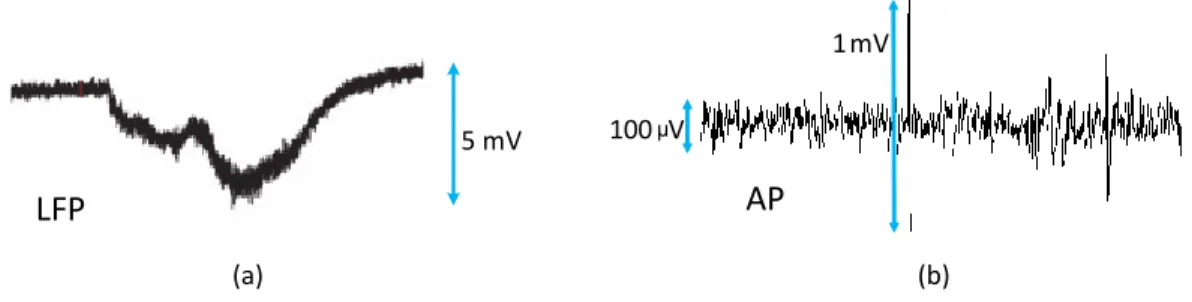

1.1 Two different types of neural signals. a) Local field potential neural signals. b) Action

potential neural signals. . . 1

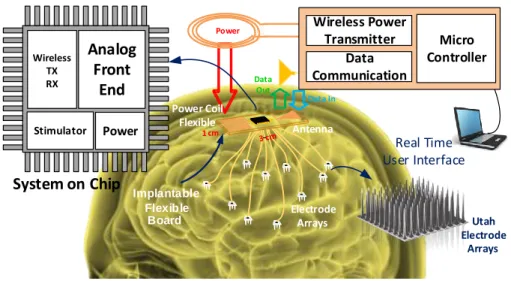

1.2 An implantable brain computer interface. . . 2

1.3 Block diagram of the conventional AFE. . . 3

1.4 Neural amplifier structure. . . 4

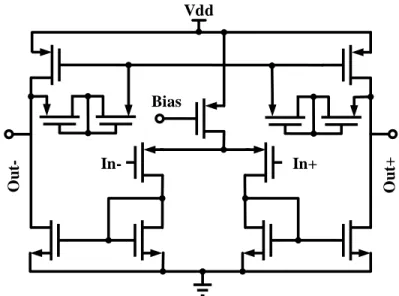

1.5 Current mirror low noise OTA. . . 4

1.6 Telescopic cascode low noise OTA.. . . 5

1.7 Folded cascode low noise OTA . . . 6

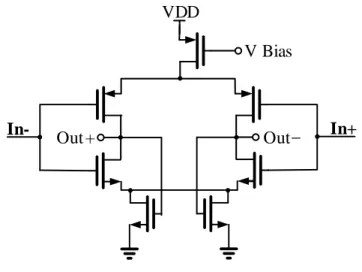

1.8 Complementary differential low noise OTA. . . 6

1.9 The partial OTA sharing. . . 7

1.10 High pass filter using programmable pseudo resistors. . . 8

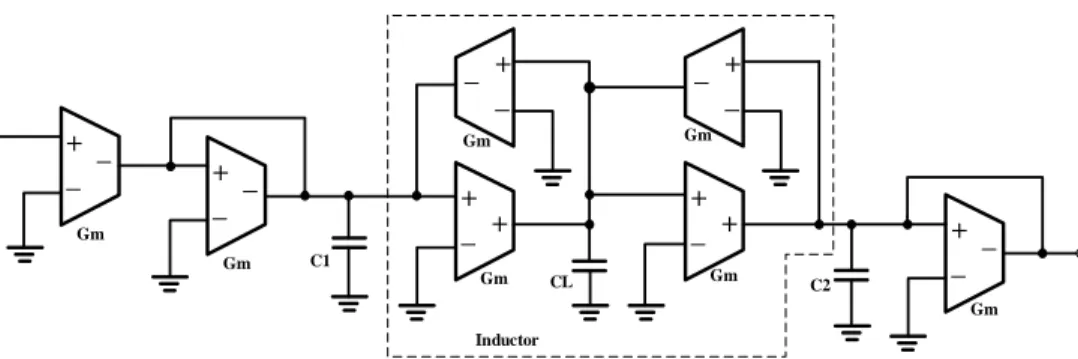

1.11 A 3rd order GM-C low-pass filter using LC structure . . . 9

1.12 A simple description to ADC functionality . . . 9

1.13 Comparison to the discrete voltage levels . . . 10

1.14 Successive approximation ADC . . . 10

1.15 Comparison between linear ADC and logarithmic ADC [1] . . . 11

1.16 Block diagram of a first order sigma-delta converter . . . 11

1.17 The modified model of the first order sigma-delta converter containing quantization noise. . . 12

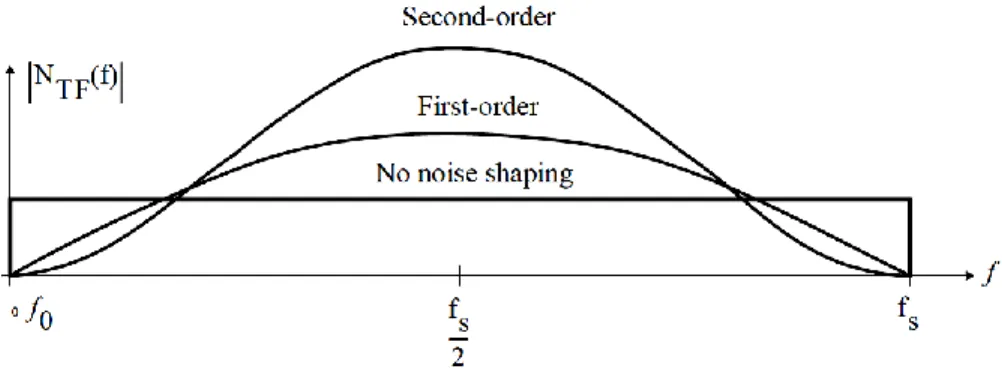

1.18 The noise shaping benefit of using a sigma-delta converter. . . 13

1.19 The parasitic input capacitor effect removal . . . 14

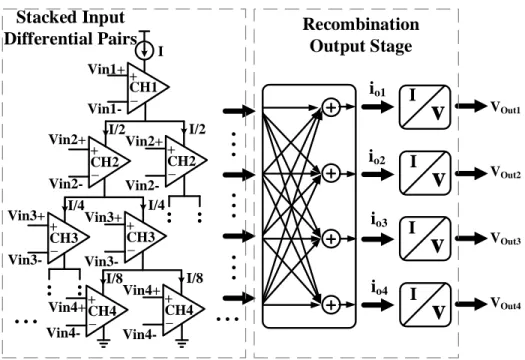

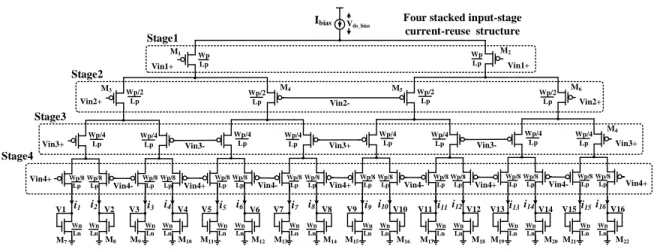

2.1 Conceptual representation of a four-channel stacked current-reuse amplifier. The input differential pairs share the same supply currents and the recombination and output blocks provide an output signal that is related to each corresponding input. . . 19

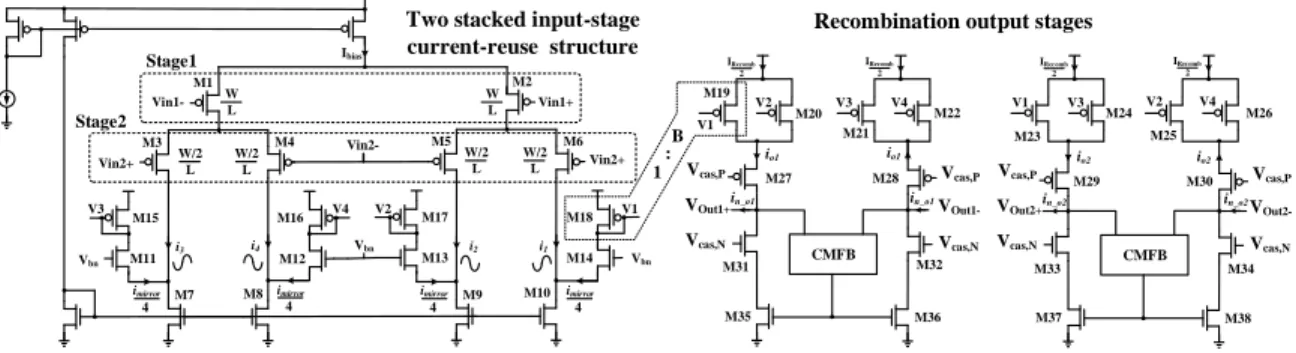

2.2 A conventional two-stage folded-cascode current reused amplifier. Two stacked input differential pairs share a same bias current source and each recombination output stage consumes B times the Ibias where B should be made smaller than 1. The common mode feedback circuits are also depicted. . . 20

2.3 The proposed optimized current reused amplifier circuit. A two-stage current mirror-based current-reuse amplifier topology uses less transistors than previous topologies. The current mirrors at the input of the recombination output stages scale the output current of the stacked input pairs by a factor of B. . . 22

2.4 Schematic of the implemented four stacked-input stage using the proposed optimized current reused amplifier circuit. In this design, Wp= 1000 µm, Lp= 0.8 µm, Wn= 80 µ m, Ln= 4 µm, Ibias= 2.5 µA. . . 22

2.5 The recombination output stage for one of the outputs related to the four-stacked input LNA (Fig. 2.4). In this design, Wp= 80 µm, Lp= 4 µm, Wn= 80 µm, Ln= 4 µm,

L= 1 µm, B = 1/8. . . 23

2.6 The noise simulation of the proposed LNA. . . 24

2.7 Block diagram of the proposed analog front-end, which includes four stacked current-reuse low-noise amplifiers (LNA) and programmable gain amplifiers (PGA). The ana-log multiplexer and outputs anaana-log buffers are also shown. . . 25

2.8 a) The proposed LNA design with the implemented T-network. b) The equivalent cir-cuit. The parasitic capacitor from input transistors are shown as CP.. . . 26

2.9 The minimum NEF versus the number of stacked differential inputs for different B factors. With B= 1/8 and N=4, this design achieves a theorical NEF of 1.237. . . 27

2.10 Die photograph of the 4-channel analog front-end fabricated in a TSMC CMOS 180-nm process. . . 28

2.11 Frequency responses (gain and phase) of the AFE for the 4 channels. . . 29

2.12 The different measured gain values for one channel in the AFE.. . . 30

2.13 Measured AFE input referred noise when the input of the AFE is shorted. . . 31

2.14 The in-vivo test setup is performed at the (CRIUSQ) on an anesthetized 23 g mouse. 32 2.15 (a) Recorded neural activity of each AFE channel from the hippocampus of a mouse. (b) 135 similar action potentials isolated from the recorded waveform and aligned (waveforms are referred to the amplifier input). . . 33

3.1 (a) Block diagram of a four-channel first order incremental Σ∆ converter (IΣ∆), where Nch is the number of multiplexed input channels and FNyq is the Nyquist sampling frequency. (b) Block diagram of the proposed four-channel multiplexed Σ∆ converter with Interleaved Oversampling (MIOΣ∆), where tsis the oversampling interval. . . . 36

3.2 Timing diagram of the output data stream and output spectrum of one channel with oversampling in of the IΣ∆ (a) and in the MIOΣ∆ (b), respectively. . . 37

3.3 Comparison between two TDM Σ∆ schemes. Performance comparison of the propo-sed TDM Σ∆ scheme with interleaved oversampling intervals depicted in Fig. 3.1-b (solid), and the conventional IΣ∆ scheme presented in Fig. 3.1-a (dashed), for a 100 Hz input sine wave for a bandwidth of 10 kHz and an OSR of 50. Both schemes are tested for second-order Σ∆ topologies. The conventional IΣ∆ scheme generates several harmonics within the bandwidth of interest, while the proposed scheme does not. The proposed scheme provides a 33 dB SNDR improvement compared to the conventional scheme, respectively. . . 38

3.4 (a) Schematic of the proposed multiplexing interleaved oversampling Σ∆ converter in the evaluation phase. Each input has its own integration capacitor. (b) The proposed circuit in the reset phase performed before each evaluation phase, and (c) the imple-mented switch circuit. . . 39

3.5 Schematic of the clock sequence generator and associated timing diagram. . . 40

3.6 Die photograph of the proposed multiplexing interleaved oversampling Σ∆ converter along with its clock sequence generator circuit. The circuit occupies a silicon area of 150 µm × 135 µm. . . 41

3.7 Measured PSD from input Channel 2 and measured inter-channel crosstalk. Channels 1 and 2 are given input sine waves of 1 kHz and 2 kHz, respectively. . . 42

3.8 Synthetic neural signal digitized with the fabricated Σ∆ converter after offline decima-tion in MATLAB. . . 43

4.1 An implantable brain computer interface. . . 47

4.2 Block diagram of the first order sigma-delta converter. . . 48

4.3 The error signal at the input of the comparator. a) Sigma-delta converter. b)

Feed-forward sigma-delta converter. . . 49

4.4 The power spectral density of the output signal. a) Sigma-delta converter. b)

Feed-forward sigma-delta converter. . . 49

4.5 Proposed circuit implementation of the sigma-delta converter depicted in Fig. 4.2. . . 50

4.6 (a) Implementation of the subtractor and integrator. (b) Implementation of switches

with dummy transistors for minimizing charge injection. . . 50

4.7 Schematic of the proposed multi-input comparator circuit. . . 51

4.8 Die photograph of the proposed sigma delta converter. . . 51

4.9 (a) Output power spectrum density obtained from a transient post layout simulation for an input sine wave. (b) Post-layout transient simulation for a pre-recorded in-vivo

List of Symbols

4KT Temperature coefitient in Kelvin

AP Action Potentials

ADC Analog to digital converter

AFE Analog front end

BMI Brain machine interface

BW Bandwidth

C Capacitor

CI Integrating capacitor

CMFB Common mode feedback

CMOS Complementary metal oxide semiconductor Cox Gate oxide capacitor

CS Sampling capacitor

DAC Digital to analog converter

dB Decibel

DC Direct current

DFF D flip flop

E Error signal

ENOB Effective number of bits

f Frequency

f J Femtojoule

f F Femto farad

FOM Figure of merrit

f w Feed-forward signal

gm Transconductance

Hz Hertz

I Current

Ibias Bias current

ICRR Inter-channel rejection ratio

Id Drain current

IΣ∆ Incremental sigma delta

kHz Kilo hertz

L Length

LFP Local Field Potentials LNA Low noise amplifier

MOSFET Metal oxide semiconductor field effect transistor

mm Milli meter

mV Milli volt

mW Milli watt

N Noise signal

NEF Noise efficiency factor

NMOS N type metal oxide semiconductor transistor

nV Nano volt

nW Nano watt

OSR Over sampling ratio

OTA Operational transconductance amplifier PEF Power efficiency factor

pF Pico farad

PGA Programmable gain amplifier

PMOS P type metal oxide semiconductor transistor PW M Pulse width modulation

R Resistor

RMS Root mean square

SAH Sample and hold

SAR Successive approximation register

SC Switched capacitor

SFDR Spurious free dynamic range SNR Signal to noise ratio

SNDR Signal to noise and distortion ratio T DM Time domain multiplexing

T HD Total harmonic distortion

T SMC Taiwan semiconductor manufacturing company UT Thermal voltage equal to 25 mV

V Voltage

Vi Voltage of node i

Vd Drain voltage

VDD Supply voltage

Vgs Gate-source voltage

Vout Output voltage

V GA Variable gain amplifier W Width X Input signal Y Output signal z variable in z domain µ Mobility µ m Micro meter µV Micro volt Σ∆ Sigma Delta °C Degree centigrade

Remerciements

First and foremost, I would like to thank Professor Benoit Gosselin for guiding my research, allowing me to discover several topics, and providing me the resources to carry it out. He encouraged me to perform to the best of my abilities and gave me opportunities to learn different topics. I would also like to thank Professor Mohamad Sawan for his advice and great support. I had this opportunity to work under his supervision and take advantage of his knowledge in my project. I would also like to thank my team member, Esmaeel Maghsoudloo for his cooperation, help and support through the research. Finally, I am deeply grateful to my wife and my family for their endless encouragement. This work could not have been accomplished without their dedicated support, trust and love throughout my life.

Avant-propos

Three chapters of this thesis are composed of material that is already published or under review in technical Transactions journal papers and a conference article. In the thesis, the text and figures have been modified to be consistent with the remainder of the document. The introduction sections have been most heavily modified. Here, I detail my contributions to two Transactions papers and the confe-rence article.

Paper 1 : M. Rezaei, E. Maghsoudloo, C. Bories, Y. De Koninck, B. Gosselin, "A Low-Power Current-Reuse Analog Front-End for High-Density Neural Recording Implants," IEEE Transactions on Bio-medical Circuits and Systems, vol. 12, no. 2, pp. 271-280, April 2018. This Transactions paper pro-vides mathematical analysis on noise calculation and introduces a novel current reuse structure AFE configuration that features smaller power consumption and less noise contribution. The original idea is proposed by me, and the experiments were conducted at the Biomedical Microsystem Lab at Laval University and research center CERVO. The manuscript was prepared by me and revised by the other authors before submission.

Paper 2 : M. Rezaei, E. Maghsoudloo, M. Sawan, B. Gosselin, "A Multiplexed Sigma-Delta Converter with Ultra Low- Crosstalk for High-Density Neural Implants," IEEE Transactions on Sensors (sub-mitted). This Transactions paper reviews the problems in the conventional multiplexing method in sigma-delta converters ; I have proposed another multiplexing scheme to improve the performance of the converter. The original idea was proposed by me, and the experiments were conducted at the Bio-medical Microsystem La at Laval University. The manuscript was prepared by me and revised by the other authors before submission.

Paper 3 : M. Rezaei, E. Maghsoudloo, M. Sawan and B. Gosselin, "A 110-nW In-channel Sigma-delta Converter for Large-scale Neural Recording Implants," IEEE International Conference on Enginee-ring in Medicine and Biology Society (EMBC), pp. 5741-5744, 2016. This article is devoted to present an in-channel ultra-low power sigma-delta ADC to be used in neural recording applications. The ori-ginal idea was proposed by me, and the experiments were conducted at the Biomedical Microsystem La at Laval University. The manuscript was prepared by me and revised by the other authors before submission.

Introduction

A Brain Machine Interface (BMI) represents the first step toward the development of chronically implantable devices for patients suffering from neurological diseases. A practical BMI must be fully implantable, provide several hundred recording channels, consume very low energy, and present an extremely small size. Such neural interfacing microsystems have greatly enhanced our understanding of brain functions and play a key role in the development of new prostheses for treating various chronic neural diseases. A variety of neural signals have captured the interest of biologists. These signals have different amplitudes and bandwidths. A multimodal neural recording system is a machine that is able to record these different types of neural signals. Local Field Potential (LFP) signals and Action Potential (AP) or spikes are some of these neural signals. Figure1.1shows these two different types of neural signals. 100 μV 1mV

LFP

5 mVAP

(a) (b)Figure 1.1 – Two different types of neural signals. a) Local field potential neural signals. b) Action potential neural signals.

The LFP signal has maximum amplitude of 5mVp−pand the BW of 1 ∼ 100Hz, while AP signal has

maximum amplitude of 1mVp−p and the BW of 300 ∼ 5KHz [2]. Typically, in a neural interfacing

microsystem [3,4], an analog-to-digital converter (ADC) is included in the analog front-end (AFE) building block in order to digitize neural signals prior to a digital signal processing module and/or a data transmitter. An AFE comprises several cascaded stages, such as a low-noise amplifier, one or several analog filters, a second-gain stage, and a sample-and-hold circuit (SAH). Thus, the signal passes through several signal processing stages before being buffered and multiplexed towards an SAH circuit. Then, the sampled signal can be digitized using a low-power, medium resolution ADC [5]. Fig.

can be powered up wirelessly using an inductive link [6,7], and communicates using both implanted and external antennas.

Antenna Power Data Out Data In Flexible Power Coil System on Chip Analog Front End Power Wireless TX RX Stimulator Real Time User Interface Electrode Arrays Data Communication Wireless Power Transmitter Micro Controller Implantable Flexible Board Utah Electrode Arrays 1 cm

Figure 1.2 – An implantable brain computer interface.

1.1

Presentation of the project

There are several challenges in designing such a precise BMI machine. These challenges are in delive-ring a certain amount of power that is needed by the system. Increasing the electromagnetic fields of power or transferring more power than several milliwatts (mW) will damage or heat up and burn the tissue of the brain. Thus, the power budget of the system is limited to several mW. Consequently, all the blocks within the system must be designed to consume as little power as possible, while meeting the needs of the system. In order to minimize the power consumption of the AFE, there is a need to design a precise low-power, low-noise amplifier. Moreover, the ADC block needs to be designed to be ultra-low power, providing a resolution of eight bits or more. Several ADC topologies have been introduced to be used in this application, such as successive approximation register ADC, sigma delta converter, and amplitude-to-time converters like PWM generators. Finally, the transceiver block needs to be designed to consume as less power as possible while having the capacity to transmit a huge vo-lume of data at a high absorption rate in biological tissues. Another challenge in this application is the size of the entire design, since an increase in the area leads to a wider opening window and complicates brain surgery. Further, an increase in the area makes the system more expensive.

Recently, many BMIs have been published, such as [8] in which there are 64 neural recording channels and it consumes 330 µW of power. This system occupies an area of 4.6 mm x 4 mm, including the transmitter and AFE. Further, another paper has been published in [9], which presents another 128-channel neural recording and electrical stimulating interface. Each electrode can be used as a recording or stimulating channel. This system is also designed to be modular with eight channels in

each module ; it occupies a space of 3.5 mm x 2.5 mm without a transmitter block, and consumes 9.3 mW of power. In 2010, a paper was published in [10], which provides 64 recording channels with a custom probe and an integrated front end. In [6], an inductively powered 32-channel wireless neural recording system was presented, whose the front end is based on a PWM converter.

Figure 1.3 – Block diagram of the conventional AFE.

In 2012, a 96-channel neural interface which consumes 68 µW per channel was published in [11]. In 2013, a 100-channel wireless neural recording interface was demonstrated in [12]. Another neural interface was created in 2013, with 100 channels consuming a total of only 1 mW [13]. Recently, in 2014, two articles were published on neural recording, one with 455 probes and 52 active channels and another with 26,400 recording probes and 1024 active recording channels in [14,15], respectively. Apparently, the number of recording channels is being increased ; consequently, the analog front end of each channel must be designed efficiently. It must occupy an area as small as possible and consume as little power as possible. To understand a BMI and to be able to optimize it, all the blocks within an AFE must be partially studiedy. A block diagram of the AFE is illustrated in Fig.1.3.

1.2

Literature Review : Low-noise Amplifier Design

In this section, we discuss low-noise amplifiers. To improve noise performance of an LNA, first, noise sources in an amplifier must be introduced. The main sources of noise in an amplifier are flicker noise and thermal noise. Thermal noise is generated in all types of real resistors, and since transistors produce an internal resistance which is related to gm, they provide thermal noise as well. The point

is that in order to calculate the input referred noise, the output noise power must be divided by the gain of the transistor powered by two (i.e., g2m) [16]. Thus, every parameter that increases the gmwill

decrease the thermal noise, such as W /L, and drain current and mobility (µ). Since the mobility of electrons is approximately three times the mobility of holes, NMOS transistors are less noisy than PMOS transistors in the same size and drain current.The other important source of noise in amplifiers is called flicker noise. This type of noise is inversely proportional to frequency (1/f). This noise could be a considerable problem in very low frequencies because of its inverse proportionality to frequency. Moreover, this noise is inversely related to the size of the transistor, and PMOS transistors inherently provide less flicker noise than NMOS transistors.

Since working bandwidth in neural activity recording begins from 1 Hz or even less [17], the main problem in LNA design is flicker noise. Consequently, all the designs in this area are made by large

PMOS input differential pairs. The principle of a neural LNA with a high-pass filter and capacitive feedback is depicted in Fig.1.4. In this figure, to provide a very low cut-off frequency, pseudo resistors are used [17]. Pseudo resistors yield a huge resistor value, but they are nonlinear. For small input signals, they are approximately linear [17]. Using pseudo resistors causes very low cut-off frequency to be achievable using small capacitors in the range of a few pF. Thus, it becomes possible to implement in-chip capacitors. In [17], a current mirror op-amp topology with cascode output stage was used as

+

_

Vin Ref CI CI CF CF CLFigure 1.4 – Neural amplifier structure.

the LNA core. This OTA structure is illustrated in Fig.1.5. However, the current mirror op-amp has a

Bias In+ In-O u t+ O u t-Vdd

good frequency response and slew rate, but it is not the best topology considering noise performance. As its input stage is biased at a lower portion of the total bias current, a relatively smaller gmhas the

same power consumption [16]. One of the other op-amp topologies which has been used frequently thus far and has better noise performance is the cascode circuit. There are two different cascode topologies : telescopic cascode [9,18,19] and folded cascode [11,20–23]. The telescopic cascode circuitry is simpler than the folded one, since the number of transistors is smaller. It is shown in Fig.

1.6. In the telescopic cascode, if the input signal has the same DC level as the output node, it makes

V Bias In+ VDD Out In-Vbp Vbn

Figure 1.6 – Telescopic cascode low noise OTA.

the output swing highly limited. This happens because, normally, the output node DC level is at the middle supply voltage. Thus, if the input DC level is in the middle of the supply voltage, it implies that either the gate-source voltage of the input transistors is high, or the drain-source voltage of the tail current provider transistor is high. Both these voltages increase the overdrive voltage (Ve f f) of

the transistors at the input node or the tail. The better topology is to use the folded cascode. The folded cascode topology circuit diagram is illustrated in Fig. 1.7. When it comes to comparing the performances of different topologies, design architectures, and trade-offs, the figure of merit factors are useful. In this case, the figure of merit introduced in [24] is termed Noise Efficiency Factor (NEF). It is presented in the following manner :

NEF= Vrms,in

r

2 · Itotal

UT· π · 4KT · BW

(1.1) , where Vrms,inis the input referred noise, Itotal is the total current of the OTA, UTis approximately 25

V Bias In+ VDD In-Vbn1 Vbp VDD Out Vbn2

Figure 1.7 – Folded cascode low noise OTA

the best topology that can provide better noise performance with the same area is the complementary differential amplifier. The self-biased complementary differential amplifier is depicted in Fig.1.8. This

V Bias

In-VDD

Out

Out + _ In+

Figure 1.8 – Complementary differential low noise OTA.

topology has been used in [25–28]. This design doubles the SNR ratio, utilizing the same transistor sizes and power consumption ; this is possible because the gmfrom the NMOS transistor is added to

the gmof the PMOS transistor in each leg of the differential pair.

There are some innovative ideas, like sharing some parts of the LNA [29], which could be common to all the other input channels. In [19], a shared reference node leg telescopic cascode LNA has been used. This is illustrated in Fig. 1.9. in this figure, In+ path has X times wider transistors comparing to the other paths (i.e. Inx-). The disadvantage of this design is its common mode gain which leads to inter-channel cross-talk. V Bias In+ VDD Out1 In1-Vbp Vbn Out2 In2-Outx

Inx-Figure 1.9 – The partial OTA sharing.

The most important source of the noise in neural activity recording applications is flicker noise. Conse-quently, since PMOS transistors produce less flicker noise, they are preferred as the input stage tran-sistors. Also, larger transistors contribute less flicker noise [16]. Moreover, there are several different topologies that could be used as the LNA topology, and each one has its advantages and disadvan-tages. It is even possible to combine certain topologies with certain innovative ideas to improve their performance.

1.3

Literature Review : Filter Stage and Second-gain Stage

The next stages are the filter and gain stages to meet the input requirements of the ADC block. In this section, the filter and gain stages are studied. As different signals and features can be targeted to be monitored in a brain-machine, different filter bandwidths and gains are needed. Generally, there is a need for a high-pass filter to eliminate the DC offset and input low-frequency changes caused by electrochemical reactions between the probe and the body. Since there are certain signals from the

brain that are categorized in frequencies as low as 1 Hz or even lower, the high-pass filter has a very low cut-off frequency. This implies that there is a need for a significant RC ratio. In the neural activity recording application, the suitable probe is a very high impedance probe. Therefore, the high-pass filter, which is normally placed at the input and directly connected to the probe, may affect the probe characterizations. Thus, it is preferable that the input resistor be as big as possible. Moreover, it also helps to have a smaller capacitor to provide a low cut-off frequency. The idea of having a very high resistor value is to use pseudo resistors. This concept has been introduced in [17]. The LNA, with its high-pass filter, has been shown in Fig.1.4. An example of using pseudo resistors is shown in Fig.

1.10. One advantage of using pseudo resistors is that it makes the cut-off frequency achievable by

+

_

Vin Ref VTune VTune CI CI CF CFFigure 1.10 – High pass filter using programmable pseudo resistors.

capacitors as small as a few pico farads. It also provides the possibility of tuning the resistance by varying a control voltage. Pseudo resistors have the disadvantage of nonlinearity, but since the neural activity signals are so small, they are approximately linear in that range. The low-pass filter is the other part of the filtering process in this application. Several different ideas on low-pass filter design have been introduced. One is to use a big capacitor at the end of the LNA [30–33]. The other approach is to use more complex circuits like high-order GM-C filters [21,23]. A sample of GM-C filters used in a neural activity recording is illustrated in the high-pass filter Fig.1.11. After filtering, the input signal must be sufficiently amplified to be used as the ADC’s input. This gain stage is usually programmable to be suitable for a wide range of applications [34].

1.4

Literature Review : Analog to Digital Converters

When the signal is sufficiently amplified, and is also filtered, the next step is to digitize the recorded signal. In this section, the analog-to-digital converter block is described. The analog signal has to

+ _ _ + _ _ + _ _ + _ _ + _ _ + _ + + _ + Gm Gm Gm Gm Gm Gm Gm C1 CL C2 Inductor

Figure 1.11 – A 3rd order GM-C low-pass filter using LC structure

be sampled before being digitized. Then, the sampled signal is compared to the reference levels and yields the digital number corresponding to the input analog value. A simple description of an ADC is presented in Fig.1.12. Depending on the number of bits on the digital side, the number of voltage

Vin CLK CLK OUT Quantizer Sampler 0100010011 - Continuous Time - Continuous Amplitude - Analog - Digital Time - Continuous Amplitude - Analog - Digital

Figure 1.12 – A simple description to ADC functionality

levels to be compared to the sampled input are provided. These voltage levels determine the resolution of the represented signal on the digital side. The more the comparison levels, the more accurate the conversion will be. The concept of comparison to the discrete voltage levels is presented in Fig.1.13. These discrete voltage levels are created using a digital-to-analog converter (DAC). The accuracy of the ADC is directly dependent on the accuracy of this DAC. There are several errors that may be found at the converted digital signal, whose references are the errors in the DAC. These errors are due to the input voltage offset, nonlinearity, and the quantization noise. The offset is that the converter does not provide the digital value of zero when the input analog signal is at the zero level. The nonlinearity error is caused by a nonlinear relation between the converter’s output and its input analog signal. Finally, the quantization noise is the difference between the demonstrated signal output of the converted digital signal and the input analog signal.

Time

Am

p

lit

u

d

e

V12 V11 V10 V9 V8 V7 V6 V5 V4 V3 V2 V1 `Figure 1.13 – Comparison to the discrete voltage levels

1.4.1 Successive Approximation Register ADC (SAR)

Depending on the applications and number of effective digital levels, there are numerous types of ADCs. Here, only those ADCs that have been used in neural recording applications are studied here. The most used ADC in neural recording applications is the successive approximation ADC (SAR) [1,23,32,35]. The SAR ADC comprises a comparator, a DAC, and a digital control block. An example of SAR ADC is presented in Fig.1.14. In [35], an SAR converter with an internal gain is introduced.

+ _

Vin SAR Control

Register CLK Output R e gi st er DAC D0 D1 Dn O u tp u t D igi tal Wor d

Figure 1.14 – Successive approximation ADC

This converter amplifies the input signal with a programmable gain controller. In [1] and [32], a logarithmic SAR converter has been proposed, with a logarithmic relationship between the digital output value and its analog input. In a logarithmic converter, the small input values are considered as the less critical signal, and the larger amplitudes are magnified. In a neural recording application, it is useful to detect impulses. A comparison between a linear ADC converter with logarithmic converters is provided in Fig.1.15.

Figure 1.15 – Comparison between linear ADC and logarithmic ADC [1]

1.4.2 Sigma Delta Converter

The other most frequently used ADC in neural recording applications is the sigma-delta converter [36–40]. A sigma-delta converter is composed of a closed loop system. In this converter, the output digital signal is converted to an analog representation by a DAC, which is located in its feedback. The recreated analog signal is subtracted from the input signal to evaluate the error. The error is integrated at the forward path, and this integration will cause a decrease in the error in the low frequencies. A block diagram of the sigma-delta converter is depicted in Fig. 1.16. This block diagram can be

z-1 1 -z-1 DAC +_ Integrator CMP X(z) E(z) Y(z)

Figure 1.16 – Block diagram of a first order sigma-delta converter

modified as the one shown in Fig.1.17, which shows the quantization noise source. Consequently, the error signal E(z) can be calculated in the following manner :

z-1 1 -z-1 DAC +_ Integrator X(z) E(z) Y(z) ++ N(z)

Figure 1.17 – The modified model of the first order sigma-delta converter containing quantization noise.

Therefore, the output signal Y (z) can be calculated using the following equation : Y(z) = E(z) · z

−1

1 − z−1 + N(z) (1.3)

Now, it is possible to rewrite (1.3) in the following manner : Y(z) = X(z) · z −1 1 − z−1 − Y(z) · z−1 1 − z−1 + N(z) (1.4) Y(z)(1 + z −1 1 − z−1) = X(z) · z−1 1 − z−1 + N(z) (1.5) Y(z)(1 − z −1+ z−1 1 − z−1 ) = X(z) · z−1 1 − z−1 + N(z) (1.6) Y(z)( 1 1 − z−1) = X(z) · z−1 1 − z−1 + N(z) (1.7) Y(z) = X (z) · z−1+ (1 − z−1)N(z) (1.8) Considering m integrators in the forward path, (1.8) can be transformed to

Y(Z) = X (z) · z−m+ (1 − z−1)mN(z) (1.9) ( ST F(Z) = Y(z) X(z)= z −m NT F(Z) =Y(z)N(z)= (1 − z−1)m (1.10) This implies that the system transfer function is a delay by length of m, and there will be a noise shaping of the order of m as well. The quantization noise spectrum is more like white noise in the bandwidth of the input signal. However, when a sigma-delta converter noise shaping is applied to it, this noise is shaped as illustrated in Fig.1.18. Sigma-delta converters are known as oversampling rate converters. Compared to the SAR converter, which is a Nyquist rate converter, the number of samples per cycle is much more than that for the SAR converter. On the other hand, compared to SAR converters, in the sigma-delta structure, there is no need for digital control logic. Moreover,

Figure 1.18 – The noise shaping benefit of using a sigma-delta converter.

if the sigma-delta converter is made as a one-bit converter, the DAC circuit in the feedback loop is merely a straight wire. Generally, the complexity of the one-bit sigma-delta converter is less than the SAR converter. In [36], the sigma-delta loop is created in the current domain. Consequently, a single capacitor plays the role of the integrator. In addition, it plays the role of the anti-aliasing filter as well. Further, in [41], the impact of using passive integrator on the behavior of the sigma-delta converter was studied. It was revealed that it is possible to implement the integrator circuit by a passive integrator to minimize power consumption.

1.5

Literature Review : Optimizing Brain Machine Interface

In this section, we explain how to optimize the design. These techniques are extracted from different resources. First, there is an explanation in [17] that considers the parasitic input capacitor, which affects the signal-to-noise ratio at the input of the LNA. Since there is a DC coupling capacitor (that is, high-pass filter) at the input nodes of LNA, there will be a capacitive voltage divider that considers the parasitic input capacitors of the LNA.

VLNA,in= VProbe

Chigh−pass

Cparasitic,LNA+Chigh−pass (1.11)

This problem becomes worse when there is a need to minimize the noise level of the LNA. In this case, the size of the input transistors of the LNA must be enlarged. Enlarging the input transistor size leads to increasing the parasitic capacitance at the input node. In [11], there is a technique to decrease the effect of the parasitic capacitor at the input node of the LNA. The technique is to add two capacitive positive feedback from the output of the LNA to its inputs. This technique is presented in Fig.1.19as MOS-capacitors M3 and M4.

In [42], the authors discuss how to optimize the ADC block. There are several considerations from [42], which are summarized here. The first one is regarding the effective number of bits that could be achieved from an ADC in a neural recording application. In this application, the high impedance probe is a must. For an electrode with a resistance of 1 M ohm operating at 27 degree centigrade

Vin+ Vin-Ibias

i1 i2

M1 M2

M3 M4

Figure 1.19 – The parasitic input capacitor effect removal

with a 10 kHz recording bandwidth, the RMS noise voltage is 12.6 µV. Moreover, there is as much background noise, which is a sum of many smaller spikes, as thermal noise [16]. In general, the maximum amplitude of extracellular spike potentials is smaller than 1 mV, and the noise is around 20 µVrmsfor a probe resistance of 1 M ohm. Therefore, the SNR of the input signal is approximately

34 dB. This implies that regardless of how large the number of bits of the ADC is and how small the amplifier noise is, the system’s effective number of bits cannot exceed six bits. Therefore, it is reasonable to make the ADC’s SNR the same as that of the input signal, and make the amplifier’s input equivalent noise negligible, to achieve as large an SNR as possible (in this case, six bits). Optimizing the number of ADCs per channel to minimize the power consumption of the system re-quires one ADC per channel. However, if the goal is to reduce the power consumption and area of the system simultaneously, the optimized number of ADCs per channel is one ADC for 16 recording channels [42].

1.6

Thesis Outline and Summary of the Contributions

In the following chapters of this thesis, we provide a deep analysis and optimization of the front-end building blocks, and we propose new structures with better performances.

Chapter 2 is devoted to a novel current reuse front-end. The following are our main contributions : - Noise analysis of the conventional structure.

- Proposing the new current reuse structure with less noise contribution and less power consumption. - Verifying the proposed architecture using the measurement results from the chip implemented in CMOS 180-nm technology.

- Performing an in−vivo experiment to show the performance of the structure.

In chapter 3, we introduce a new multiplexed Sigma-Delta converter. Our main contributions in this regard are listed below :

- Presenting the analysis on the conventional incremental Sigma-Delta structure. - Simulating the power spectral density using the conventional structure.

- Proposing a new multiplexing scheme.

- Presenting the advantages of the proposed architecture with simulation results.

- Providing measurement results obtained from the chip implemented in CMOS 180-nm technology.

Chapter 4 presents the ultra-low power Sigma-Delta converter, which consumes only 110 nW. Our contributions in this regard are listed below :

- Analyzing the Sigma-Delta structure.

- Proposing a new circuit using a 0.6 V power supply working in the subthreshold region. - Providing the post-layout simulation results with corner analysis.

Chapitre 2

A Low-Power Current-Reuse Analog

Front-End for High-Density Neural

Recording Implants

Résumé

L’étude de l’activité cérébrale in vivo nécessite la collecte simultanée de signaux bioélectriques pro-venant de plusieurs microélectrodes afin de capturer les interactions neuronales. Dans ce chapitre, nous présentons un nouveau frontal analogique (AFE), qui peut être étendu à un très grand nombre de canaux d’enregistrement, grâce à sa petite taille faite sur silicium et à sa faible consommation d’éner-gie. Cette AFE à réutilisation de courant, qui comprend un amplificateur à faible bruit (LNA) et un amplificateur à gain programmable (PGA), utilise une nouvelle topologie de miroir de courant entière-ment différentielle utilisant moins de transistors et améliorant plusieurs paramètres de conception, tels que la consommation d’énergie et le bruit, par rapport aux implémentations de circuit d’amplificateur de réutilisation de courant précédentes. Nous montrons que l’amplificateur de réutilisation de courant proposé peut fournir un facteur d’efficacité de bruit théorique (NEF) aussi bas que 1,01, qui est le NEF théorique le plus bas fourni par une topologie LNA. Un AFE à réutilisation de courant à 4 canaux mis en œuvre dans une technologie CMOS de 0,18 µm est présenté comme une preuve de concept. Les circuits capacitifs du réseau en T sont utilisés pour diminuer la taille des condensateurs d’entrée et augmenter la précision du gain dans l’AFE. La performance mesurée de l’ensemble du système est présentée. La consommation totale par canal, y compris le LNA et le PGA, est de 9 µW (4,5 µW pour LNA et 4,5 µW pour PGA), pour un bruit d’entrée de 3,2 µV rms, atteignant une NEF mesurée de 1,94. L’AFE entière présente trois gains sélectionnables à 35,04 dB, 43,1 dB et 49,5 dB, et occupe une surface de 0,072 mm2par canal. Le circuit mis en œuvre a un taux de réjection inter-canaux mesuré à 54 dB. Les résultats d’enregistrement in vivo obtenus avec l’AFE proposée sont rapportés. Il permet de recueillir avec succès des signaux de potentiel d’action extracellulaire de faible amplitude à partir d’une microélectrode à fil de tungstène implantée dans l’hippocampe d’une souris de laboratoire.

Abstract

Studying brain activity in-vivo requires to collect bioelectrical signals from several microelectrodes simultaneously in order to capture neuron interactions. In this chapter, we present a new current-reuse analog front-end (AFE), which is scalable to very large numbers of recording channels, thanks to its small implementation silicon area and its low-power consumption. This current-reuse AFE, which is including a low-noise amplifier (LNA) and a programmable gain amplifier (PGA), employs a new fully differential current-mirror topology using fewer transistors, and improving several design parameters, such as power consumption and noise, over previous current-reuse amplifier circuit implementations. We show that the proposed current reuse amplifier can provide a theoretical noise efficiency factor (NEF) as low as 1.01, which is the lowest reported theoretical NEF provided by an LNA topology. A 4-channel current-reuse AFE implemented in a CMOS 0.18-µm technology is presented as a proof-of-concept. T-network capacitive circuits are used to decrease the size of input capacitors and to increase the gain accuracy in the AFE. The measured performance of the whole AFE is presented. The total power consumption per channel, including the LNA and the PGA stage, is of 9 µW (4.5 µW for LNA and 4.5 µW for PGA), for an input referred noise of 3.2 µVrms, achieving a measured NEF of 1.94. The

entire AFE presents three selectable gains of 35.04 dB, 43.1 dB and 49.5 dB, and occupies a die area of 0.072 mm2per channel. The implemented circuit has a measured inter-channel rejection ratio of 54 dB. In-vivo recording results obtained with the proposed AFE are reported. It successfully allows to collect low-amplitude extracellular action potential signals from a tungsten wire microelectrode implanted in the hippocampus of a laboratory mouse.

2.1

Introduction

Neural recording systems featuring several parallel readout channels enable neuroscientists to study brain neurodynamics in-vivo. Such invaluable information is critical to study and to understand the functions of biological neural networks. Moreover, such devices open up opportunities for building feedback systems to help patients with spinal cord injuries, Parkinson’s disease and other chronic neurological diseases. State-of-the-art neural recording systems consists of two main parts : 1) an implantable device typically including a data acquisition unit, a power management unit (using either a wireless power transmission link [43] or a small battery as power source [44]), as well as a wireless transmitter, and 2) an external base station made of a wireless receiver connected to a host PC [3]. Thus, the design of a suitable multichannel neural recording system must address several critical challenges. Among others, it must handle a large number of low-noise amplifiers (LNA) (typically one per channel) under stringent power budget [17]. As it must interface with implanted microelectrode arrays presenting several recording sites, the small pitch of the microelectrode arrays (a few hundred micrometers typically) usually determines the circuit density and overall system area. Heat dissipation, which needs to be kept as small as possible not to harm tissues, also puts limits on power consumption. For instance, it has been shown that a local temperature rise of only a few °C can harm adjacent tissues [45]. Power is often provided to the recording system by a small battery or by a wireless

power transmission scheme [44], which also contributes to power limitation. Additionally, the LNA circuits must present very low-noise, so the weak neural signals can be properly collected, and they must suppress the microelectrode potentials to avoid large offset voltage at the input of the LNA [17]. The LNA usually determines the overall signal-to-noise ratio of a given neural signal recording device. Therefore, the design of a suitable LNA is critical for this application as it must present low-input noise and low-power, while being scalable to very large numbers of recording channels (typically hundreds [15]). Several analog front-end (AFE) topologies were proposed to address these requirements and challenges. A robust approach consists of using an ac-coupled capacitive feedback topology consisting of feedback capacitors implemented around an operational transconductance amplifier (OTA) [17], as a first stage LNA. Such feedback topology, the goal of which is to properly amplify the neural signal while removing the electrode potentials, often uses very large resistive elements known as pseudo-resistors [17], in parallel with feedback capacitors to bias the amplifier and to create a very large-time constant high-pass filter for suppressing the dc offset voltage of the electrodes, the low-frequency noise and the drift.

In this chapter, we first review the principle of current reusing amplifiers (Fig. 2.1) which prompt for very low power consumption designs. We then provide a noise analysis of this circuit topology detailed in Section2.2.2, and we propose a new current-reuse AFE circuit, including an LNA and a programmable gain amplifier (PGA), which is improving previous implementations, in Section2.2.3

and Section 2.2.4. Additionally, we discuss the utilization of a capacitive T- network in the imple-mentation of the LNA (Section2.2.5and2.2.6) to implement small capacitors values with very high accuracy for decreasing the size of the input capacitors of the LNA. Then, in Section2.2.7we ana-lyze the noise performance of this new current reuse circuit and we show that it can reach the lowest reported theoretical noise efficiency factor (NEF). The measured performance, as well as in-vivo re-sults obtained with this front-end design fabricated in a CMOS process, are presented in section2.3. Finally, conclusions are drawn.

2.2

CURRENT REUSE ANALOG FRONT END OVERVIEW

Previously, several efforts have been devoted to improve the size, the precision and the NEF of biome-dical signal recording LNAs [46]. Several energy-efficient circuit topologies were introduced for that purpose, like the component sharing arrays [20], or the self-biased fully-differential structure [19]. Furthermore, specific circuit techniques have been proposed to improve further the noise vs power tradeoff, such as folded cascodes with low-current folds [20], reference electrode sharing [19], gm

boosting via current-splitting [47], and complementary inputs devices [48] or back-gate driven de-vices [49]. Despite this progress that is improving current techniques, an integrated AFE design sca-lable to thousands of channels for collecting the signals of large groups of neurons at once is still mis-sing. Recently, an orthogonal current-reuse structure has been presented in [50] to improve previous techniques. Such an orthogonal current-reuse structure is attractive since it yields ultra-low power by properly operating under very low-voltage supplies, without affecting the noise performance.

Further-+ _ + _ I I/2 CH1 CH2 Vin1+ Vin1-Vin2+ Vin2-VOut1 VOut2 VOut3 VOut4

Recombination

Output Stage

Stacked Input

Differential Pairs

+ _ CH2 Vin2+ Vin2-I/2 + _ I/4 CH3 Vin3+ Vin3-+ _ CH3 Vin3+ Vin3-I/4 + _ I/8 CH4 Vin4+ Vin4-+ _ CH4 Vin4+ Vin4-I/8I

v

I

v

I

v

I

v

i

o1i

o2i

o3i

o4Figure 2.1 – Conceptual representation of a four-channel stacked current-reuse amplifier. The input differential pairs share the same supply currents and the recombination and output blocks provide an output signal that is related to each corresponding input.

more, low-power consumption and robust crosstalk suppression between the stacked amplifier parts makes the orthogonal current-reuse structure (Fig.2.1) a well-suited solution for the design of a high-performance neural recording AFE. As shown in Fig.2.1, a current-reuse structure consists of stacked differential input pairs, which converts the input voltages into currents, a current recombination block, which separates the output currents assigned to each input signal, and an output stage, which uses the recombined currents to generate an output voltage that corresponds to a given low-amplitude input signal [50]. The voltage headroom required in each input differential pair is minimized by operating each input pair transistor in the sub-threshold region.

2.2.1 Principle of Current-Reuse Amplifier

The schematic of a stacked current-reuse amplifier previously presented in [51] is shown in Fig.2.2. A two-stacked input topology is shown for simplicity. Such a current-reuse circuit topology presents several stacked input differential pairs separated across a binary tree structure in which each transistor of an input pair has at most one stacked children input pair [50].

Since gm= (2µCox(W /L)Id)1/2 and Vgs= Vth+ (2Id/(µCox(W /L))1/2 equivalent transconductances

and gate-source voltages are maintained across all stacked input pair transistors by using half the transistor size in the children branches compared to the transistors of the parent branches, and by using half the current in the children branches compared to the current flowing into the parentbranches. Then, a single current source can be employed to bias all stacked differential input pairs at once,

1 :

Recombination output stages

Vcas,P Vcas,N VOut1+ Vcas,P Vcas,N V Out1-V1 V2 V3 V4 V1 V3 V2 V4 CMFB Vcas,P Vcas,N Vcas,P Vcas,N VOut2+ V Out2-M19 M20 M21 M22 M23 M24 M25 M26 M27 M28 M29 M30 M31 M32 M33 M34 M35 M36 M37 M38 CMFB in_o1

in_o1 in_o2 in_o2

io1 io1 io2 io2 IRecomb 2 IRecomb 2 IRecomb 2 IRecomb 2 B Vbn Vin1- Vin1+ Vin2+ Ibias i3 Vbn Vbn Vin2-Vin2+ W/2 L W L W L V3 V4 V2 V1 Stage1 Stage2

Two stacked input-stage current-reuse structure W/2 L W/2 L W/2 L i4 i2 i1 M1 M2 M3 M4 M5 M6 M7 M8 M9 M10 M11 M12 M13 M14 M15 M16 M17 M18 imirror imirror imirror imirror 4 4 4 4

Figure 2.2 – A conventional two-stage folded-cascode current reused amplifier. Two stacked input differential pairs share a same bias current source and each recombination output stage consumes B times the Ibias where B should be made smaller than 1. The common mode feedback circuits are also depicted.

the tail currents of which are coming from the previous stages. Indeed, since the same total current flows into Stage 1 and Stage 2 (Fig.2.2), both stages have equal overall gmvalues. The small signal

currents output i1, i2, i3, i4are independent and linear combinations of the several output currents that

are derived from one output branch which corresponds to a given stacked input pair. For instance, in Fig.2.2, Stage 1 has a single input pair, while Stage 2 has two input pairs, having identical input voltages Vin2+and Vin2− , in parallel. Then, in order to generate Vout1−and Vout1+, the corresponding

small signal output currents io1− and io1+ are re-constructed by summing output currents i1, i2 and

i3 , i4 (Fig. 2.2) respectively in the Recombination output stage 1. Similarly, Vout2+ and Vout2− are

generated by summing i1, i3, and i2, i4in the Recombination output stage 2. The small signal output

currents are given by (2.1) to (2.4). i1= ( gm1 4 .Vin1+) + ( gm2 4 .Vin2+) (2.1) i2= (gm1 4 .Vin1+) + (− gm2 4 .Vin2+) (2.2) i3= (− gm1 4 .Vin1−) + ( gm2 4 .Vin2−) (2.3) i4= (− gm1 4 .Vin1−) + (− gm2 4 .Vin2−) (2.4) 2.2.2 Noise Analysis

The thermal noise density of a MOSFET can be approximated by (i2n= 4KT γgm) where K is the

Boltzmanns constant (1.38 × 10−23J/K), T is the temperature in Kelvin, γ is a constant (which ap-proximately equal to 2/3 in long-channel transistor processes and 2∼3 in short-channel transistor pro-cesses [46]) and gmis the transconductance of the transistors. Considering a ratio B : 1 between M19∼26

and M15∼18in the circuit shown in Fig.2.2, the thermal noise current contribution of all transistors at

the output nodes Vout1and Vout2are

i2n,o2= 4KT γ(4B2gm3+ 4B2gm7+ 4B2gm15+ 4gm23+ 2gm37) (2.6)

As mentioned above, since the size of M3is half of M1, and the drain current of M3is half of M1, gm3

has half the value of gm1(gm1= 2gm3). Hence, the input-referred noise is obtained as follows :

Vn,in12 =8KT γ gm1 (1 +2gm7 gm1 +2gm15 gm1 +2gm19 B2g m1 + gm35 B2g m1 ) (2.7) Vn,in22 =8KT γ 2gm3 (1 +2gm7 2gm3 +2gm15 2gm3 + 2gm23 2B2g m3 + gm37 2B2g m3 ) (2.8)

It can be shown that Vn,in22 = Vn,in12 if (W /L)3and (W /L)4are equal to 1/2(W /L)1. In addition, it can

be shown that the total supply current Itotal can be expressed by

Itotal= Ibias+ Imirror+ NIRecomb= Ibias+ Imirror(1 + NB) (2.9)

where Imirrorand IRecombare the currents flowing in the current mirror (Fig.2.2) and the recombination

output stage, respectively. The total current can be approximated to Itotal= Ibias+ Imirrorif B is chosen

significantly small.

2.2.3 Proposed Current-Reuse Amplifier Design

We propose a new current-reuse structure based on a simplified current-mirror topology (shown in Fig.2.3) which uses fewer transistors in the signal path compared to the conventional topology shown in Fig.2.2. Indeed, the conventional circuit (Fig.2.2) folds the currents i1, i2, i3, i4through M11∼14,

where the currents are being mirrored by M15∼18 towards the corresponding output recombination

stages. In the proposed circuit (Fig.2.3), the currents are mirrored directly by M7∼10, which avoids

the utilization of M15∼18, compared to the conventional folded-cascode topology. Therefore, the Itotal

of this new circuit is given by

Itotal= Ibias+ NIRecomb= Ibias(1 + NB) (2.10)

where N is the number of stacked inputs requiring as much recombination stages, NIRecombis the total

supply current of the recombination stages, and B = (IRecomb/Ibias). Thus, Itotal can approach Ibiasif a

sufficiently small ratio B is used. As for noise analysis of this new proposed circuit, we set a ratio of B: 1 between M11∼18and M7∼10in Fig.2.3to find the output current noises of circuit branches 1 and

2 :

i2n,o1= 4KT γ(2gm1+ 4gm7+ 4B2gm11+ 2B2gm27) (2.11)

i2n,o2= 4KT γ(4gm3+ 4gm7+ 4B2gm15+ 2B2gm29) (2.12)

Hence, dividing (2.11) and (2.12) by the gain of the LNA gives the input-referred noise : Vn,in12 =8KT γ gm1 (1 +2gm7 gm1 +2gm11 B2g m1 + gm27 B2g m1 ) (2.13)

1 : B Vin1+ Vin1-Vin2+ Vin2-Ibias i3 Vin2+ W/2 L W L V3 V4 V2 V1 Stage1 Stage2

Two stacked input-stage current-reuse structure W/2 L W/2 L W/2 L i4 i2 i1 W L M1 M2 M3 M4 M5 M6 M7 M8 M9 M10 CMFB Vcas,P Vcas,N VOut1+ Vcas,P Vcas,N V Out1-V1 V2 V3 V4 V1 V3 V2 V4 CMFB Vcas,P Vcas,N Vcas,P Vcas,N VOut2+ V Out2-Recombination Output Stage 1 VCM A1 VCM A2 M11 M12 M13 M14 M15 M16 M17 M18 M19 M20 M21 M22 M23 M24 M25 M26 M27 M28 M29 M30

in_o1 in_o1 in_o2 in_o2

io1 io1 io2 io2 Recombination Output Stage 2 IRecomb 2 IRecomb 2 IRecomb 2 IRecomb 2

Figure 2.3 – The proposed optimized current reused amplifier circuit. A two-stage current mirror-based current-reuse amplifier topology uses less transistors than previous topologies. The current mir-rors at the input of the recombination output stages scale the output current of the stacked input pairs by a factor of B. Vn,in22 =8KT γ 2gm3 (1 +2gm7 2gm3 + 2gm15 2B2g m3 + gm29 2B2g m3 ) (2.14)

As for the conventional circuit, it can be shown that Vn,in22 = V2

n,in1if (W /L)3and (W /L)4are equal to

1/2(W /L)1. In these conditions, it can be seen that the proposed design has less input referred noise

compared to the conventional circuit shown in Fig.2.2, the noise of which is given by (2.7) and (2.8). Additionally, its power consumption is reduced since the Imirror formed by transistors M15 18 in Fig.

2.2are removed in this new design (Fig.2.3).

Vin1+ Vin2+ Vin2-Ibias Wp/2 Lp Wp Lp V2 Stage1 Stage2

Four stacked input-stage current-reuse structure Wp/2 Lp M1 M3 M4 Vin3+ Vin3-Wp/4 Lp Wp/4 Lp Vin4- Vin4+ Wp/8 Lp Wp/8 Lp Vin4+ Wp/8 Lp Wp/8 Lp Vin3+ Wp/4 Lp Wp/4 Lp Vin4- Vin4+ Wp/8 Lp Wp/8 Lp Wp/8 Lp Wp/8 Lp Vin1+ Vin2+ Wp/2 Lp Wp Lp Wp/2 Lp M2 M5 M6 Vin3-Wp/4 Lp Wp/4 Lp Vin4- Vin4+ Wp/8 Lp Wp/8 Lp Wp/8 Lp Wp/8 Lp Vin3+ Wp/4 Lp Wp/4 Lp M4 Vin4- Wp/8Lp Vin4+ Wp/8 Lp Wp/8 Lp Wp/8 Lp Stage3 Stage4 i3 V3 i4 V4 M9 M10 i1 V1 i2 M7 M8 i5 V5 i6 M11 M12 i7 V7 i8 M13 M14 V6 V8 V10 V11 i11i12V12 M17 M18 i9 V9 i10 M15 M16 i13 V13 i14 M19 M20 i15 V15 i16 M21 M22 V14 V16 Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Wn Ln Vds_bias

Figure 2.4 – Schematic of the implemented four stacked-input stage using the proposed optimized current reused amplifier circuit. In this design, Wp= 1000 µm, Lp= 0.8 µm, Wn= 80 µm, Ln= 4

µ m, Ibias= 2.5 µA.

2.2.4 Current-Reuse AFE Design

We used this improved current-reused amplifier circuit to implement a new advanced neural recording AFE including a four-channel LNA and a four-channel PGA (Fig.2.4 and Fig.2.5). Increasing the number of stacked inputs by 2 compared to the circuits of Fig.2.2 and2.3gives 4 times additional