Vers une reconfiguration dynamique partielle parallèle par prise en compte de la régularité des architectures FPGA-Xilinx

Texte intégral

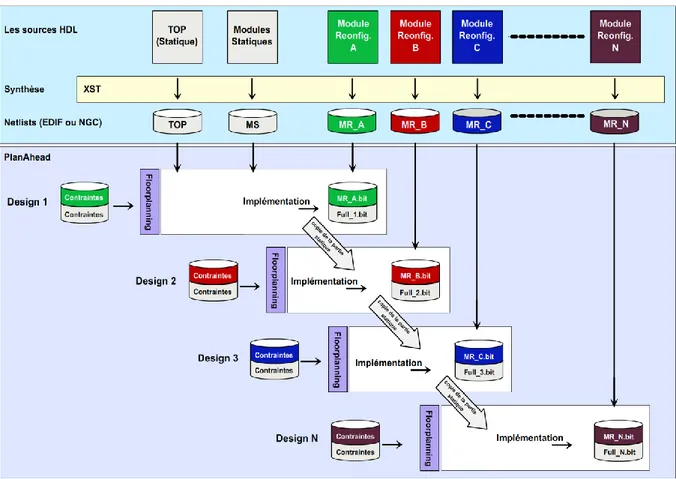

Figure

Documents relatifs

Dans cet article on montre que contrairement au cas du flot dynamique maximal il n* existe pas nécessairement un flot dynamique maximal de coût minimal qui soit un flot répété, On

Pour cela, MGP s’appuie sur deux stratégies : Open Check (OC) qui vérifie si le nouveau but est présent dans l’arbre de recherche déjà construit lors d’une précédente

Aménagement foncier agricole et forestier – morcellement des surfaces agricoles – division volontaire des terres agricoles – commission départementale d’aménagement

En conformité avec les dispositions du Règlement des études collégiales (RRÉC), notamment l=article 11, le ministère de l=Éducation déposait en septembre 1998, la

Ils ont été étendus sur des cartes cibles Xilinx dans le but d’avoir un « grand » TP alliant l’intégration d’un périphérique matériel Libre dans un SoPC

Plutôt que d’utiliser une syntaxe basée sur des évolu- tions de la structure générale du modèle, d’un état initial vers un état final, nous avons choisi de présenter une

Cette r` egle (d 21 ) d´ ecrit le traitement d’un investigateur lors du de phase d’un groupe d’investigateurs de l’exploration vers l’action. Une fois l’initialisation

1 - Une caract´erisation a priori partant sur le D-enveloppe de R de l’existence d’un commutant non trivial est n´ecessaire pour aborder l’´etude des applications rationnelles