HAL Id: hal-02348279

https://hal.archives-ouvertes.fr/hal-02348279

Submitted on 5 Nov 2019

HAL is a multi-disciplinary open access

archive for the deposit and dissemination of

sci-entific research documents, whether they are

pub-lished or not. The documents may come from

teaching and research institutions in France or

abroad, or from public or private research centers.

L’archive ouverte pluridisciplinaire HAL, est

destinée au dépôt et à la diffusion de documents

scientifiques de niveau recherche, publiés ou non,

émanant des établissements d’enseignement et de

recherche français ou étrangers, des laboratoires

publics ou privés.

Communication-aware scheduling on an IMA

architecture: invited paper

Émilie Bérard-Deroche, Jean-Luc Scharbarg, Christian Fraboul

To cite this version:

Émilie Bérard-Deroche, Jean-Luc Scharbarg, Christian Fraboul. Communication-aware scheduling on

an IMA architecture: invited paper. ACM SIGBED Review, Association for Computing Machinery

(ACM), 2016, 13 (3), pp.23-24. �10.1145/2983185.2983188�. �hal-02348279�

Any correspondence concerning this service should be sent

to the repository administrator: tech-oatao@listes-diff.inp-toulouse.fr

This is an author’s version published in:

http://oatao.univ-toulouse.fr/22337

To cite this version:

Deroche, Emilie and Scharbarg, Jean-Luc and

Fraboul, Christian Communication-aware scheduling on an IMA

architecture: invited paper. (2016) SIGBED Review, 13 (3). 23-24.

ISSN 1551-3688

Official URL

DOI : https://doi.org/10.1145/2983185.2983188

Open Archive Toulouse Archive Ouverte

OATAO is an open access repository that collects the work of Toulouse

researchers and makes it freely available over the web where possible

Communication-aware

scheduling on an IMA

architecture

Invited

paper

Emilie Deroche

1,2,Jean-Luc Scharbarg

1, Christian Fraboul

11Université de Toulouse - IRIT-INPT/ENSEEIHT - 2, rue Camichel - 31071 Toulouse - France 2Airbus Group SAS - Airbus Group Innovations - 18, rue Marius Terce - 31025 Toulouse - France

{Firstname.Lastname}@enseeiht.fr

ABSTRACT

Integrated modular Avionics (IMA or ARINC 651), as it is currently implemented in large aircrafts, uses a limited num-ber of complex processors interconnected through a commu-nication network (AFDX or ARINC 664). The allocation of avionics applications is done according a communicating partitions model (APEX or ARINC 653) needed for guaran-teeing robust partitioning when sharing processors (TDMA like schedule) and communication network (APEX channel). On smaller aircrafts (such as helicopters) the objective (due to room and weight constraints) is to use les complex proces-sors and consequently to increase their number. Implement-ing such a distributed IMA architecture leads to a global (more complex) integration problem, which is twofold. Al-location and scheduling of partitions on each shared pro-cessor as well as end-to-end communication delays among distributed partitions must be compatible in order to guar-antee timing requirements of distributed avionics applica-tions. This paper points out the complexity of composing the two aspects of this integration problem on different pos-sible target architectures.

1.

INTRODUCTION

Helicopter and aircraft industries attempt to reduce weight and power consumption. The Integrated Modular Avionics (IMA) architecture is a first step in this direction: instead of having one function per processor like in federated architec-tures, several functions share the same processor. Moreover, communication means are also shared to reduce the number and the weight of cables [1] [3].

In large aircraft, processing units are grouped in a limited number of centralized racks [3]. But in smaller aircraft such as helicopters, the idea is to integrate equipment in unused area. Moreover new devices have to be positioned so as to balance weight in the whole helicopter.

To face these new constraints, one way is to have a larger number of (possibly less complex) processors that can be distributed in the whole helicopter. The problem is then to

guarantee timing properties of distributed avionics systems. In this paper we show that a compositional approach is needed to find an allocation that respects both scheduling and communication constraints.

2.

PROBLEM STATEMENT

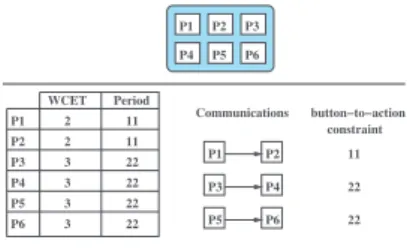

Figure 2 gives an overview of a simple avionic system exe-cuting on one processor. It is composed of a set of partitions (P 1 . . . P 6 in the example) with a period and a Worst-Case Execution Time (WCET) per partition, as well as a set of communication channels between partitions (from P 1 to P 2, P 3 to P 4 and P 5 to P 6 in the example).

P1 2 P4 P3 P2 P6 P5 3 3 3 3 2 WCET Period 11 11 22 22 22 22 Communications button−to−action P1 P3 P5 P2 P4 P6 constraint 11 22 22 P1 P2 P3 P6 P5 P4

Figure 1: Simple avionic system

According ARINC 653, scheduling of the partitions on the processor is statically defined by a MAjor Frame (MAF). A MAF is a periodic schedule where slots are assigned to the partitions, based on their period and WCET. Figure 2 shows a valid MAF for the avionic system in Figure 2. The schedule is repeated every 22 ms (least common multiple of the periods). Partitions P 1 and P 2 execute twice (every 11 ms) while other ones execute every 22 ms.

P2 4 WC P3−>P4 6 6 WC P5−>P6 P3 P4 0 2 4 7 10 P1 P2 P5 P6 11 13 15 18 21 P1 WC P1−>P2

Figure 2: A valid MAF on one powerful processor End-to-end communication constraints have to be guaran-teed by the MAFs. Different semantics are possible for these constraints, depending on the transmitted data [2]. In the context of this paper, we assume a button-to-action delay, which considers the first reaction to a data, as illustrated in Figure 2 for communication P 1 → P 2. Constraints are given in Figure 2. The MAF in Figure 2 insures them.

As explained in Introduction, a more distributed archi-tecture composed of less powerful processors has to be de-ployed for small aircrafts or helicopters. Partition WCETs

P1

P2 P2 P2

P1

button−to−action delay

Figure 3: End-to-end communication semantic

are then increased. The challenge is to find an optimal allo-cation that respects end-to-end constraints. The alloallo-cation is defined by the number of processors, assignment of the partitions on the processors and MAFs.

Let’s study the allocation of system in Figure 2 on less powerful processors (WCET is 4 ms for P 1 and P 2, 6 ms for the other partitions). Figure 2 shows that candidate al-locations on two processors are rejected for different reasons. In the upper left solution, P 1 and P 2 are allocated to the

P1 P2 0 4 8 11 15 19 22 26 30 proc1 proc2 P2 P1 P1 P2 P4 P5 P3 P3 0 6 12 18 22

P1 and P2 on the same processor

No space for P6 => no possible MAF

P2 P2 P1 P1 P1 P2 P2 P2 P2 P2 P2 P3 P4 P3 P1 P1 0 4 8 15 19 end−to−end delay P1−>P2: 19 delay constraint exceeded

0 4 8 11 15 19 22 26 30

proc1 proc2

0 6 12 18 22

P1 and P2 on different processors

P1 and P2 on different processors with oversampling of P2

No space for P5 and P6 => no possible MAF

Figure 4: No valid allocation on 2 processors same processor and there is no space for another partition on this processor. Thus the four remaining partitions have to be allocated to the other processor, which is impossible. In the right solution, P 1 and P 2 are allocated to different processors, leading to a possible missed end-to-end deadline for P 1 → P 2. One solution would be to oversample P 2, i.e. to execute it every 5.5 ms (twice per period). It leads to the lower left solution, which is also rejected since there is not enough space for remaining partitions.

This small example shows that two types of properties have to be respected: valid MAFs for partition assignment to the processors and end-to-end constraints. Existing ap-proaches consider separately both problems. We argue that an approach has to consider both problems at the same time to be efficient.

3.

PROPOSED APPROACH

The problem can be summarized in the following way. The goal is to allocate a set of communicating partitions on a physical architecture (set of interconnected processors). Each partition is defined by a period and a WCET on the considered processor. A delay constraint is associated to each communication channel between partitions. Different architectures have to be considered, with different numbers of processors. For each architecture, every possible partition allocation is analyzed. The goal is to find a valid scheduling (valid MAF on each processor) which respect communica-tion constraints.

In a first step, we developped an exhaustive analysis. A set of candidate architectures are selected (number of pro-cessors, interconnection means). For each architecture, Each possible allocation of the partitions on the processors is tested. An allocation is valid if MAFs exist which respect end-to-end constraints. An exhaustive search is done on

MAFs. At the end of the overall process, a set of valid allo-cations is obtained.

This preliminary tool has been used to analyze the Ve-hicle Monitoring System (VMS) depicted in Figure 3. It provides parameter values and alerts the pilot when a pa-rameter is close to the alarm threshold. This system is up to now deployed on two duplex Aircraft Management Comput-ers (AMCs), four multi-function displays (MFDs) and local I/Os. It includes 7 communicating partitions with four in-stances of each partition for redundancy reason.

Figure 5: Vehicle Monitoring System We have explored possible allocations when less powerful processors are used (WCET are increased by 33 %), con-sidering one instance per partition. Thanks to the tool, we have shown that one single valid allocation does exist with two processors, while no valid allocations exist with 1, 3 and 4 processors. Considering four instances per partitions leads to an execution time issue (all possible solutions are tested).

4.

CONCLUSION

The problem introduced in this paper concerns the dis-tribution of an IMA architecture using less powerful pro-cessors, in order to deal with small aircraft and helicopters. The applicative architecture includes a set of communicating partitions which are allocated to the processors. An alloca-tion is valid if both scheduling of partialloca-tions and end-to-end constraints are guaranteed. The exhaustive search consid-ered in this paper is only a first step, since it cannot deal with large case studies. Thus a heuristic approach has to be defined.

5.

REFERENCES

[1] P. Bieber, F. Boniol, M. Boyer, E. Noulard, and C. Pagetti. New challenges for future avionic architectures. Journal Aerospace Lab., 4, May 2012. [2] N. Feiertag, K. Richter, J. Norlander, and J. Jonsson.

A compositional framework for end-to-end path calculation of automotive systems under different path semantics. In CRTS, Barcelona, Spain, November 2008. [3] J. Moore. Digital Avionics Handbook, chapter 33:

Advanced Distributed Architecture. CRC Press, 2 edition, 2001.