Du Modèle à l'exécution : Traduction Automatique d'un Réseau de Petri Interprété en Langage VHDL

Texte intégral

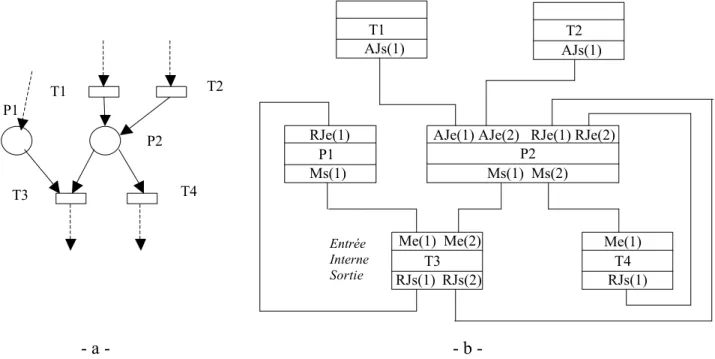

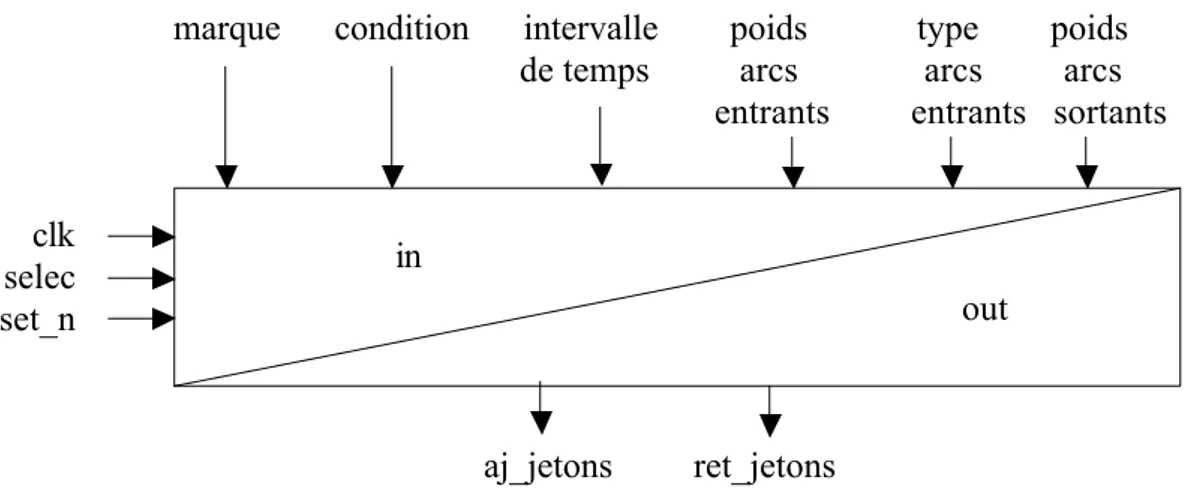

Figure

Documents relatifs

Ghania SLIMANI, 2004, «Modélisation comportementale des circuits analogiques et mixtes en langage VHDL-AMS», Mémoire de magister, Université de Constantine 1..

Pour ces attributs, le préfixe doit être un objet (signal, variable, constante) de type tableau, un sous-type tableau contraint,.un type pointeur ou un alias y faisant référence..

Permet la configuration configuration sur FPGA ou la réalisation d'un circuit dédié (ASIC)... L'entité est la description de l'interface

Conception de circuits et langage VHDL modélisation et synthèse.. Patrice

Pour utiliser les types unsigned et signed (que l’on utilise systématiquement pour représenter des nombres qui sont physiquement des fils), il faut placer au début de la

Utiliser les propriétés des signaux pour plus de généricité. ๏ Les signaux et les variables ont des propriétés qui vous permettent de simplifier l’écriture du

Formation VHDL Vahid MEGHDADI.. Conception

-- permet d'utiliser l'addition non signée avec le type STD_LOGIC_VECTOR use ieee.std_logic_unsigned.all;. entity