Faculte de genie

Departement de genie electrique et de genie informatique

DEVELOPPEMENT D'UNE TECHNOLOGIE NMOS POUR LA

CONCEPTION DE FONCTIONS ELECTRONIQUES AVANCEES

Memoire de maitrise

Speciality : genie electrique

Benoit-Louis BERUBE

Jury: Serge CHARLEBOIS

Jean-Francois PRATTE

Jacques BEAUVAIS

Sherbrooke (Quebec), Canada Septembre 2010

1*1

Library and Archives

Canada

Published Heritage

Branch

395 Wellington Street

OttawaONK1A0N4

Canada

Bibliotheque et

Archives Canada

Direction du

Patrimoine de I'edition

395, rue Wellington

Ottawa ON K1A 0N4

Canada

Your file Votre reference ISBN: 978-0-494-70808-8 Our file Notre reference ISBN: 978-0-494-70808-8

NOTICE:

AVIS:

The author has granted a

non-exclusive license allowing Library and

Archives Canada to reproduce,

publish, archive, preserve, conserve,

communicate to the public by

telecommunication or on the Internet,

loan, distribute and sell theses

worldwide, for commercial or

non-commercial purposes, in microform,

paper, electronic and/or any other

formats.

L'auteur a accorde une licence non exclusive

permettant a la Bibliotheque et Archives

Canada de reproduire, publier, archiver,

sauvegarder, conserver, transmettre au public

par telecommunication ou par Nnternet, prefer,

distribuer et vendre des theses partout dans le

monde, a des fins commerciales ou autres, sur

support microforme, papier, electronique et/ou

autres formats.

The author retains copyright

ownership and moral rights in this

thesis. Neither the thesis nor

substantial extracts from it may be

printed or otherwise reproduced

without the author's permission.

L'auteur conserve la propriete du droit d'auteur

et des droits moraux qui protege cette these. Ni

la these ni des extra its substantiels de celle-ci

ne doivent etre imprimes ou autrement

reproduits sans son autorisation.

In compliance with the Canadian

Privacy Act some supporting forms

may have been removed from this

thesis.

Conformement a la loi canadienne sur la

protection de la vie privee, quelques

formulaires secondaires ont ete enleves de

cette these.

While these forms may be included

in the document page count, their

removal does not represent any loss

of content from the thesis.

Bien que ces formulaires aient inclus dans

la pagination, il n'y aura aucun contenu

manquant.

• • I

RESUME

Ce memoire de mattrise presente le developpement d'une technologie NMOS utilisee en enseignement au le r et 2e cycle et comme preuve de concepts en recherche a YUniversite de

Sherbrooke. Le developpement est base sur la technologie JOPE a 6 masques utilisee en

enseignement depuis les annees 90. Le but de ce projet est d'optimiser ce procede pour augmenter la r e p r o d u c t i b l e des circuits et la densite d'integration. Les problemes de JOPE sont une forte resistivite de couche du polySi, une grande resistivite des contacts aluminium/polySi et

aluminium/zone active ainsi qu'une grande fluctuation de la tension de seuil des transistors.

Le procede de fabrication JOPE a ete optimise pour creer JOPE2 afin d'ameliorer les proprietes physiques des composantes et atteindre les objectifs fixes. Des circuits ont ete fabriques contenant des structures de caracterisations et des circuits numeriques et analogiques concus avec une regie de longueur de grille minimale de 2 urn.

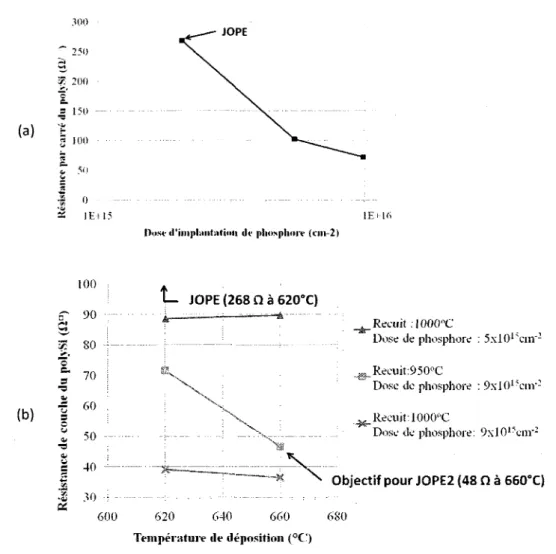

La resistivite du polySi de JOPE2 est diminuee d'un facteur 5 en augmentant la temperature de deposition de la couche par LPCVD et en ajoutant une implantation ionique dediee en plus de celle deja prevue avec le procede autoaligne pour les sources/drains. De cette facon, la resistivite des contacts aluminium a polySi est diminuee d'un facteur 10. La resistivite des contacts aluminium a zone active est diminuee d'un facteur 20 en augmentant la dose d'implantation ionique des sources/drains. JOPE2, tout comme JOPE, presente une variation importante de la tension de seuil causee par les charges d'interfaces Si/Si02 et la variation de la resistivite du substrat utilisee (1 a l O n - c m ) . Le faible rendement du procede, evalue a 47%, est cause par la faible stabilite des contacts, la grande densite de defauts et les limitations en ce qui attrait a I'alignement des masques.

Pour faire suite a ce projet, un procede NMOS a 3 u,m est recommande afin d'augmenter le rendement en diminuant I'impact des defauts, ameliorant la stabilite des contacts et en augmentant la qualite de I'alignement. De plus, pour augmenter la stabilite de la tension de seuil il est recommande d'utiliser des tranches hautes resistivite. Le procede recommande devrait permettre de fabriquer des circuits complexes bases sur des transistors NMOS avec un rendement de 80 %.

Mots-cles: microelectronique, conception de circuits integres, NMOS, microfabrication, caracterisation electrique, mesures statistiques de defauts et enseignement.

REMERCIEMENTS

J'aimerais remercier sincerement Pierre Langlois, Jean-Francois Bedard et Abdelatif Jouad pour I'aide significative qu'ils m'ont apportee tout au long du projet.

Un merci special a Serge Charlebois pour m'avoir appuye et permis d'accomplir ces travaux qui ont ete pour moi une opportunity extraordinaire de parfaire mes connaissances.

Merci beaucoup au Centre d'excellence en genie de I'information (CEGI) d'avoir cru au projet et I'avoir supporte financierement.

Merci a Jean-Francois Pratte et Jacques Beauvais pour le temps pris pour la correction de ce document.

Finalement, un merci chaleureux a ma mere et mon pere pour m'avoir encourage et avoir cru en moi dans les moments les plus difficiles comme dans les moments les plus forts.

TABLE DES MATIERES

Chapitre 1 Introduction 1 1.1 Miseen contexte 1 1.2 Objectifs 3 1.3 Methodologie 4 1.3.1 Stabilisation de la technologie 4Chapitre 2 Etat de I'art 7 2.1 Les debuts du NMOS 7 2.2 Precedes NMOS utilises a titre pedagogique 9

2.3 Precedes CMOS utilises aujourd'hui 11 2.3.1 Utilisation en enseignement 11 2.3.2 Utilisation en industrie 11 2.4 Impacts de la reduction des dimensions 12

2.5 Techniques de fabrication 13

2.5.1 Dopage 13 2.5.2 Recuit d'activation des porteurs 14

2.5.3 Gravure du Si02 14

2.5.4 Gravure du Polyl et M e t a l l 15 2.5.5 Deposition d'aluminium 16

2.5.6 Saliciure 16

Chapitre 3 Precede de fabrication 17

3.1 JOPE 17 3.1.1 Description du precede 17

3.1.2 Description des circuits 19 3.1.3 Problemes de la technologie 20

3.2 JOPE2 22 3.2.1 Ajustement de la tension de seuil 23

3.2.2 Definition des grilles 28 3.2.3 Dopage du Polyl 29

Chapitre 4 Realisations et resultats 33

4.1 Modele SPICE 35 4.2 Implementation des circuits 36

4.2.1 Puces 36 4.2.2 Alignement 38 4.3 Puce A - Circuits de caracterisation 39

4.3.1 Chames de transistors 40 4.3.2 Condensateur MOS 46 4.3.3 Pont en croix 55 4.3.4 Structure de Kelvin 58 4.3.5 Structure de mesures statistiques de defauts : 60

4.4 Puce B - Circuits complexes 63

4.5 Autres resultats ....66 4.5.1 Photolithographie 66 4.5.2 Taux de gravure 66 4.5.3 Desalignement de masque 68

4.5.4 Definition de la zone active 68 4.5.5 Deposition d'oxyde PECVD 69

Chapitre 5 Analyse des resultats 71

5.1 Discussion 71 5.1.1 Rendement 71 5.1.2 Stabilite de la tension de seuil 73

5.2 Recommandations 73 5.2.1 Procede de fabrication 73 5.2.2 Autres recommandations 75

Chapitre 6 Conclusion 79

Annexe A Procede JOPE etJOPE2 81

Annexe B Evaluation du SOD 83

B.l Sommaire 83 B.2 Nettoyage pre-procede et post-procede 84

B.3 Etalement du produit et recuit doux 85

B.4 Recuit dur 86 B.4.1 RTA 86 B.4.2 Fournaise 86

Annexe C Procede recommande 89

Annexe D Regies de conception 101

LISTE DES FIGURES

Figure 2.1. Comparaison d'un inverseur logique CMOS en (a) et NMOS en (b) 9

Figure 2.2. Vue du dessus (masques) et en coupe d'un transistor {{90 Parent,D.W. 2007}} 10

Figure 2.3 Vue en coupe de deux contacts de diametre plus petit que I'epaisseur de I'oxyde

(d<e) pour une gravure anisotrope (a) et isotrope (b)... 15

Figure 3.1 Tension de seuil en fonction de I'epaisseur d'oxyde de grille pour differente

resistivite de substrat 21

Figure 3.2 Etats de I'energie pour la grille et le canal des transistors a enrichissement (a) et

a appauvrissement (b) 25

Figure 3.3 Epaisseur d'oxyde de grille en fonction de I'energie d'implantation de bore (a) et de phosphore (b) trouve a partir de simulation SRIM pour obtenir le maximum de porteurs

a 50 nm de profondeur 27

Figure 3.4 Comparaison des donnees de simulation MicroTec et de I'equation developpee de la concentration de porteurs en fonction de la dose d'implantation pour differentes

energies 28

Figure 3.5 Resistance de couche du polySi en fonction de la dose d'implantation ionique de phosphore avec une temperature de deposition de 620°C et de recuit de 950°C (a) en resistance de couche du polySi fonction de la temperature de deposition pour 3 echantillons, avec un recuit de 1000°C et une dose d'implantation de 5xl01 5cm~2, avec un recuit de 950°C et une dose d'implantation de 9 x l 01 5 cm'2 et finalement, avec un recuit de

1000°C et une dose d'implantation de 9 x l 01 5 cm"2 (b) 31

Figure 4.1 Plan de fabrication 34

Figure 4.2 Schema detaillant la disposition et le contenu des puces sur la tranche 37

Figure 4.3 Marque utilisee sur les puces pour I'alignement fin des masques 38

Figure 4.4 Transistor de 100/2 u.m separe en quatre doigts 4 1

Figure 4.5 Courant de grille en fonction de la tension de grille pour un transistor no.7 de la tranche A (a) et tension de claquage du drain en fonction de la longueur de grille pour des

transistors de la tranche G et des simulations TCAD (b) 45

Figure 4.6 Reponse en frequence de transistors de 20/5u.m de 50 et 100 nm d'oxyde de grille par une mesure du gain d'un amplificateur de tension en comparaison avec la reponse en frequence de Cox determinee par une mesure CV (a) et amplificateur de tension utilise

pour mesurer le gain en fonction de la frequence (b) 46

Figure 4.7 Connectivity utilisee pour les mesures CV 48

Figure 4.8 Courbe CV apres recuit a 300°C avec tension de grille positive (VG+) et negative

(VG-) pour JOPE (a) et JOPE2 (b) 49

Figure 4.9 Courbe CV en hysteresis pour JOPE (a) et JOPE 2 (b) 51

Figure 4.10 Circuit equivalent pour la mesure de la conductance Gp necessaire pour le calcul

de Qit avec le circuit complet MOS (a), le circuit contenant la conductance (b) et les donnees

mesurees (c) 5 1

Figure 4.11 Densite d'etats d'interface Qit de JOPE et de JOPE2 avec et sans charge mobile a

Tinterface Si/Si02 53

Figure 4.12 Structure de pont en croix permettant de mesurer la resistance de couche et la largeur effective de lignes (a) en comparaison avec les deux structures separees de JOPE : la

mesure de Van der Pauw (b) et la mesure de largeur effective (c) 55

Figure 4.13 Distribution des mesures de resistance de couche du Polyl (a) et Metall (b) 57

Figure 4.14 Schemas de la structure de Kelvin 58

Figure 4.15 Resistance de contact M l / Z A et M l / P i 59

Figure 4.16'Courbes l-V d'une chaTne de 64 contacts Ml/Pi pour JOPE et de 128 contacts

Ml/Pi pourJOPE2 59

Figure 4.17 Schemas de masques de la structure de multiplexage passif de resistances en serpentins (a) avec le schema-bloc des 8 resistances SI a S8 et des plots N l a N4 et K l a K4

(b) ainsi que le schema electrique utilise pour la mesure (c) 60

Figure 4.18 Schema electrique de I'amplificateur operationnel couple avec 1'amplificateur

AB (b) accompagne des dessins de masques (b) 64

Figure 4.19 Schema electrique du compteur binaire 4 bits (a) accompagne des dessins de

masques (b) 65

Figure 4.20 Configuration d'un inverseur avec charge active a appauvrissement (a) et a

enrichissement (b) 66

Figure 4.21 Distribution des mesures de la surgravure prises au microscope optique a 20X 67

Figure 4.22 ChaTne de contacts graves dans NH4F:HF (6:1) de JOPE2 68

Figure 4.23 Photo d'un transistor sur lequel on y voit le desalignement entre les

masques 1 et 2 (a) avec la vue en coupe theorique (b) 69

Figure 4.24 Vue en coupe du polySi avec oxyde PECVD sur oxyde de grille de 100 nm de la

IX

Figure 5.1 Transistor 24 (W/L de 100/2) de la tranche A (a) qui demontre un probleme de surgravure desalignement expliquant le dysfonctionnement et une structure fonctionnelle

e n G ( b ) 72

Figure A . l Vues en coupes aux etapes importantes des procedes JOPE et JOPE2 81

Figure B.l Image de polysilicium non-nettoye recouvert de SOD apres recuit de 5min. a

245°C (a) et apres un deuxieme recuit de 5min. a 245°C (b) 81

Figure D.l Representation graphique des regies de dessin d'un transistor (W/L de 100/10)

LISTE DES TABLEAUX

Tableau 3.1 Resume des structures developpees sur JOPE avec leurs descriptions et les

resultats 20

Tableau 4.1 Modele SPICE 36

Tableau 4.2 Resume des structures de la puce A 40

Tableau 4.3 Sommaire des resultats de tensions de seuil visees et mesurees 42

Tableau 4.4 Dose et energie d'implantation d'ajustement VT 43

Tableau 4.5 Modulation de la longueur de canal e x p e r i m e n t a l 44

Tableau 4.6 Resume de la densite de charge d'interface mesuree 48

Tableau 4.7 Comparaison de la resistance de couche des materiaux pour JOPE et JOPE2 58

Tableau 4.8 Comparaison de la resistivite des contacts entre JOPE et JOPE2 59

Tableau 4.9 Rendement des chames de contacts 62

Tableau 4.10 Resultats des mesures statistiques de defauts des resistances en serpentins 63

Tableau 4.11 Resultats des mesures statistiques de defauts des resistances en peignes.... 63

Tableau B.l Resultats de 1'evaluation du recuit RTA 86

Tableau B.2 Resultats de 1'evaluation du recuit en fournaise pour le SOD en comparaison

avec I'implantation ionique 87

LEXIQUE

Cellule : En electronique, une cellule est un « [...] element de base effectuant differentes fonctions elementaires ou plus complexes de logique ou d'arithmetique [...] » [15].

CMOS : Terme provenant de I'anglais, complementary metal oxide semiconductor, designant une technologie de fabrication de circuits de microelectronique integrant des transistors NMOS et PMOS sur un meme substrat.

JOPE : Nom designant les circuits et le procede de fabrication NMOS developpe au cours des annees 80 par des collaborateurs francais. Le nom provient des noms de famille des conceptrices, Jouanny et Perrin. Le procede et les circuits sont decrits dans [7].

JOPE2 : Nom designant les circuits et le procede de fabrication utilise au cours de ce projet dans le but de concevoir des circuits complexes a 2 u.m. Le developpement de ce procede est base sur JOPE.

Mesure CV : Technique de mesure utilisee pour caracteriser les condensateurs MOS qui consiste a mesurer la capacite en fonction d'une rampe de tension continue sur lequel est modulee une sinusoi'de typiquement de 10 mV crete a 1 MHz.

M e t a l l : Indique la couche d'aluminium du procede JOPE et JOPE2, qui sert d'interconnexion.

Nettoyage RCA : Procedure de nettoyage standard des tranches de silicium developpe dans les annees 60 dans les laboratoires de la compagnie Radio Corporation of America. La procedure consiste a nettoyer les contaminants organiques, graver la couche d'oxyde native et de nettoyer les contaminants ioniques [35].

P o l y l : Indique la couche de polySi de JOPE et JOPE2 servant de grille et de couche superieure des condensateurs PIP du procede de fabrication recommande suite aux resultats des travaux (voir section 5.2).

Poly2 : Indique la seconde couche de polySi de JOPE et JOPE2 servant a la couche inferieure des condensateurs PIP du procede de fabrication recommande suite aux resultats des travaux (voir section 5.2).

PolySi: Signifie silicium polycristallin, ou polysilicium.

Rendement: En electronique, le rendement est le « rapport entre le nombre de circuits utilisables a la fin du procede de fabrication et le nombre total de circuits initialement soumis au procede de fabrication » [15].

Resistance de couche : « Resistance entre deux cotes d'un carre imaginaire d'une region diffusee ou d'une couche mince »[15]. En anglais, on I'appelle sheet resistance.

Saliciure : Terme provenant de I'anglais salicide pour self-aligned silicide, ce qui se traduit par siliciure autoaligne, qui designe une technique permettant de contacter une couche d'interconnexion a un alliage de silicium et d'un metal tel que le titane.

Tolerance : En statistique, la tolerance est la « valeur limite specifiee d'un caractere mesurable et qui, par exemple en matiere de controle de la qualite, amene le rejet d'un certain nombre d'articles et I'acceptation des autres » [15]. La tolerance s'exprime en pourcentage (%). Pour le cas des resistances, m u l t i p l i e s par la valeur nominale de la resistance, la tolerance indique la variation acceptable de la resistance en 0.

LISTE DES SYMBOLES

d : Capacite de grille (F/cm2).

Cox: Capacite de I'oxyde de grille des transistors MOSFET (F).

gm : Transconductance (O1)

Kn: Parametre de technologie, transconductance (gm(sat)) divise par VD (A/V2).

Q : Charge effective totale a I'interface Si/Si02de transistors MOSFET par unite de surface (qC/cm2).

QOT : Charge piegee dans I'oxyde de grille de transistors MOSFET par unite de surface (qC/cm2).

QM : Charge mobile dans I'oxyde de grille de transistors MOSFET par unite de surface (qC/cm2).

Qi,: Charge a I'interface Si/Si02de transistors MOSFET par unite de surface (qC/cm2).

QF: Charge fixe presente a I'interface Si/Si02de transistors MOSFET par unite de surface (qC/cm2).

Na: Densite de porteurs dans le substrat (cm3)

Ra: Resistance de couche d'un materiau (0.D).

RDS: Resistance drain-source equivalente des MOSFET (0.).

To x: Epaisseur de I'oxyde de grille (Oxide Thickness) (nm).

VT : Tension de seuil des MOSFET (Threshold Voltage) (V).

W/L : Ratio de la largeur sur la longueur de griile d'un MOSFET.

A.: Modulation de la longueur de canal (V1).

p : Resistivite (O-cm).

LISTE DES ACRONYMES

AOE : Advanced Oxide Etch, pour gravure d'oxyde avancee par plasma

ASE : Advanced Silicon Etch, pour gravure de silicium avancee par plasma

APP : Apprentissage par problemes et par projets

ASIC : Application Specific Integrated Circuit, pour circuit integre pour application specifique

BOE : Buffered Oxide Etch, pour gravure d'oxyde

CRN2: Centre de recherche en nanofabrication et nanocaracterisation

DIBL :Drain-lnduced Barrier Lowering, pour abaissement de barriere induit par le drain

DRAM : Dynamic Random Memory Access, pour memoire vive dynamique

FET : Field Effect Transistor, pour transistor a effet de champ

LDD : Ligthly Doped Drain, pour drain a faible dopage

ITRS : International Technology Roadmap for Semiconductors

LOCOS : LOCal Oxidation of Silicon, pour oxydation locale du silicium

LPCVD : Low-pressure Chemical vapor deposition, pour depot chimique en phase vapeur realisee a pression sous-atmospherique

M l : Metall

MEMS : Micro-Electro-Mechanical Systems, pour microsysteme electromecanique

MOSFET : Metal Oxyde Semiconductor FET, pour FET metal-oxyde-semiconducteur

MPU : Manycore Processing Unit, pour microprocesseur multi-cceurs

NMOS : n-Channel MOSFET, pour MOSFET a canal N

P I : Polyl (de facon similaire P2 signifie Poly2)

PECVD : Plasma-enhanced chemical vapor deposition, pour depot chimique en phase vapeur assiste par plasma

PIP : Condensateur po/yS/-/so/ant-po/yS/

PMOS : p-Channel MOSFET, pour MOSFET a canal P

PSG : Phosphorus doped Silica Glass, pour dioxyde de silicium dope de phosphore

PVD : Physical Vapor Deposition, pour depot physique en phase vapeur

RTA : Rapid Thermal Anneal, pour recuit thermique rapide.

RTR : Rail-to-Rail, pour plage dynamique couvrant I'etendu de I'alimentation

SOD : Spin on Dopant, pour dopage par diffusion d'une source liquide

TSMC : Taiwan Semiconductor Manufacturing Company

USG :Undoped-Silicate Glass, pour verre constitue de silice (Si02) non dope

VLSI: Very Large Scale Integration, pour integration a tres grande echelle

CHAPITRE 1 INTRODUCTION

1.1 Mise en contexte

Le silicium est le principal materiau utilise par I'industrie pour la fabrication de circuits microelectroniques. II est le materiau de choix pour ses proprietes physiques. Compare a d'autres materiaux semi-conducteurs, le silicium est facile a utiliser, a une bonne qualite d'oxyde, il est abondant, peu couteux et est tres bien maTtrise par I'industrie de la microelectronique [27]. Essentiellement, sur silicium on utilise essentiellement la technologie CMOS pour realiser des fonctions logiques et analogiques.

Partant de ce fait, I'industrie d'aujourd'hui a besoin d'integrer des biocapteurs et des MEMS directement sur les circuits CMOS pour le conditionnement de signaux qui permettent une recrudescence des fonctionnalites des systemes tout en les rendant plus autonomes. De plus, il est important pour I'industrie que les composants a fabriquer soient compatibles avec la technologie CMOS afin de limiter les changements au sein de leurs infrastructures de production, diminuant ainsi les couts et les risques de compromettre la stabilite de leurs procedes. Pour les laboratoires de recherche, il est done de plus en plus benefique d'etre en mesure de prouver la compatibility des capteurs et des systemes MEMS avec une technologie CMOS. Ceci permet aux industries d'integrer plus aisement de nouveaux composants developpes dans le cadre de projet de recherche a leurs infrastructures de fabrication.

Le CRN2 de YUniversite de Sherbrooke n'a pas de procede CMOS ni de technologie NMOS stable qui puisse etre fabriquee a I'interieur des laboratoires du centre. Ceci implique qu'il est difficile pour les chercheurs d'integrer leurs decouvertes a ces technologies. En effet, la technologie NMOS JOPE a six masques disponible au centre permet de fabriquer des dispositifs de grande taille possedant une stabilite precaire. Une version simplified du procede de fabrication a quatre masques de cette technologie est presentement utilisee a des fins pedagogiques pour les cours Techniques de

fabrication en salles blanches (GEI718) du programme de baccalaureat et de maTtrise en genie

electrique de YUniversite de Sherbrooke. Le procede est utilise principalement pour I'enseignement des techniques de fabrication et de caracterisation de composants de bases, tels que des condensateurs MOS et des transistors NMOS.

Cependant, ce procede n'est pas stable puisque les performances des dispositifs fabriques different d'une puce a I'autre, d'une tranche a I'autre et d'un lot a I'autre. Ce comportement est du a la tolerance de la resistivite des tranches utilisees, aux proprietes du polySi formant les grilles ainsi qu'a la qualite d'oxyde de grille des transistors. Ces parties du MOSFET sont cruciales puisqu'ils affectent les caracteristiques fondamentales des transistors fabriques, tels que la tension de seuil {VT) ainsi que

la capacite de grille (C,). Cette instability donne lieu a une variation aleatoire des transistors qui resulte en un procede n'etant pas optimal pour la conception de circuits complexes oil plusieurs transistors sont impliques. Cette technologie NMOS n'est done utilisee seulement qu'a titre pedagogique dans le but de caracteriser des transistors individuels.

Posseder une filiere NMOS stable pouvant etre fabriquee dans les installations du CRN2 de YUniversite

de Sherbrooke permettrait au departement de genie electrique et de genie informatique d'utiliser le

procede a des fins pedagogiques plus etendues. A titre d'exemple, des cellules complexes pourraient etre caracterisees pour enseigner des cours comme Physique des semi-conducteurs II (GEL311),

Electronique analogique II (GEL320) ou Conception avancee de circuits integres (GEI710). II pourrait de

meme etre possible d'enseigner un cours tel qo'Elements de statistique (GEL350), s'il est possible de caracteriser plusieurs puces fabriquees au CRN2 et ainsi prendre des mesures statistiques de defauts. Le programme de genie electrique et de genie informatique de YUniversite de Sherbrooke se prete bien a ^integration d'elements pratiques a I'enseignement puisqu'il utilise une approche pedagogique d'apprentissage par projets (APP). Cette approche implantee au departement en 2001 permet aux etudiants d'acquerir leurs connaissances tout au long du baccalaureat par la resolution de problemes pratiques et par la realisation de projets concrets.

Avoir une filiere NMOS stable est une etape essentielle dans I'etablissement au sein du CRN2 d'une eventuelle filiere CMOS. En effet, fabriquer des transistors NMOS fiables est une etape preliminaire essentielle pour fabriquer des circuits CMOS fiables, qui sont constitues de transistors NMOS et PMOS. Un procede de fabrication CMOS pourrait etre developpe a partir d'une technologie NMOS en ajoutant entre autres les etapes pour I'implantation de puits N ainsi que les etapes pour I'implantation de drains-sources de type P. La fabrication de cellules CMOS complexe permettrait aux chercheurs de YUniversite de Sherbrooke d'avoir la possibility de fabriquer a faibles couts des circuits destines a des applications specifiques. Par exemple, elle permettrait la fabrication de microbiocapteurs a meme des puces CMOS.

Introduction 3

Geci nous amene a nous poser la question :

« Est-ce que la technologie NMOS dont dispose le CRN2 (JOPE) peut etre utilisee pour integrer une plus

grande densite de cellules defacon stable, a desfins pedagogiques et de recherches, permettant ainsi le developpement d'une technologie CMOS future? »

1.2 Objectifs

La finalite de ce projet est I'etablissement du procede NMOS au sein du CRN2. Pour atteindre ce but, plusieurs sous-objectifs sont prevus :

• Evaluer la stabilite du procede afin d'integrer une plus grande densite de cellules en diminuant la

taille des composantes. II faut identifier les causes d'une possible instability afin de reviser le

procede pour en ameliorer la stabilite. Un rendement de 85 % est vise pour la technologie. A titre d'exemple, selon I'lTRS, en 2007 [21], I'industrie visait une augmentation du rendement de puce pour passer de 83 a 89.5 % d'ici 2016 pour les MPU, les ASIC et les DRAM. Dans le cadre de ce projet, cet objectif de 85 % est raisonnable a comparer de ceux de I'industrie dans la mesure ou les circuits produits par celle-ci necessitent jusqu'a 37 masques et sont fabriques sur des tranches allant jusqu'a 300 mm. La technologie visee dans ce document necessite 6 masques et est fabriquee sur des tranches de 76 mm. En outre, les equipements utilises au CRN2 ne sont pas dedies au procede et done pas optimises pour celui-ci. L'environnement de fabrication est ainsi soumis a differents materiaux tels que du mercure, de I'or et du cuivre qui diffusent dans le silicium et peuvent causer des pieges profond. Ceci laisse envisager une diminution du rendement. • Verifier la possibilite d'utiliser le Polyl comme couche d'interconnexion complementaire a

1'aluminium1. Deux couches d'interconnexion sont essentielles afin de permettre d'acheminer les

signaux dans des circuits complexes comprenant plusieurs transistors.

• Developper un modele SPICE de la technologie pour la simulation. Ceci est un outil essentiel pour la conception de circuits complexes.

• Definir des contraintes de conceptions ainsi que des regies de dessins des masques et lesfoumir au

CRN2 afin de permettre I'utilisation du procede a plus grande echelle.

Cette pratique etait couramment utilisee dans les annees 70 avant I'avenue de multiples couches d'interconnexions metalliques.

• Developper des circuits de caracterisation du procede afin de les utiliser dans un cadre

pedagogique.

1.3 Methodologie

Plusieurs actions ont ete mises de I'avant afin d'atteindre la finalite decrite a la section 1.2. Les sections suivantes presentent les differentes etapes realisees pour accomplir le projet.

1.3.1 Stabilisation de la technologie

Afin de permettre la fabrication d'une plus grande densite de composant NMOS, il faut diminuer la taille des composantes. Pour ce faire, la technologie doit etre stabilisee. En d'autres mots, il faut comprendre et maTtriser les differentes etapes du procede pour permettre la fabrication de transistors de taille plus faible tout en ayant un rendement acceptable de 85 %.

Caracteriser JOPE

Pour atteindre cet objectif, des circuits fabriques dans les annees anterieures selon le procede JOPE ont ete caracterises. Les premiers parametres evalues sont la resistivite, I'epaisseur, la grosseur de grain et le dopage de la couche de Polyl. II est essentiel de faire une telle evaluation afin d'apporter les corrections necessaires pour utiliser la couche de Polyl comme interconnexions.

Ensuite, I'oxyde de grille a du etre evalue, car c'est la partie la plus sensible et la plus critique des MOSFET. L'epaisseur d'oxyde de grille ainsi que la charge d'interface Q, influencent de facon significative VT. Dans le meme ordre d'idee, la variation de la tension de seuil AVTa ete ainsi evaluee

theoriquement en fonction de I'epaisseur de I'oxyde de grille, de la resistivite du substrat de depart, du dopage du polySi et de Q,.

Des transistors fabriques selon JOPE ont ete egalement caracterises afin de determiner les parametres fondamentaux tels que VT, KN, A, RDSl T0x et Na, pour developper un modele SPICE,

essentiel pour la conception de cellules complexes.

Conception, fabrication et caracterisation de JOPE2

Des puces ont ete concues pour creer JOPE2, ces dernieres ont une densite plus importante de composantes que JOPE. Ceci a pour but d'evaluer la performance des MOSFET dans de telles

Introduction 5

conditions. Pour y arriver, des regies de dessins ont ete fixees, comme la longueur de grille minimale a 2 u.m, la largeur et I'espacement des lignes d'interconnexion a 2 u.m. Des circuits de caracterisation ainsi que des cellules analogiques et numeriques ont ete concus afin de caracteriser le procede et de calculer le rendement.

Les 6 masques ont ete fabriques avec un phototraceur DWL 66 System, les 3 premiers sur des substrats de 102 mm et les 3 derniers sur des substrats de 127 mm. Ceci a permis de comparer deux aligneuses, les tranches ont ete alignees avec une OAI 200 sur les masques de 102 mm et avec une OAI 806MBA sur les masques de 127 mm.

La fabrication du procede a ete lancee initialement sur 9 tranches de 76 mm de type P (1-10 Q-cm) (echantillon A a I). Plusieurs problemes sont survenus pendant la fabrication, ce qui fait que 5 tranches (A, B, D, E et G) ont vue la fin du procede. Trois tranches ont eclate et une autre a subi une erreur majeure de fabrication. Le procede de fabrication utilise pour JOPE2 a ete modifie selon les resultats obtenus lors de la caracterisation de JOPE. Plusieurs etapes varient en fonction des tranches dans le but de definir les parametres optimaux de fabrication. La structure du plan de fabrication du prototype est presentee a la figure 4 . 1 .

Une fois la fabrication terminee, les tranches ont ete rigoureusement caracterisees pour definir le rendement du procede. Le rendement est evalue en termes de fiabilite des contacts, d'alignement des masques et de densite de defauts. Plusieurs autres parametres ont ete egalement determines tels que les parametres fondamentaux des transistors, la resistance des contacts, la resistance de couche des materiaux et le taux de surgravure des couches.

CHAPITRE 2 ETAT DE L'ART

Dans cette section, le projet sera situe par rapport a revolution de la microelectronique. Tout d'abord, I'histoire du NMOS sera abordee a partir de ses debuts. Differents procedes NMOS et CMOS utilises a titre pedagogique seront ensuite enumeres. Egalement, les impacts de la reduction des dimensions sur les proprietes physiques des transistors a effet de champ seront decris. Finalement, les principales techniques de fabrications en salle-blanche adaptes a la fabrication de MOSFET seront traitees.

2.1 Les debuts du NMOS

La technologie NMOS a ete utilisee par les premiers microprocesseurs a etre commercialises notamment, le 8008 6'lntel en 1974 et peu apres durant la meme annee, la serie 6800 de Motorola. Ces processeurs ont d'ailleurs ete utilises dans les populaires consoles Atari et Commodore 64. On verra apparaTtre differentes topologies de microprocesseurs basees sur cette technologie dans les annees qui suivirent [39, 46]. Plusieurs amplificateurs operationnels ont egalement ete developpes durant ces annees [14, 38, 48, 53], de meme que de la memoire RAM [29]. Ainsi, I'industrie de la microelectronique a utilise la technologie NMOS pour des circuits numeriques et analogiques jusqu'au debut des annees 80 pour ensuite la remplacer par le CMOS.

En recherche, cette technologie est encore utilisee aujourd'hui puisqu'elle est tres flexible, facile a fabriquer et peu couteuse. A titre d'exemple, le procede le plus abordable offert par CMC

Microsystems est le CMOSP8E de Dalsa Semiconducteur a 0.8 u.m de longueur de grille. Pour un

groupe de recherche universitaire, faire fabriquer une puce de 76 mm2 de cette technologie, dimensions semblables aux puces de JOPE2, coute 3600$ et est livree en 7 mois. A condition de fabriquer plusieurs tranches a la fois, une tranche de 76 mm de JOPE (~4500 mm2) coute environ 1000 $ et peut-etre fabriquee en 2 mois, ce qui plus rapide et moins couteux que les procedes offerts par CMC Microsystems. De plus, JOPE offre une plus grande flexibilite en mettant a disposition tous les parametres de fabrication et en permettant au concepteur de modifier certains de ces parametres tels que I'epaisseur d'oxyde de grille et les implantations source/drain et d'ajustement de la tension de seuil.

L'industrie quant a elle s'est tournee vers la technologie CMOS, qui est dite complementaire puisqu'elle utilise a la fois des MOSFET a canal N et P (NMOS et PMOS) sur une meme puce, done sur un meme substrat. Cette technologie necessite done un procede de fabrication plus complexe puisqu'il faut ajouter des puits N ou P. Cependant, plusieurs avantages sont relies au CMOS. Pour les circuits analogiques, le CMOS permet entre autres de pratiquement atteindre les tensions d'alimentation (rail to rail ou RTR) a I'entree et a la sortie des amplificateurs operationnels. A leurs sorties, on parvient a atteindre pratiquement le RTR en utilisant un etage d'amplification AB CMOS en mode source commune, opere en moyenne inversion de population [52]. Le CMOS permet d'avoir une symetrie presque parfaite et de reduire grandement le courant de repos. Meme si des topologies d'amplificateur AB NMOS ont ete proposees pour reduire le courant de repos [16], il reste difficile d'atteindre le RTR du notamment a I'asymetrie de la reponse. Pour le RTR a I'entree, la technique la plus simple est une double paire differentielle NMOS et PMOS en parallele [20]. Dans cette configuration, la paire differentielle PMOS est operationnelle pour des tensions d'entrees en mode commun de VSS a une tension superieure a VDD/2 et la paire differentielle NMOS est operationnelle pour des tensions d'entrees en mode commun inferieur a VDD/2 jusqu'a VDD. En technologie NMOS, on peut obtenir des resultats semblables avec une paire differentielle NMOS a grille flottante ou en operant une paire NMOS par le substrat [52], ce qui n'est pas possible a implanter avec toutes les technologies NMOS, notamment la technologie JOPE.

En electronique numerique, le gain de la technologie CMOS est encore plus clair. Par exemple, pour un inverseur logique NMOS comme celui presente a la figure 2.1(b), il y aura une consommation electrique non negligeable des transistors M l et M2 lorsque le niveau logique de la sortie sera a niveau bas du a la charge active M l . A ce moment, la sortie ne pourra etre exactement VSS. Pour I'inverseur logique CMOS presente a la figure 2.1(a), on constate qu'il n'aura consommation electrique que pendant un changement d'etat, ou M l et M2 conduiront en meme temps. Par exemple, en electronique numerique la technologie CMOS apporte un gain significatif au niveau de la consommation electrique qui a ete un pilier tres important pour l'industrie qui demande une densite de transistors en constante evolution, suivant la loi de Moore [21].

Etat de I'art 9 V e o 4 (a) VDD

?

M1 —OVs M2 V e^ >1

(b) VDD9

J

M1 -OVs VSS M26

VSSFigure 2.1. Comparaison d'un inverseur logique CMOS en (a) et NMOS en (b)

2.2 Procedes NMOS utilises a titre pedagogique

Comme YUniversite de Sherbrooke, plusieurs autres centres d'enseignement utilisent encore aujourd'hui des circuits NMOS dedies a i'enseignement de la fabrication et de la caracterisation de la microelectronique [23, 30].

L'enseignement de procedes de fabrication au niveau du baccalaureat permet aux etudiants d'etre confronted a la fabrication de microelectronique avant leur choix de carriere. Ceci leur donne la possibility d'entreprendre une carriere en fabrication VLSI, en simulation, caracterisation, conception, modelisation, etc. Les etudiants sont generalement satisfaits de ce type de cours puisqu'ils eveillent la curiosite de comprendre des circuits integres plus complexes. Les etudiants seront egalement mieux prepares s'ils entreprennent des etudes superieures dans le domaine de la microelectronique.

Par exemple, la Virginia Polytechnic Institute and State University aux Etats-Unis ont developpe un procede NMOS a quatre couches permettant de fabriquer des jonctions PN, des MOSFET a canal N, des condensateurs et des resistances [45]. Avec ce procede, les etudiants peuvent faire la caracterisation de la fabrication par des mesures de resistivites de chaque couche et peuvent egalement caracteriser les composants actifs (MOSFET et diodes). De plus, les etudiants peuvent concevoir leurs propres masques de fabrication grace a une technique de fabrication de masque peu couteuse utilisant une imprimante haute definition Alps Microdry™. Cette technique permet une regie de dessins minimale de 100 p.m. Cette technique a I'avantage d'enseigner aux etudiants le developpement de masques de fabrication en plus de la caracterisation. Une autre particularity

interessante de ce procede est la haute qualite et la faible epaisseur de I'oxyde de grille (40 nm) qui est crue par oxydation seche. Cette faible epaisseur du dioxyde de silicium (Si02) avec la grande dimension de grille permet d'avoir une capacite de grille tres elevee. Ceci permet un bon controle de canal mais un courant de fuite eleve et une frequence de coupure faible. Aussi, la grande dimension des transistors rend le procede inadapte pour la fabrication de cellules complexes a haute densite.

Un procede NMOS a 2 masques et 3 photolithographies est presente par Parent en 2007 [33]. Comme il est montre a la figure 2.2, ce procede a ete simplifie en mettant I'oxyde de champ sur la meme couche que I'oxyde de grille. De plus, aucun masque d'isolation n'est utilise et la grille est faite d'aluminium tout comme les interconnexions, par une seule photolithographie. Finalement, le meme masque est utilise pour la photolithographie servant a la diffusion des sources/drains par Spin on

Glass (SOG) et la photolithographie servant a I'ouverture des contacts.

Offset

Figure 2.2. Vue du dessus (masques) et en coupe d'un transistor [33]

D'un point de vue pedagogique, avoir peu de masques de fabrication permet de reduire le cout et le temps de fabrication de circuits. Le procede a deux couches presente par Parent [33] est utilise pour I'enseignement ou les etudiants concoivent, simulent, fabriquent et caracterisent leurs propres circuits. Les etudiants peuvent souvent reprendre les erreurs commises lors de la fabrication puisque le procede est simple, ce qui permet d'augmenter le rendement des circuits fabriques.

Etatdel'art

11

2.3 Procedes CMOS utilises aujourd'hui

2.3.1 Utilisation en enseignement

La technologie NMOS JOPE disponible au CRN2 necessite 6 masques et 21 etapes de fabrication. Une technologie standard CMOS simple necessite au moins 13 masques de fabrication afin de creer les puits N sur un substrat P [4]. Une technologie industrielle telle que CMOSP35 de TSMC, avec une resolution de 350 nm, necessite 23 masques de fabrication. Cette derniere possede 2 couches de polySi et 4 couches metalliques d'interconnexions.

On retrouve dans la litterature plusieurs technologies CMOS qui sont utilisees a titre pedagogique. Entre autres, on retrouve un circuit de technologie CMOS 0.35 urn, pour enseigner le VLSI analogique [31]. Ce projet presente la fabrication d'une puce contenant 18 bornes d'interconnexions permettant de configurer deux circuits distincts; un circuit contenant des miroirs de courant en cascade et un etage d'entrees differentielles. Les etudiants peuvent done configurer et mesurer plusieurs circuits analogiques simples, lis peuvent ainsi comprendre les modes d'operations des circuits analogiques. Cependant, I'objectif de ce projet n'est pas I'enseignement de methodes de fabrication puisque les etudiants ne concoivent ni ne fabriquent les puces dues a la complexity du procede.

2.3.2 Utilisation en industrie

Quoiqu'/nte/ sorte en 2010 sa technologie 32 nm pour leur nouvelle serie de microprocesseurs, des technologies CMOS de 0.8 a 5 urn sont toujours utilisees de nos jours. En effet, pour des raisons de faibles couts et de robustesse, ces technologies sont utilisees encore aujourd'hui dans les domaines de I'automobile, I'aerospatial et la medecine, ou la fiabilite est un enjeu critique. A titre d'exemple,

Dalsa offre le procede de 2 u.m C20G ainsi que Seme Fab offre des procedes 2 et 3 u,m. Ces

technologies ont une plus grande capacite de dissipation thermique et operent a des tensions plus elevees ce qui les rendent moins sensible au bruit. Pour ces raisons, elles ont necessairement une meilleure fiabilite que les technologies submicroniques plus recentes.

2.4 Impacts de la reduction des dimensions

Puisque ce projet necessite de reduire les dimensions des structures fabriquees par la technologie existante JOPE, il est necessaire de prendre en consideration les phenomenes physiques qui surviennent.

Tout d'abord, il est important de mentionner que le dimensionnement des composantes actives doit se faire autant dans le plan de la tranche (axes X et / ) qu'en profondeur (axe Z). En d'autres termes, si on desire reduire la geometrie d'un transistor en termes de longueur et de largeur (axes X et Y), il est necessaire de reduire en consequence I'epaisseur d'oxyde de grille et la profondeur des jonctions source/drain (axe Z).

En diminuant les dimensions des transistors, on doit s'attendre d'abord a voir les tensions de claquage diminuer2 et par le fait meme les tensions d'operation. En effet, la distance qui separe le drain et la source diminue, ce qui augmente le champ electrique dans le canal et done I'energie cinetique des porteurs. Pour les NMOS, les electrons deviennent tres energetiques et ils sont alors appeles electrons chauds. Certains de ces electrons traverseront I'oxyde de grille, ce qui a pour effet d'induire un courant de grille. Les electrons chauds peuvent egalement etre pieges dans I'oxyde, ce qui a pour effet d'augmenter VT. Finalement, ces electrons peuvent briser des liens Si-H a I'interface

Si-Si02, ce qui degrade de facons permanentes la transconductance des transistors. Pour reduire cet effet negatif, on dope plus faiblement le drain et la source pres de la grille. Cette technique, appelee

Lightly Doped Drain (LDD), permet de reduire le champ electrique dans la region de pincement pour

reduire I'acceleration des porteurs. De plus, la diminution de I'epaisseur d'oxyde de grille engendre une augmentation du champ electrique de I'oxyde ce qui cause une diminution de la tension de claquage de la grille et une augmentation du courant de fuite de grille.

Cependant, il y a plusieurs points benefiques a diminuer les dimensions des transistors FETcomme I'augmentation de la vitesse de commutation due a une diminution de C0x et la diminution de la

consommation electrique. Neanmoins, la densite de composante plus elevee cause une augmentation de la puissance dissipee des microprocesseurs plus recents.

Etat de I'art 13

2.5 Techniques de fabrication

Plusieurs methodes de fabrications sont utilisees pour produire des MOSFET. Cette section sert a presenter ces differentes techniques ainsi que celles utilisees dans ce projet.

2.5.1 Dopage

Le dopage consiste a injecter dans un materiau semi-conducteur des impuretes choisies afin d'ajouter des porteurs. II existe principalement trois methodes pour injecter localement une densite de porteurs, 1'implantation ionique, la diffusion et le Spin on Dopant (SOD). Chacune d'elles a des avantages et des inconvenients.

Implantation ionique

La technique consiste a accelerer des ions dans une chambre a vide pour qu'ils frappent et penetrent la tranche de silicium. Cette technique est utilisee par JOPE pour doper le polySi, les sources/drains pour I'isolation electrique des NMOS ainsi que le dopage d'ajustement de VT. L'implantation ionique

peut etre masquee par une couche de Si02. Elle permet de doper avec une profondeur desiree en ajustant I'energie pour creer un profil d'implantation precis, cette technique est done tres flexible. Cependant, les ions crees des defauts en frappant la structure cristalline, ces defauts sont reduits par un recuit d'activation des porteurs.

Diffusion

Le dopage par diffusion est tres utilise en industrie puisque e'est une methode efficace pour doper plusieurs tranches en meme temps. La technique consiste a alterner des tranches a doper, masque par du Si02, avec des tranches agissant comme source solide de dopant, par exemple du P205. En reglant la temperature de la fournaise entre 900 a 1200°C, le phosphore entre alors en phase gazeuse et diffuse dans les tranches. Le principal avantage de la methode est qu'aucun defaut dans la structure cristalline n'est produit par le procede. De plus, la diffusion permet d'avoir un profil de dopage uniforme et elle permet de doper plusieurs tranches simultanement. Par contre, elle ne permet pas de concentrer les porteurs a une profondeur precise.

Spin on Dopant

Cette methode consiste a etaler sur la tranche un film dopant, tel que le Phosphorosilicafilm de

Emulsitone. Ensuite, avec un recuit thermique, le dopant diffuse dans la tranche. II est possible de

faire un dopage localise avec un masque de Undoped-Silicate Glass (USG) [32]. Cette technique de dopage est simple, rapide et peu couteuse et ne creee pas de defaut dans la structure cristalline. Cependant, comme la diffusion en fournaise, cette technique ne permet pas de concentrer les porteurs a une profondeur precise. Plus de details sur ce procede de fabrication sont disponibles a I'annexe B.

2.5.2 Recuit d'activation des porteurs

Pour le procede JOPE, suite aux differentes implantations, un recuit thermique est fait en fournaise pour activer les porteurs et reparer la structure cristalline. Comme ce recuit se fait a temperature elevee (950°C), il y a egalement diffusion des porteurs. La diffusion des porteurs est souvent non desiree dans les procedes ou plusieurs implantations doivent etre faites. La diffusion peut etre reduite par un recuit rapide, RTA. La temperature de ce type de four peut augmenter tres rapidement, souvent avec I'aide de lampes tres puissantes ce qui permet de faire un recuit d'activation en quelques secondes et ainsi reduire la diffusion des porteurs.

2.5.3 Gravure du SiCh

Des formes peuvent etre definies dans le dioxyde de silicium par gravure humide ou seche. La gravure humide consiste a immerger les tranches a graver, masquee avec de la resine (S1813 pour JOPE et JOPE2), au Buffered Oxide Etch (BOE) (un melange NH4F:HF). Quoiqu'il soit deja prepare avec des proportions tres exactes, pour avoir un taux de gravure precis et repetable, la solution doit etre chauffee a 26°C de facon manuelle. Le desavantage de cette technique est que la gravure est isotrope et que le taux de gravure depend fortement de la temperature. Une petite variation de temperature peut engendrer des problemes d'uniformite surtout quand les structures a graver sont fines. Egalement, les tranches peuvent etre agitees pour augmenter le taux de gravure. Ceci peut causer un probleme d'uniformite lorsque I'agitation est faite manuellement. Par contre, la gravure humide est simple et rapide, c'est pourquoi elle est utilisee dans JOPE et JOPE2 afin d'ouvrir les regions actives et les contacts.

Etat de I'art 15

La gravure seche par plasma, appele AOE, est anisotrope et se fait quant a elle par plasma. Cette technique offre une grande stability surtout pour la gravure d'une grande densite de structures etroites.

Gravure des contacts

Pour s'assurer que la couche d'interconnexions ne soit pas discontinue a I'interieur des contacts, la pente des contacts doit etre douce, comme il est represente a la figure 2.3. Ceci ne cause generalement pas de probleme pour une gravure humide, comme c'est le cas pour JOPE et JOPE2. La raideur de la pente pose problemes pour les contacts graves par AOE. La gravure anisotrope des contacts par plasma est utilisee en industrie generalement lorsque le diametre du contact est egal ou plus petit que sa profondeur. Dans le cas contraire, une gravure humide/seche est utilisee. En d'autres mots, il s'agit d'une gravure humide isotrope partielle, qui est terminee par une gravure seche, ce qui permet d'adoucir la pente du contact [49]. Pour des contacts submicronique, la gravure humide est remplacee par une gravure isotrope seche pour un plus grand controle [43].

t

d

tjgj B M e t a l l (Aluminium)

L ^ ^ ^ ^ ^ ^ HOxyde deposee

! i ISubstrat

Figure 2.3 Vue en coupe de deux contacts de diametre plus petit que I'epaisseur de I'oxyde (d<e) pour une gravure anisotrope (a) et isotrope (b)

2.5.4 Gravure du Polyl et Metall

Tout comme pour le Si02, les couches de polySi et d'aluminium peuvent etre gravees en solution aqueuse (gravure humide) ou par plasma (gravure seche). La gravure seche offre un meilleur controle des dimensions. Pour JOPE, ces deux couches sont gravees en solution aqueuse, qui est un processus rapide et peu couteux.

Pour JOPE2 cependant, puisque les longueurs de grilles ont grandement diminue par rapport a JOPE, le Polyl est grave par plasma (ASE) ce qui offre un meilleur controle et une bonne reproductibilite. La couche d'aluminium est une etape beaucoup moins critique pour les dispositifs puisqu'elle sert d'interconnexions. Pour cette raison, la definition des interconnexions est faite par gravure humide pourJOPE2.

2.5.5 Deposition d'aluminium

Au CRN2, I'aluminium peut etre depose par evaporation et par pulverisation (PVD). Pour notre cas, les deux methodes se ressemblent outre que I'evaporation est un procede plus lent. La pulverisation quant a elle peut generer des defauts sur la couche deposee mais permet la deposition d'une couche plus epaisse.

Sur JOPE et JOPE2 la couche d'aluminium est deposee par evaporation puisque I'epaisseur de la couche est suffisamment mince. II pourrait etre une bonne pratique de deposer I'aluminium par evaporation et de deposer une couche plus epaisse afin de diminuer la resistance de couche et reduire I'apparition de defauts.

2.5.6 Saliciure

Lorsque les contacts du Metall/zone active (Ml/ZA) ont une dimension submicronique, la resistivite des contacts augmente radicalement. Pour contrer ce probleme, une des techniques utilisees consiste a reduire la resistivite a I'aide d'une couche de saliciure, qui est du siliciure autoaligne {salicide). Pour y arriver, une couche de cobalt ou de titane est deposee sur les regions a contacter et ensuite un recuit est fait. Une couche de siliciure est formee par I'alliage du metal et du silicium. Le metal n'ayant pas diffuse peut etre grave par une solution qui attaque selectivement le metal par rapport au siliciure, c'est pourquoi cette methode est appelee du siliciure autoaligne. Cette procedure permet ensuite de deposer la couche de metal servant aux interconnexions, et de reduire considerablement les resistances de contacts [35, 41].

CHAPITRE 3 PROCEDE DE FABRICATION

JOPE designe le procede de fabrication ainsi que les circuits sur lesquels ce projet est base [7]. Lesmasques de fabrication de ces circuits sont disponibles au CRN2. Ainsi, plusieurs tranches ont pu etre fabriquees. Ce chapitre presente done en detail I'analyse du procede de fabrication JOPE ainsi que les modifications qui y sont apportees. Ces changements apportes au procede ont pour objectifs de creer le procede JOPE2 afin de confirmer s'il est possible de creer des circuits complexes.

3.1 JOPE

Le procede est base sur 6 masques permettant de fabriquer des transistors a enrichissement et a appauvrissement. Le procede utilise une grille autoalignee, e'est-a-dire que les sources/drains sont implantes en meme temps que les grilles de polySi. De plus; une implantation d'isolation est disponible pour separer electriquement chacun des transistors fabriques.

Masque 1 : Implantation d'isolation Masque 2 : Definition des zones actives

Masque 3 : Implantation d'ajustement de la tension de seuil des transistors a appauvrissement Masque 4 : Definition des grilles (Polyl)

Masque 5 : Definition des contacts

Masque 6 : Definition des interconnexions (Metall)

Les circuits sont fabriques sur des tranches de 76 mm dopees P de 1 a 10 Q-cm. La fabrication se fait a partir de masques de 102 mm compatibles avec I'aligneuse OAI 200.

Les sections suivantes decrivent les principales etapes du procede reliees a chacun des masques. Plus de detail sont disponibles dans [7],

3.1.1 Description du procede

Masque 1 : Implantation d'isolation

L'implantation d'isolation entre les transistors se fait au travers d'un masque d'oxyde :

• Nettoyage RCA

• Croissance seche d'oxyde (500 nm)

• Definition des regions d'isolation dans I'oxyde par gravure humide (masque 1) • Implantation d'isolation (bore, l x l O1 4 cm"2 a 40 keV)

Masque 2 : Definition des regions actives

Cette etape comprend non seulement la photolithographie pour definir les regions actives mais egalement, la croissance d'oxyde de grille ainsi que I'implantation d'ajustement de tension de seuil des transistors a enrichissement. Cette implantation se fait au bore a deux differentes doses pour fins de tests, 4 x l Ou cm-2 et l x l 01 2c m - 2 :

• Nettoyage RCA

• Croissance d'oxyde de champ (500 nm)

• Definition des regions actives par gravure humide (masque 2) • Croissance seche d'oxyde de grille (100 nm)

• Implantation d'ajustement de VT des transistors a enrichissement a 26 keV (differentes doses)

Masque 3 : Ajustement de VT des transistors a appauvrissements

Cette etape sert a ajuster la tension de seuil des transistors a appauvrissement par une implantation ionique de phosphore a deux differentes doses aux fins de tests, a 3xl01 2 et 4 x l 01 2 cm"2. L'implantation est masquee par la resine utilisee pour la photolithographie :

• Photolithographie (masque 3)

• Implantation d'ajustement de VT des transistors a appauvrissement a 80 keV (differentes

doses)

Masque 4 : Definition des grilles {Polyl)

C'est dans cette etape qu'est depose, grave et implante la couche de polySi servant de grille. L'implantation ionique qui'suit la gravure du polySi sert egalement a creer les sources/drains des transistors :

• Deposition de 400 nm de polySi LPCVD a 620°C

• Definition des grilles de Polyl par gravure humide (masque 3) • Implantation source/drain de phosphore (2xl01 5 cm"2 a 100 keV)

Procede de fabrication

19

• Recuit d'activation des porteurs a 950°C pendant 30 minutes

Masque 5 : Definition des contacts

Une couche d'oxyde PECVD est utilisee pour isoler la couche d'interconnexion d'aluminium {Metall) de la region active des transistors :

• Depot de 100 nm d'oxyde PECVD

• Definition des contacts gravure humide (masque 5)

Masque 6 : Definition des interconnexions (Metall)

La derniere etape consiste a evaporer la couche de I'aluminium sur la face avant et la face arriere de la tranche :

• Evaporation d'une couche de 200 nm d'aluminium

• Definition des interconnexions par gravure humide (masque 6) • Protection de la face avant avec de la resine

• Decapage de la face arriere par gravure humide

• Evaporation d'une couche de 200 nm d'aluminium sur la face arriere • Recuit pour former I'alliage Al-Si a 450°C pendant 30 minutes

3.1.2 Description des circuits

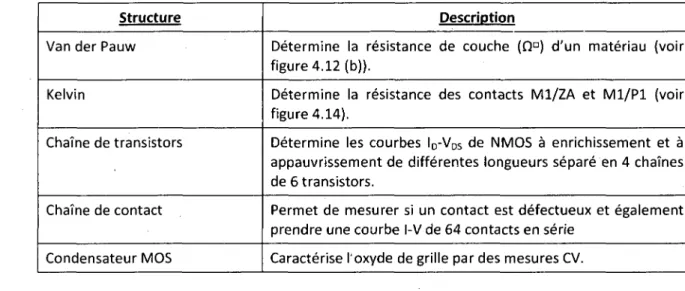

Tableau 3.1 Resume des structures developpees sur JOPE avec leurs descriptions et les resultats

Structure

Van der Pauw

Kelvin

ChaTne de transistors

Chame de contact

Condensateur MOS

Description

Determine la resistance de couche (fiD) d'un materiau (voir figure 4.12(b)).

Determine la resistance des contacts M l / Z A et M l / P i (voir figure 4.14).

Determine les courbes lD-VDS de NMOS a enrichissement et a appauvrissement de differentes longueurs separe en 4 chaTnes de 6 transistors.

Permet de mesurer si un contact est defectueux et egalement prendre une courbe l-V de 64 contacts en serie

Caracterise I'oxyde de grille par des mesures CV.

3.1.3 Problemes de la technologie

Les resultats experimentaux de JOPE sont preponderants pour le projet puisqu'ils determinent quelles sont les modifications apportees au procede pour etablir JOPE2. Cette section presente les resultats electriques des materiaux et des transistors qui sont problematiques pour I'etablissement de la technologie dans le contexte d'une application reelle.

Tension de seuil

Les mesures prisent sur les transistors a appauvrissements des circuits JOPE sur differentes tranches, montrent une variation de tension de seuil (VT) de 0.42 a 1.29 V. Cette grande variation peut etre

fatale pour plusieurs circuits complexes. Plusieurs facteurs provoquent cette fluctuation, il y a I'epaisseur d'oxyde de grille (Tox), la resistivite du substrat (p), et la charge d'interface Q,. Le modele

simple permettant de determiner VT est presente a I'equation 3.1, ou T0x affecte la capacite de

I'isolant (C,) e t p affecte la charge de la zone de depletion (Qd).

n.

Qa

l

'T ~ V>>ns -!" 7T ~ T~ T

2(Pf;

r r. 3.1

La figure 3.1 montre la variation de VT en fonction de la tolerance de la resistivite des tranches

Procede de fabrication 21

que VT varie d'au plus 1.2 V. Ce AVT est critique et est defini principalement par la tolerance de la

resistivite du substrat et de facons moins importantes, par la stabilite de T0

x-Resistivity du substrat (ohm-cm)

%0 95 100 105 110

Tox (nm)

Figure 3.1 Tension de seuil en fonction de I'epaisseur d'oxyde de grille pour differente resistivite de substrat

L'autre parametre tres important qui influence VT est Q„ la charge presente a I'interface Si/SiO

Celles-ci seront traitees a la section 4.3.2.

Resistivite des couches

Le polySi (Polyl) depose par LPCVD a une resistivite de couche moyenne >250fiD. En industrie, il est commun de t r o u v e r des procedes CMOS ayant une couche de polySi de 12 nD [40]. Avec une resistivite aussi faible, le Polyl pourrait etre utilise comme couche d'interconnexion locale3 en plus de la couche d'aluminium (Metall) de 0.2 QD. Pour arriver a cette fin avec le procede JOPE, la resistivite du Polyl doit etre diminuee.

La resistance elevee du Polyl affecte non seulement les interconnexions mais egalement la bande passante des dispositifs. En effet, la resistivite des grilles affecte directement la constante de temps de charge des condensateurs MOS. Plus la resistivite sera reduite, plus grande sera la bande passante.

Afin d'apporter les corrections necessaires pour diminuer la resistivite, le dopage ainsi que la grosseur de grain ont ete evalues pour determiner les parametres optimaux de deposition et d'implantation du polySi.

Resistance des contacts

Un contact est la jonction entre le Metall et le Polyl ( M l / P l ) , pour connecter typiquement la grille, ou la jonction du Metall avec la zone active (Ml/ZA), pour connecter typiquement les sources/drains. Les contacts sont tres resistifs dans le procede JOPE et presentent un redressement Schottky. La courbe l-V d'une chaTne de 64 contacts M l / P l est montree a la figure 4.16. La resistance moyenne des contacts M l / P i est >100 Q et des contacts M l / Z A est >450 Q. A titre d'exemple, il est possible de trouver dans la litterature des contacts AI/SiN+ de 3 u.m de moins de 10 0. [11].

La haute resistivite des contacts augmente la resistance source/drain (RDS) des transistors, ce qui

induit une perte energetique et une augmentation du bruit electronique, critique pour les circuits analogiques faibles bruits. La solution pour reduire cet effet est de mettre plusieurs contacts en parallele.

Le redressement Schottky est encore plus nefaste puisqu'il peut empecher le fonctionnement de circuits et introduit de la distorsion harmonique.

Modulation de la longueur de canal (X)

Les effets de canal courts, generalement associes aux transistors submicroniques, peuvent engendrer une diminution effective de la longueur de canal en regime de saturation en fonction de la tension de drain appliquee. Ceci a pour effet de diminuer la transconductance, ce qui engendre des harmoniques en traitement du signal analogique. Dans le cas de transistors a grille submicronique, la modulation du canal peut-etre attribuee au Drain-Induced Barrier Lowering (DIBL). Ce phenomene survient lorsqu'un canal est peu dope, que la jonction source/drain est trap profonde ou encore que I'oxyde de grille est trop epais [42]. La modulationde longueur du canal (X) s'exprime en V1. II est souhaitable d'obtenir la plus petite valeur possible pour avoir une variation de lD la plus faible possible. La

modulation du canal mesuree pour JOPE est de 0.03 V"1.

3.2 JOPE2

Suite aux resultats experimentaux obtenus avec JOPE (section 3.1.3), plusieurs modifications ont ete apportees au procede pour creer JOPE2. Ces changements ont pour but de regler les problemes lies au procede. Cette section presente done en detail les changements apportes. Le chapitre 3 presente

Procede de fabrication 23

les masques realises, la fabrication ainsi que les resultats experimentaux. Les vues en coupe des etapes des du procede sont presentees a I'annexe A.

3.2.1 Ajustement de la tension de seuil

Puisque la tension de seuil est un probleme important de JOPE, on prevoit un ajustement de VT

adapte pour chaque tranche selon sa resistivite et I'epaisseur d'oxyde de grille. Pour ce faire, les puces C, D et E permettent de prendre une mesure de Tox par ellipsometrie et une mesure de

resistivite du substrat avec une mesure CV par sonde au mercure (4.2.1).

Pour arriver a ajuster VT pour chaque tranche, un algorithme sur Matlab a ete concu afin de calculer

automatiquement I'energie et la dose d'implantation necessaire pour creer les transistors a appauvrissement et a enrichissement. Le calcul se fait selon T0x et selon la resistivite du substrat (p5). Cette section presente le fonctionnement de I'algorithme.

Pour utiliser le logiciel, on doit entrer les parametres suivants :

Epaisseur d'oxyde de grille determinee par ellipsometrie (Tm)

. La resistivite du substrat determinee par une mesure CV (ps)

La tension de seuil desiree des transistors a appauvrissement et a enrichissement (VT)

La dose d'implantation du polySi realisee (Dp)

Determiner la concentration de porteurs requise

Puisqu'une tranche dopee P est utilisee, la premiere etape est de trouver la densite d'accepteur du substrat (Na.s) selon I'equation 3.2.

P = — —2 ; 3.2

La mobilite des trous \ip est dependante de la concentration d'impuretes totale, dans ce cas ci, la

Vv =

A\-A ' « .= 54,3 cm"/V x s

selon < ^c

= 4 0 6'

9 c m :/ V * £

Ka = 0.38

3.3N,

ef= 2.35 X 10

17cm"

Ce calcul est important puisqu'on trouve que \xp varie de 11% quand la resistivite varie de 1 a 10

Q-cm. Ceci represente done une erreur relative de 11 % dans le calcul de Na.s si ^pe s t estime a la valeur du silicium intrinseque.

Ensuite, le calcul de la concentration d'accepteurs desiree dans le canal (Na.d) pour obtenir la tension de seuil desiree est determine par la densite de charge de la zone de depletion (Qd) selon

I'equation 3.4 et le potentiel de Fermi du substrat (cpFs) selon les equations 3.5 et 3.6. Ces parametres

sont le lien entre N0 et VT (equation 3.1).

<0r, =

!n[ —

'-) 3.4Qd-nr = -2y/s

tqN

a_

t.ln(N

a_

ti/n

i)<p

Fs 3.5Qd-ttv =2^/e

£qN

a.

liln(N

e.

d/n

i)\if>

I 3.6D'autres parametres sont egalement necessaires pour calculer Na.d. Premierement, la densite de

charge d'interface (Q,) est determinee a la section 4.3.2. Deuxiemement, la difference de potentiel du metal-semiconducteur (<pms), determinee selon I'equation 3.7 et 3.8. De plus, il est demontre a la section 3.2.3 que le polySi est degenere pour JOPE et JOPE2 et done son travail (cpp) est egal a I'affinite

Procede de fabrication 25

* * i f - dej

= $? -

4>su

<PFS

Xv

~-f"

-<P.r,

= <pFs ~ •PolvSilicium

Les differents parametres de ces equations sont illustres a la figure 3.2.

3.8 Polysilicium (N+) I I Canal Si (P) Isolant (b) Vide

T

EcTE EF *-.A

*

Polysilicium (N+) \ qc|3: qxsi Tq*Fsi E,

Canal Si (N) IsolantFigure 3.2 Etats de I'energie pour la grille et le canal des transistors a enrichissement (a) et a appauvrissement (b)

Ainsi, les concentrations de porteurs a implanter en surface du canal sont exprimees aux equations 3.9 et 3.10. La concentration surfacique de bore que I'on doit implanter pour appauvrir le canal des transistors a enrichissement est notee A/„.,. Celle-ci est egale a la concentration desiree (Na.d)

moins la concentration de trous deja presents initialement dans le substrat (N0.s).

Dans le cas des transistors a appauvrissement, la concentration surfacique de phosphore que I'on doit implanter pour enrichir le canal est notee A/d.,. Comme I'implantation Nd.j est faite en second, on doit

compenser I'implantation A/0.,. Done, A/d_, est egal a N0.d ajoute a la concentration de donneurs desiree