To cite this version :

Goiffon, Vincent and Corbière, Franck and

Rolando, Sébastien and Estribeau, Magali and Magnan, Pierre and

Avon, Barbara and Baer, Jeremy and Gaillardin, Marc and Molina,

Romain and Paillet, Philippe and Girard, Sylvain and Chabane,

Aziouz and Cervantes, Paola and Marcandella, Claude

Multi-MGy Radiation Hard CMOS Image Sensor: Design,

Characterization and X/Gamma Rays Total Ionizing Dose Tests

.

(2015) IEEE Transactions on Nuclear Science, vol.62 (n°6). pp.

2956-2964. ISSN 0018-9499

O

pen

A

rchive

T

OULOUSE

A

rchive

O

uverte (

OATAO

)

OATAO is an open access repository that collects the work of Toulouse researchers and

makes it freely available over the web where possible.

This is an author-deposited version published in :

http://oatao.univ-toulouse.fr/

Eprints ID : 14621

Any correspondance concerning this service should be sent to the repository

administrator:

staff-oatao@listes-diff.inp-toulouse.fr

Multi-MGy Radiation Hard CMOS Image Sensor:

Design, Characterization and X/Gamma Rays

Total Ionizing Dose Tests

Vincent Goiffon, Member, IEEE, Franck Corbière, Sébastien Rolando, Magali Estribeau, Member, IEEE,

Pierre Magnan, Member, IEEE, Barbara Avon, Jérémy Baer, Marc Gaillardin, Member, IEEE,

Romain Molina, Philippe Paillet, Senior Member, IEEE, Sylvain Girard, Senior Member, IEEE,

Aziouz Chabane, Paola Cervantes, and Claude Marcandella

Abstract—A Radiation Hard CMOS Active Pixel Image

Sensor has been designed, manufactured and exposed to X and -ray sources up to several MGy of Total Ionizing Dose (TID). It is demonstrated that a Radiation-Hardened-By-Design (RHBD) CMOS Image Sensor (CIS) can still provide useful im-ages after MGy (i.e. 1 Grad). This paper also presents the first detailed characterizations of CIS opto-electrical perfor-mances (i.e. dark current, quantum efficiency, gain, noise, transfer functions, etc.) in the MGy range. These results show that it is possible to design a CIS with good performances even after having absorbed several MGy. Four different RHBD photodiode designs are compared: a standard photodiode design, two well known RHBD layouts and a proposed improvement of the gated photo-diode design. The proposed layout exhibits the best performances over the entire studied TID range and further optimizations are discussed. Several original MGy radiation effects are presented and discussed at the device and circuit levels and mitigation tech-niques are proposed to improve further the radiation hardness of future Rad-Hard CIS developments for extreme TID applications (e.g. for nuclear power plant monitoring/dismantling, experi-mental reactors (e.g. ITER) or next generation particle physics experiments (e.g. CERN)).

Index Terms—Active pixel sensors, APS, CIS, CMOS, CMOS

image sensors, complementary-metal-oxide-semiconductor, dark current, deep submicron process, DSM, ELT, enclosed layout transistors, gamma-rays, gigarad, Grad, image sensors, integrated circuit, interface states, ionizing radiation, MAPS, MGy, mono-lithic active pixel sensor, quantum efficiency, rad-hard, radiation damage, radiation effects, radiation hard, radiation hardening, radiation tolerant, RHBD, shallow trench isolation, STI, TID, total ionizing dose, trapped charge, X-rays.

I. INTRODUCTION

T

HERE is a fast growing interest in the development of compact radiation hard imaging systems based on solid state image sensors that are able to provide good qualityManuscript received July 10, 2015; revised October 01, 2015; accepted October 06, 2015. Date of current version December 11, 2015.

V. Goiffon, F. Corbière, S. Rolando, M. Estribeau, P. Magnan, B. Avon, J. Baer, R. Molina, A. Chabane, and P. Cervantes are with ISAE-SUPAERO, Université de Toulouse, Image Sensor Research Team, F-31055 Toulouse, France (e-mail: vincent.goiffon@isae.fr).

M. Gaillardin, P. Paillet, and C. Marcandella are with CEA, DAM, DIF, F-91297 Arpajon, France.

S. Girard is with Université de Saint-Etienne, Laboratoire Hubert Curien, UMR-CNRS 5516, Saint-Etienne, France.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TNS.2015.2490479

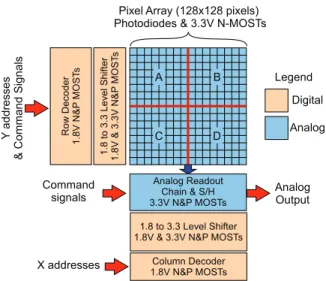

Fig. 1. Architecture overview of the studied CMOS Image Sensor (CIS) Inte-grated Circuit (IC). standard photodiode; surround photodiode;

gate overlap photodiode; aligned gated photodiode.

images after the absorption of extreme radiation doses (above MGy , i.e. 100 Mrad). This is especially true for nu-clear applications [1] such as monitoring and remote handling in highly radioactive areas of nuclear facilities (e.g. nuclear power plants, nuclear waste repository, experimental reactors (e.g. ITER [2]) and next generation particle physics facilities (e.g. CERN [3])) but also for nuclear decommissioning and for mobile rescue robots dedicated to deal with nuclear incidents.

The radiation hardness of Radiation-Hardened-By-Design (RHBD) Active Pixel Sensors (APS) has been explored and sometimes demonstrated (on technologies now obsolete in most cases) up to several hundreds of kGy (several tens of Mrad) [4]–[7]. More recently, the radiation hardness of RHBD CMOS Image Sensors (CIS) has been explored up to a few tens of kGy (i.e. a few Mrad) [8]–[10] and some dark current measurements have been reported on a RHBD APS (not based on a CIS process) for electron microscopy up to 2 MGy [11]. However, to date, an image captured with a solid state image sensor exposed to 1 MGy or more has not been reported and the radiation hardness of a modern CIS technology in the MGy range has not been evaluated in literature.

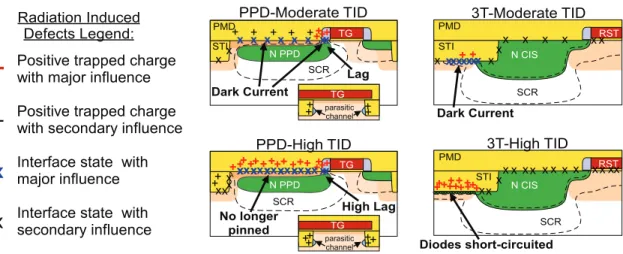

Fig. 2. Illustration of the TID induced degradation mechanisms in Pinned Photodiodes (PPD) and conventional photodiode (referred to as 3T here) at moderate (2-20 kGy) and high TID ( kGy). In the 3T case, the STI sidewalls of the RST MOSFET channel are not represented here because their influence on the pixel radiation hardness is secondary [12] compared to the other degradation sources illustrated here.

The aims of this work are:

• to design and characterize a fully radiation-hardened-by-design CIS in the MGy range to demonstrate that radiation-hardened-by-designing an imaging system which can withstand MGy-Grad dose levels can be achieved;

• to evaluate the opto-electrical performances (beyond simple dark current measurements, such as quantum effi-ciency measurements) at such extreme radiation dose; and • to identify the degradation mechanisms in this TID range

to improve further the radiation hardness.

A new RHBD photodiode layout is also proposed and its per-formances are compared to the most promising existing solu-tions.

II. RADIATION-HARDENING-BY-DESIGNSTRATEGY

A. Circuit RHBD Strategy

The overall architecture of the studied CIS is presented in Fig. 1. For this first exploration in the MGy range, sequencing and Analog-to-Digital-Conversion (ADC) are realized off-chip. Row and column decoders are pure 1.8 V logic circuits which have been designed using the radiation tolerant IMEC DARE UMC 180 nm platform funded by ESA [13]. All the I/O pads (not shown in the figure) are also based on that DARE platform. CIS are mixed signal Integrated Circuits (IC) that require a significant voltage swing to provide a good dynamic range. For this reason, the pixel array and the analog readout circuits are designed using 3.3 V MOSFETs (much more sensitive to TID than 1.8 V core MOSFETs [14], [15]) and 1.8 V-to-3.3 V level shifters [16] are required. The pixel array, the analog readout chain and the level shifters have been fully radiation hardened by ISAE-SUPAERO by using well established RHBD techniques [17]. Especially, Enclosed Layout Transistors (ELT) have been used for N-MOSFETs (to mitigate the lateral parasitic leakage path and the Radiation Induced Narrow Channel Effect (RINCE) [14], [18]) but also for P-MOSFETs (mainly to mit-igate the RINCE). Extreme care has been taken to enclose the nodes sensitive to leakage currents (e.g. sampling nodes) and rings or additional gates have been used to avoid inter de-vice leakage wherever necessary.

B. Photodiode RHBD Strategy

The two main types of photodetectors used in CIS today are the conventional photodiode that can be found in 3-Transistor (3T) active pixels [19] and the buried photodiode, called the Pinned Photodiode (PPD) [20], [21]. The main radiation in-duced degradation mechanism in conventional photodiodes and in PPD at high TID is the effect of the radiation induced posi-tive charge trapping in the STI, the TG spacer and the pre-metal dielectric (PMD) (see Fig. 2) that leads to the depletion and the inversion of the P-doped layers. In PPD pixels, the PMD and TG spacer trapped charges induce important image lag that can be followed by a disappearance of the pinning layer [22]. To date, there is no RHBD technique validated experimentally in literature that can mitigate this radiation effect [9]. In 3T pixels, the STI positive trapped charge leads to a short circuit between the photodiode and the surrounding N regions and to a drop of Charge-to-Voltage conversion Factor (CVF) [10]. Both radia-tion effects can be mitigated by using RHBD techniques. For these reasons, PPDs were excluded for this study (including hole channel PPDs [23], [24] that are also likely to suffer from impor-tant image lag at high TID because of the PMD/spacer trapped charge) and conventional photodiodes hardened-by-design were selected.

The two most promising solutions identified in [10] were chosen: the gated [4], [5], [10], [25], [26] and the surround [10] photodiodes as illustrated in Fig. 3.

In classical gated photodiode designs, the N implant is either self-aligned on the gate edge (by using a self-aligned im-plant [4], [5], [25] as shown in the cross-section D of Fig. 3), or voluntarily drawn to cover only the P region [10], [26]. It means that classical gated photodiode designs are never meant to cover the N depleted region. It has two major consequences: 1) the N depleted region is in contact with the PMD interface where a higher interface state density ( ) is expected compared to the gate oxide interface; 2) at the optimum voltage (P region in ac-cumulation) the depleted region is pinched between the highly doped N region and the accumulated P region, which leads to high Electric Field Enhancement (EFE) of the dark current as illustrated in Fig. 4(a). This effect can be enhanced at high TID because the positive trapped charge density ( ) near the gate

Fig. 3. Cross sectional views of the studied photodiode layouts.

Fig. 4. Magnification of the peripheral depletion region on (a) the classical aligned gated diode design and (b) the proposed gate overlap design. The de-pleted interface is narrowed in the classical gated diode design leading to electric field enhancement of the dark current.

pinches further the depleted region at the interface in the N re-gion, leading to a even higher electric field.

To mitigate this aligned gated photodiode limitations, a new design is proposed and tested here: the gate overlap design (layout C in Fig. 3) which corresponds to a gated photodiode layout where the gate completely covers both N and P depleted regions. By doing so, only the gate oxide is in contact with the PN-junction (reducing the interface state density in the depleted region). Moreover, when the gate is accumulated, the depleted interface on the P-side almost disappears but there is still a significant depleted interface thickness on the N-side, mitigating the EFE [as shown in Fig. 4(b)].

III. EXPERIMENTALDETAILS

A. Test Chip

The manufactured CIS pixel array is constituted by

3T m pitch pixels and it is divided in four sub-arrays (of pixels, as depicted in Fig. 1) each with a different pho-todiode (details of the phopho-todiode cross sections are given in Fig. 3). The CVF values are about V/e for the standard diode and V/e for the three RHBD layouts (this differ-ence is due to an additional parasitic capacitance in RHBD pho-todiode). These CVF values include a readout gain of 0.7.

The in-pixel MOSFETs and all the readout chains are the same for the entire array. In other words, the only difference between the four pixels is the photodiode layout. This evalua-tion circuit is a front side illuminated sensor, without microlens

TABLE I

IRRADIATIONCONDITIONSSUMMARY. RT STANDS FORROOMTEMPERATURE. ALL THETIDARE GIVEN IN

and without color filter array, and it was manufactured using a commercially available 180 nm CIS process.

Another CIS with the same design but with only a single pho-todiode design (the gate overlap design) for the entire

pixel array is also present on the same die as the main image sensor. This uniform CIS was sometimes used for additional measurements, especially to compare the effect of biasing on the radiation induced degradations (see Section V).

Several MOSFET test structures are also located on the same die but the detailed analysis of their behavior after exposure to ionizing radiation is performed in another study [15].

B. Irradiation

The irradiation conditions are summarized in Table I. All the TID given in this paper are expressed in . The results presented here have been obtained on nine sensors.

For a CIS the worst case biasing conditions are still unclear, especially in this unexplored TID range. It is possible to apply DC biases on the sensor but, without sequencing the sensor, the voltages will not be transmitted to the floating nodes (such as the most important part of the sensor: the photodiodes) and most of the nodes and transistors of the IC will not see the applied bias during exposure. For this reason, it is supposed in this study that the worst case bias condition for a CIS is powered ON with nom-inal bias and nomnom-inal sequencing (i.e. as in standard operating conditions, when the sensor is acquiring frames continuously).

All the X-ON sensors were irradiated ON (powered and operated during exposure) with an ARACOR semiconductor 10 keV X-ray irradiator at CEA-DIF (at Room Temperature (RT)). X-OFF1 and X-OFF2 were irradiated at the same time (on the same die) as X-ON1 and X-ON2, in the same conditions except that X-OFF1 and X-OFF2 were grounded during expo-sure. X-OFF1 and X-OFF2 are uniform pixel arrays whereas all the other studied CIS are divided in four sub-arrays as described in the previous subsection. -ray irradiation were performed on -OFF1 to 3 at SCK-CEN BRIGITTE facility at position B. For practical reasons, it was not possible in the timeframe of this first evaluation to develop an irradiation setup for BRIGITTE able to withstand more than 1 MGy of TID while operating properly the irradiated sensors. As a consequence, the devices

Fig. 5. Dark Current as a function of gate bias before irradiation for the four studied pixel layouts. Standard and P+ surround photodiodes have no surrounding gate (no influence of the gate voltage on their dark current). Temperature .

exposed to -rays were grounded during irradiation. It is also important to notice that the average temperature inside the BRIGITTE container was about (i.e. more than 25 degrees above the RT conditions used at CEA). The dose rate was ten times lower at BRIGITTE than at CEA-DIF.

The measurements were typically performed between 24 h and one week after exposure to ionizing radiation to allow for shipment to ISAE facilities and full image sensor characteri-zation. The weak room temperature annealing variations over this period were clearly negligible compared to the radiation in-duced variation from one TID step to another.

IV. CIS PERFORMANCESBEFOREIRRADIATION

Fig. 5 presents the mean dark current exhibited by the four studied photodiode designs before irradiation as a function of the applied gate voltage. The standard diode design exhibits the lowest dark current. This result was expected since this design is the one for which the process has been optimized by the foundry. The P+ surround design is more than one order of magnitude above the standard design, most likely due to high EFE at the P+/N+ surface junction (as discussed in [10]). As expected also, the classical aligned gated diode design exhibits a high EFE, even at the optimum bias (here again about 10 times more dark current than the standard design). On the contrary, the proposed gate overlap layout manages to reach the low dark current value of the standard design before irradiation. It validates the EFE mitigation with an optimum voltage range (between and mV) more comfortable than the optimum voltage range of the aligned gated design (between and mV). Reaching a dark current value as low as a standard design with a RHBD photodiode is pretty uncommon since a degradation of at least a factor of two is generally observed on RHBD photo-diodes [4], [5], [10].

The standard photodiode has also the highest External Quantum Efficiency (EQE) before irradiation (as shown in Fig. 6) and the RHBD photodiodes suffer from a reasonable loss of sensitivity at short wavelengths due to the use of a polysilicon gate (reducing the transmission in the blue range) or to the use of a highly doped implant (increasing the photo-carrier recombination rate). EQE will be optimized in the

Fig. 6. External Quantum Efficiency (EQE) of the studied pixels before irradi-ation. The EQE is defined as the number of collected electrons divided by the number of incoming photons over the pixel area.

Fig. 7. Raw images captured before (left) and after (right) MGy ( Grad ) of TID with comparable illumination conditions. The studied pixel sub-arrays are distributed as follows. Top-left: sub-array A, standard photodiode. Top-right: sub-array B, surround photodiode. Bottom-left: sub-array C, gate overlap photodiode. Bottom-right: sub-array D, aligned gated photodiode. No dark frame subtraction and no FPN cancellation has been performed.

next test chip by reducing the polysilicon and P+ areas to the minimum required value to ensure a good radiation hardness.

The Maximum Output Voltage Swing (MOVS) is about 600 mV for the standard photodiode and 700 mV for the RHBD ones. This low MOVS (for an optimized CIS process) is due to a wrong reset MOSFET channel implantation (unwanted man-ufacturing issue) that leads to a threshold voltage for the reset MOSFET higher than 1 V whereas a low was targeted. In addition to that, the use of an ELT for the in-pixel reset MOSFET also increases the voltage drop induced by capacitive coupling effect during the reset pulse falling edge. Because of the combination of both effects, the reference voltage of the tested RHBD photodiodes was about 2.1 V (about 2 V for the standard one). Without this process issue, an MOVS of more than 1 V would have been achieved and thus, higher MOVS are expected for the next developments.

V. CIS PERFORMANCESAFTERIRRADIATION

After exposure to ionizing radiation the manufactured radia-tion hard sensors are still fully funcradia-tional (except the standard diode sub-array), even after having absorbed MGy ( Grad ) as illustrated in Fig. 7. This figure presents for the first time an optical image captured by a solid state image

Fig. 8. Overview of the radiation induced degradations observed on the studied sensors as a function of TID. STD stands for standard.

sensor exposed to such a high TID. This image demonstrates that all the integrated functions presented in Fig. 1 are working properly (digital circuits, pixels, readout chain, sample and hold stage) after irradiation since any failure in a sub-block would lead to clear image artifacts. The standard diode failed between 10 kGy and 100 kGy, and it was not possible to measure its per-formances after that.

Despite the fact that the radiation hardened sensor is still able to provide useful images at MGy , several radiation induced degradations have been observed during the test cam-paign. Fig. 8 provides an overview of the main radiation effects as a function of the absorbed radiation dose. Each effect is dis-cussed in details in the following sub-sections.

A. PMOSFET and its Consequences on Analog Circuits

The first major performance degradation that appeared is a drop of speed performance that leads to the column Fixed Pat-tern Noise (FPN) artifact shown in Fig. 9(a). The column FPN is caused by the parasitic capacitive coupling of a column ad-dressing signal on the Printed Circuit Board (PCB). This cou-pling cannot be canceled (at the pixel rate) by the output stage of the sensor due to a too weak output current after irradiation. The output stage of the analog readout chain (see Fig. 1 of [12] for the schematic of one path of the differential readout chain) is a PMOSFET source follower amplifier. The output current de-crease at the origin of this speed issue is caused by a large 3.3 V PMOSFET threshold voltage shift. This large occurring in 3.3 V ELT PMOSFET has been clearly evidenced in a com-panion study on the same technology (foundry C in [15]). The irradiated PMOSFET I-V curves presented in [15] clearly show that radiation induced gate oxide trapped charge is responsible (as it was observed on non-ELT 2.5 V P-MOSFET in [14]). In order to compensate this P-MOSFET , the bias voltage of the output stage ( in Fig. 1 of [12]) has been decreased until recovering good speed performances. It is important to em-phasize that in a commercial product, a dedicated circuit would have been used to automatically compensate the voltage shift (e.g. a radiation hardened current reference circuit). However,

Fig. 9. Raw images showing radiation induced artifacts. (a) Column FPN caused by a too weak output current (PMOSFET readout chain output stage) on a raw dark frame. (b) Random loss of rows due to the failure of 1.8 V to 3.3 V row level shifters. MGy.

Fig. 10. Quasi-static electrical transfer functions of the readout chain for sev-eral TID (obtained from the X-ON CIS). Up to 10 kGy, nominal bias voltages were used for N and P current sources. Beyond, optimum bias voltages ensuring the best performances were used. The 2.1 V photodiode reference level after reset (valid up to 3 MGy for the two gated photodiode designs) is represented in this figure. For each TID, the quasi-static MOVS corresponds to the difference between the output voltage value at this reference voltage and the minimum output voltage value (for low input voltage). The readout gain is the slope of the characteristics in the linear range.

for this evaluation test chip, a direct manual access to each bi-asing point was necessary to fully understand and compensate the radiation induced degradations.

Fig. 10 presents the effect of TID on the quasi-static Elec-trical Transfer Function (ETF) of the readout chain (

characteristic as defined in Fig. 1 of [12]). Beyond 10 kGy, the optimum voltage needed to recover good speed performance was used for P current sources ( in Fig. 1 of [12]). Up to 10 kGy, there is almost no effect on the ETF but at higher TID, the manual voltage compensation performed on the P current source directly shifts the characteristics upward. Up to 1 MGy, no change was performed on the N current source. For 3 MGy and beyond, (as defined in Fig. 1 of [12]) has been slightly increased by 100 mV to compensate the small induced mainly by gate oxide interface states as demonstrated in [15]. The correction of is the reason of the apparent small recovery between 1 and 3 MGy. Here again, this correction would be automatic in a product where a more advanced current reference would be used instead of the elementary current source used for this study.

TABLE II

FIGURES OFMERITEXTRACTED FROMFIG. 10ATSEVERALTID

Several key performances of the CIS can be discussed on these curves. The quasi-static MOVS (i.e. without the effects of parasitic capacitive coupling) corresponds to the difference between the output voltage value at the photodiode reference voltage (input voltage V for the two gated photodiode designs up to 3 MGy) and the minimum output voltage value (for low input voltage). The readout gain can be determined by computing the slope in the linear range. These two figures of merit are reported for some key TID values in Table II.

The MOVS does not vary much up to a few MGy and the readout gain in the linear range does not change much either (except at 1 MGy because has not been corrected for this measurement). The MOVS decreases after 3 MGy because the photodiode reset voltage ( in Fig. 1 of [12]) has to be slightly decreased to keep the reference voltage of the photo-diode in the linear range of the ETF.

By doing so, it was possible to ensure a significant linear range enabling the accurate characterization of the sensors up 5 MGy (but with a small decrease of readout gain, about 10-15%, due to the shift of operating point on the curve). At 10 MGy, the non linearities induced by the large P-MOSFET were too strong (there is nearly no linear range on the 10 MGy curve in Fig. 10) to enable the accurate determination of the different parameters required to estimate properly the electro-optical performances of the sensor. For this reason, no parameter evaluation (such as dark current, quantum effi-ciency…) is presented at 10 MGy in this paper, despite the fact that the sensor is still able to provide usefull images at this TID level.

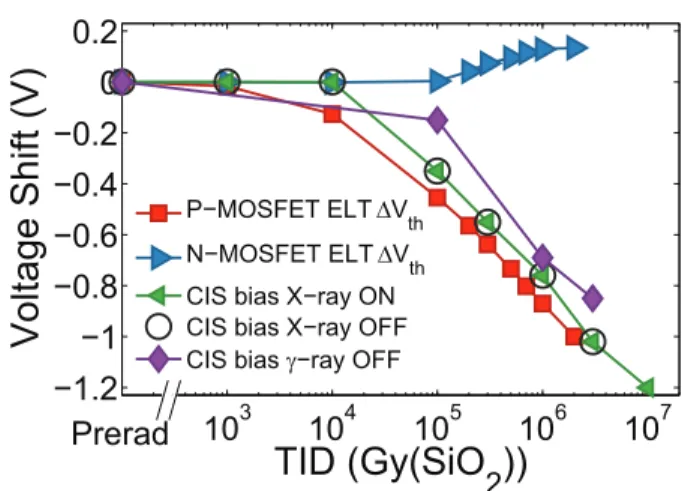

Fig. 11 presents a comparison between the P-MOSFET cur-rent source bias voltage shift that was applied to keep good speed performances and the P and N ELT MOSFET threshold voltage shifts measured on irradiated MOSFET test structures (from [15]). The optimum bias voltage shift is shown for the X-ON CIS but also for the X-OFF and the -OFF CIS. The op-timum bias voltage shifts follow nicely the large P-MOSFET but with a small delay. This delay can be explained by the margin used before irradiation on the nominal output current of the P-MOSFET output stage. This current was set to a value much larger than what is necessary to drive the sensor output at the used pixel rate. On the other hand, after irradiation, the op-timum P current source bias voltage was chosen to provide the required output current with much less margin. Hence, part of the P-MOSFET is compensated by the margin reduction on the output current source leading to this apparent right-shift on CIS curves.

This graph also shows clearly that the CIS biasing conditions during irradiation have little effect on the P-MOSFET induced degradation. Surprisingly, -ray OFF irradiations lead to less voltage shift than X-ray ON and OFF conditions. This is most likely due to the higher irradiation temperature (leading to more annealing during irradiation) of -ray irradiations or to the dif-ference in dose rate (less likely). The origin of this

discrep-Fig. 11. Radiation induced threshold voltage shift ( ) measured on indi-vidual 3.3 V ELT N and P MOSFETs (data from [15]) compared to the P current source optimum voltage shifts (curves called CIS bias in the figure) that have been applied to the irradiated CIS to keep good performances.

ancy will be the subject of future work but these first results strongly suggest that -ray ON irradiations should not lead to much larger degradation than the X-ray ON conditions used in this study.

It is interesting to notice in Fig. 11 that the N-MOSFET threshold voltage shift is much weaker than the P-MOSFET one and that the saturation value reached by the N-MOSFET after a few MGy corresponds well to the correction ( mV) performed on the N current source bias voltage to recover the nominal readout gain value after 3 MGy. The surprising dissymmetry between N and P 3.3 V ELT MOSFETs has also been reported in [14] and is further studied and discussed in [15].

B. PMOSFET and its Consequences on Digital Circuits

After a few MGy of absorbed TID, some random and tran-sient digital artifacts such as the ones presented in Fig. 9(b) start to appear all over the array. This effect is also caused by the large 3.3 V PMOSFET but in this case, a digital circuit is involved. The only digital circuits that make use of 3.3 V PMOSFET transistors are the level shifters used to adapt the 1.8 V logic command signals to the 3.3 V pixel transistors. The schematic of the level shifter used in this CIS (a conventional type-I level-up shifter) can be found in [16]. In order to set the node T1 (see Fig. 1 in [16]) to high the following equation must be satisfied:

(1) where and are the threshold voltages of P and N 3.3 V MOSFETs respectively, and the mobility. It can clearly be seen in this equation that when is too high, it is not possible to set T1 to high and this node is stuck to low [leading to the row addressing issue shown in Fig. 9(b)]. The most efficient way to compensate the large is to boost the numerator by increasing slightly the 1.8 V digital supply voltage. This has been done by adding between 100 and 200 mV (depending on the TID level) to the 1.8 V digital supply voltage and it has mitigated completely the parasitic effect shown in Fig. 9(b).

Fig. 12. Mean dark current versus Total Ionizing Dose (TID) with optimum gate bias for the four studied pixels. Temperature . This set of data has been obtained on the four X-ON CIS powered during X-ray irradiation.

TABLE III

COMPARISON OF THERHBD PHOTODIODEPERFORMANCES

C. Dark Current Increase

The evolution of dark current with TID is presented for the four studied pixel designs in Fig. 12 and an overall compar-ison of the key performances of these pixels is summarized in Table III. As always in irradiated CIS, a continuous increase of dark current with TID is observed from the first TID step to at least 100 kGy. The standard photodiode design suffers from an extremely fast rise of its dark current with TID. On the other hand, the RHBD photodiodes manage to contain this inevitable degradation with an improvement of more than five orders of magnitude at 10 kGy. Beyond 10 kGy the standard photodiode is no longer sensitive to light (most likely because of the sur-rounding STI inversion as illustrated in Fig. 2) and the dark cur-rent can not be estimated anymore.

The proposed gate overlap design exhibits the best perfor-mances on the whole TID range, with about one order of mag-nitude improvement before irradiation to a factor of two im-provement at the highest TID (in the MGy range) compared to the classical gated photodiode. At 1 kGy, the P+ surround photodiode performs as well as the gate overlap diode. It con-firms that this design is still a good candidate for low TID ap-plications (as concluded in [10]). Nevertheless, this device de-grades faster than the other RHBD ones in the 1-100 kGy range, most likely because of the reduction of the effective surface P+ doping due to the PMD trapped charge. Hence, for the MGy range the polysilicon gate appears to be necessary to shield properly the diode from trapped charge related effects.

The dark current reaches a saturation regime on the three RHBD layouts after a few hundreds of kGy. Such saturation mechanism has been previously reported in solid state active pixel sensors at similar TID levels (700 kGy in [27] and about 500 - 600 kGy for the 65 nm process in [28]) but to date, it has not really been discussed or explained. Since at least in the

Fig. 13. Comparison of the radiation induced mean dark current increases of the gate overlap photodiode (pixel C) observed on the nine studied sensors (with different irradiation conditions as defined in Table I). Temperature .

two gated designs, the junction is shielded from the radiation in-duced trapped charge, the dark current increase in this TID range is most likely only due to the interface state buildup. Therefore, this saturation is probably due to a saturation of the radiation induced interface state density in the gate oxide of 3.3 V tran-sistors.

This hypothesis is in good agreement with the apparent sat-uration of the interface states induced threshold voltage shift observed on the irradiated 3.3 V N-MOSFET (see Fig. 11).

Fig. 13 compares the TID induced dark current rise for dif-ferent irradiation conditions. There is no noticeable difference between ON and OFF X-ray irradiations and the data points align very well (as in Fig. 11) showing that there is very little disparity from one circuit to another. Here again, the higher tem-perature -ray irradiations lead to a weaker degradation than X-rays at a given TID (about 40% reduction). Since the satura-tion regime seems to correspond very well between X and -ray irradiations, a dosimetry error is very unlikely. On the contrary, the fact that the curve appears to be shifted downard with -ray irradiation agrees well with a more intense annealing due to the higher temperature of -ray exposure. Here again, these results suggest that the worst case irradiation conditions (biased -ray irradiations) should not lead to much larger degradations than what is observed with biased X-ray irradiations.

Finally, as regards the dark current uniformity, the dark cur-rent distributions were pretty uniform and no border effect was observed (contrary to what has been reported in [29]–[31]). D. Opto-Electrical Transfer Function and Quantum Efficiency

The Opto-Electrical Transfer Functions (OETF) of the four studied pixels before and after irradiations are presented in Fig. 14. This figure summarizes well most of the observed radi-ation effects (at 4 MGy): an increase of dark signal, a reasonable reduction of MOVS (10-20%) due to the , no dramatic drop of slope in the linear region (no important loss of sensitivity at this wavelength) for the RHBD photodiodes and a complete loss of sensitivity for the standard photodiode design. More insight into the sensitivity degradation is provided by Fig. 15, which presents the evolution of the EQE with TID for the Gate Overlap Pixel. It shows an EQE drop in the blue part of the spectrum. This effect is due to the buildup of interface states that enhance the surface electron-hole recombination.

Fig. 14. Opto-electrical transfer functions at 650 nm before irradiation and after MGy for the four studied pixel sub-arrays. Temperature .

standard, , Overlap and Gated.

Fig. 15. External Quantum Efficiency of the gated overlap photodiode (pixel C) for several TID showing the sensitivity reduction at short wavelengths.

It leads to the loss of signal carriers generated close to the surface [12], [32] where most of the short wavelength photons are absorbed (in front side illuminated sensors). However, this degradation is very limited when compared to what could have been extrapolated from previous studies up to 3 kGy [12], [22]. E. CVF and Readout Noise

No obvious change of CVF has been observed on the gated photodiode design except the slight decrease after several MGy due to readout gain reduction (caused by the PMOSFET , as discussed in Section V-A). Hence, it can be inferred that the photodiode capacitance is not degraded after irradiation in gated photodiodes. Readout noise also remained stable around Vrms for the three RHBD layouts and around Vrms for the standard design.

VI. DISCUSSION: FURTHERRADIATIONHARDNESS

IMPROVEMENT

A. 3.3 V P-MOSFET Shift

The radiation induced trapped charge in PMOSFET double gate oxide (GO2) that is at the origin of very large threshold voltage shifts in 3.3 V ELT PMOSFETs is the root cause of most of the performance degradations of this first test chip. This dis-symmetry between N and P channel GO2 MOSFETs appears on all the deep-submicron CMOS technologies tested in the

TABLE IV

SUMMARY OF THEPROPOSEDIMPROVEMENTS TOPOSSIBLYREDUCE THE

DARKCURRENT

MGy range so far but with different magnitude depending on the foundry [14], [15]. To mitigate this degradation that can affect both analog and digital circuits, the two following so-lutions will be explored on the next test chip: 1) Using a full NMOST based analog readout chain. This solution should not reduced the MOVS before irradiation but the circuit will still suffer from a small interface state buildup induced shift (about 100 mV here). Additionally, the level shifter design will have to be adapted to ensure that it can still function properly even after a large PMOSFET (e.g. by increasing the width of the NMOST or by changing its architecture). 2) Using only 1.8 V simple gate oxide (GO1) MOSFETs. It should ensure the most stable performances with TID since GO1 MOSFET degra-dations are really weak in the MGy range [14], [15]. Neverthe-less, the achieved performances before irradiation (especially the MOVS) could be lower with 1.8 V MOSFETs than the per-formances achieved after irradiation with the first solution (full 3.3 V NMOST readout chain).

B. Dark Current Increase

Despite first encouraging results compared to a standard de-sign, the dark current rise is still important and the overall sensor performances could be much improved by a further reduction of the radiation induced dark current. The following improve-ments of the Gate Overlap design (summarized in Table IV) will be explored in the next test chip: 1) to use a GO1 gate oxide in-stead of the GO2 one for the surrounding gate used to harden the photodiode (to reduce the interface state buildup in this critical region); 2) to optimize the overlap distance between the gate and the N photodiode region (a too small overlap leads to high EFE and a too large overlap leads to a surface depletion area bigger than what is necessary, and so to a large number of in-terface generation centers in the photodiode depletion region); and 3) to reduce the photodiode perimeter (leading to a direct re-duction of dark current but also to possible EQE and cross-talk degradations).

VII. CONCLUSIONS ANDPERSPECTIVES

This work demonstrates that, despite the use of 3.3 V MOS-FETs and CMOS analog circuits (that are more sensitive to TID than 1.8 V digital circuits), CIS can be radiation hardened to operate in the MGy range (tested up to MGy Grad here) and with good performances. It also demonstrates that 1.8 V logic gates and I/O pads of the IMEC DARE UMC 0.18 platform can handle very high levels of TID, much beyond the kGy target for which this library has been designed. The proposed improved gated photodiode design appears to be more efficient at mitigating TID effects than the existing clas-sical radiation hardened designs. The main weaknesses of this

first test vehicle is the large 3.3 V P-MOSFET degradation and the still significant dark current rise with TID.

This study also provides the first opto-electrical performance data from CMOS Image Sensors irradiated to several MGy and several mitigation technique propositions to push even further these performances. Thanks to these results, it could be possible to design a full size sensor with a good idea of the reachable performances after irradiation for extreme TID applications.

The next step will be to explore the proposed improvements, to integrate more functions on-chip, to increase the format and add more features in order to develop a full size, fully integrated Multi-MGy or even Grad Radiation Hard CMOS Image Sensor with high performances (even in this extreme TID range).

ACKNOWLEDGMENT

The authors are grateful to the Imec-Europractice team and especially Marc Dingenen, Erwin Deumens and Paul Malisse for their great support. The authors also thank the Imec DARE team and the people involved in the creation of the DARE UMC 0.18 library. In particular we would like to express our grati-tude to Steven Redant (Imec), Boris Glass (ESA), Geert Thys (imec) and Bert Blockx (imec). Andrei Goussarov (SCK-CEN) is thanked for his support during gamma-ray irradiation.

REFERENCES

[1] J. W. Cho, Y. S. Choi, and K. M. Jeong, “Monitoring performance of the cameras under the high dose-rate gamma ray environments,”

Health Phys., vol. 106, no. 5, pp. S47–S58, 2014.

[2] P. Leroux, J. Sterckx, J. Verbeeck, M. Van Uffelen, and C. Damiani, “Design and simulation of a MGy radiation tolerant signal conditioning circuit for resistive sensors in m CMOS,” IEEE Trans. Nucl. Sci., vol. 59, no. 4, pp. 1309–1316, Aug. 2012.

[3] L. Ding, S. Gerardin, M. Bagatin, S. Mattiazzo, D. Bisello, and A. Paccagnella, “Drain current collapse in 65 nm pMOS transistors after exposure to grad dose,” Trans. Nucl. Sci., vol. 62, no. 6, Dec. 2015. [4] B. R. Hancock, T. J. Cunningham, K. P. McCarty, G. Yang, C. J.

Wrigley, and P. G. Ringold et al., “Multi-megarad (Si) radiation-tol-erant integrated CMOS imager,” in Proc. SPIE, 2001, vol. 4306, pp. 147–155.

[5] B. Pain, B. R. Hancock, T. J. Cunningham, S. Seshadri, C. Sun, and P. Pedadda et al., “Hardening CMOS imagers: Radhard-by-design or radhard-by-foundry,” in Proc. SPIE, 2004, vol. 5167, pp. 101–110. [6] E.-S. Eid, T. Y. Chan, E. R. Fossum, R. H. Tsai, R. Spagnuolo, and J.

Deily et al., “Design and characterization of ionizing radiation-tolerant CMOS APS image sensors up to 30 Mrd (Si) total dose,” IEEE Trans.

Nucl. Sci., vol. 48, no. 6, pp. 1796–1806, Dec. 2001.

[7] J. Bogaerts, B. Dierickx, G. Meynants, and D. Uwaerts, “Total dose and displacement damage effects in a radiation-hardened CMOS APS,”

IEEE Trans. Electron Devices, vol. 50, no. 1, pp. 84–90, Jan. 2003.

[8] M. Innocent, “A radiation tolerant 4t pixel for space applications,” in

Proc. IISW, 2009.

[9] V. Goiffon, M. Estribeau, P. Cervantes, R. Molina, M. Gaillardin, and P. Magnan, “Influence of transfer gate design and bias on the radiation hardness of pinned photodiode CMOS image sensors,” IEEE Trans.

Nucl. Sci., vol. 61, no. 6, pp. 3290–3301, Dec. 2014.

[10] V. Goiffon, P. Cervantes, C. Virmontois, F. Corbiere, P. Magnan, and M. Estribeau, “Generic radiation hardened photodiode layouts for deep submicron CMOS image sensor processes,” IEEE Trans. Nucl. Sci., vol. 58, no. 6, pp. 3076–3084, Dec. 2011.

[11] D. Contarato, P. Denes, D. Doering, J. Joseph, B. Krieger, and S. Schindler, “A m pitch cmos active pixel sensor in 65 nm technology for electron microscopy,” in Proc. IEEE Nucl. Sci. Symp.

Medical Imaging Conf. (NSS/MIC), Oct. 2012, pp. 2036–2040.

[12] V. Goiffon, M. Estribeau, and P. Magnan, “Overview of ionizing ra-diation effects in image sensors fabricated in a deep-submicrometer CMOS imaging technology,” IEEE Trans. Electron Devices, vol. 56, no. 11, pp. 2594–2601, Nov. 2009.

[13] S. Redant, R. Marec, L. Baguena, E. Liegeon, J. Soucarre, and B. Van Thielen et al., “The design against radiation effects (DARE) library,” in RADECS2004 Workshop, Madrid, Spain, 2004, pp. 22–24. [14] F. Faccio and G. Cervelli, “Radiation-induced edge effects in deep

sub-micron CMOS transistors,” IEEE Trans. Nucl. Sci., vol. 52, no. 6, pp. 2413–2420, Dec. 2005.

[15] M. Gaillardin, V. Goiffon, M. Martinez, P. Paillet, S. Girard, and M. Raine et al., “Multi-MGy total ionizing dose effects in CMOS tech-nologies,” IEEE Trans. Nucl. Sci., submitted for publication. [16] K.-H. Koo, J.-H. Seo, M.-L. Ko, and J.-W. Kim, “A new level-up

shifter for high speed and wide range interface in ultra deep sub-mi-cron,” in Proc. IEEE Int. Symp. Circuits Systems (ISCAS), May 2005, vol. 2, pp. 1063–1065.

[17] H. L. Hughes and J. M. Benedetto, “Radiation effects and hardening of MOS technology: Devices and circuits,” IEEE Trans. Nucl. Sci., vol. 50, pp. 500–501, Jun. 2003.

[18] M. Gaillardin, V. Goiffon, S. Girard, M. Martinez, P. Magnan, and P. Paillet, “Enhanced radiation-induced narrow channel effects in com-mercial 0.18 um bulk technology,” IEEE Trans. Nucl. Sci., vol. 58, no. 6, pp. 2807–2815, Dec. 2011.

[19] E. R. Fossum, “CMOS image sensors: Electronic camera-on-a-chip,”

IEEE Trans. Electron Devices, vol. 44, no. 10, pp. 1689–1698, Oct.

1997.

[20] N. Teranishi, A. Kohono, Y. Ishihara, E. Oda, and K. Arai, “No image lag photodiode structure in the interline CCD image sensor,” IEDM

Tech. Dig., vol. 28, pp. 324–327, 1982, IEEE.

[21] E. R. Fossum and D. B. Hondongwa, “A review of the pinned photo-diode for CCD and CMOS image sensors,” IEEE J. Electron Devices

Soc., 2014.

[22] V. Goiffon, M. Estribeau, O. Marcelot, P. Cervantes, P. Magnan, M. Gaillardin, C. Virmontois, P. Martin-Gonthier, R. Molina, F. Corbiere, S. Girard, P. Paillet, and C. Marcandella, “Radiation effects in pinned photodiode CMOS image sensors: Pixel performance degradation due to total ionizing dose,” IEEE Trans. Nucl. Sci., vol. 59, no. 6, pp. 2878–2887, Dec. 2012.

[23] E. Stevens, H. Komori, H. Doan, H. Fujita, J. Kyan, C. Parks, G. Shi, C. Tivarus, and J. Wu, “Low-crosstalk and low-dark-current CMOS image-sensor technology using a hole-based detector,” in Proc. IEEE

Int. Solid-State Circuits Conf. (ISSCC) Tech. Dig., Feb. 2008, pp.

60–595.

[24] S. Place, J.-P. Carrere, P. Magnan, V. Goiffon, and F. Roy, “Rad tol-erant CMOS image sensor based on hole collection 4t pixel pinned photodiode,” IEEE Trans. Nucl. Sci., vol. 59, no. 6, pp. 2888–2893, Dec. 2012.

[25] W. Dulinski, A. Besson, G. Claus, C. Colledani, G. Deptuch, M. De-veaux, G. Gaycken, D. Grandjean, A. Himmi, C. Hu, K. Jaaskeleinen, M. Szelezniak, I. Valin, and M. Winter, “Optimization of tracking performance of CMOS monolithic active pixel sensors,” IEEE Trans.

Nucl. Sci., vol. 54, no. 1, pp. 284–289, Feb. 2007.

[26] M. Battaglia, D. Contarato, P. Denes, D. Doering, P. Giubilato, T. S. Kim, S. Mattiazzo, V. Radmilovic, and S. Zalusky, “A rad-hard CMOS active pixel sensor for electron microscopy,” Nucl. Instr. Meth. A, vol. 598, no. 2, pp. 642–649, Jan. 2009.

[27] D. Contarato, P. Denes, D. Doering, J. Joseph, and B. Krieger, “Di-rect detection in transmission electron microscopy with a m pitch CMOS pixel sensor,” Nucl. Instr. Meth. A., vol. 635, no. 1, pp. 69–73, 2011.

[28] D. Contarato, P. Denes, D. Doering, J. Joseph, and B. Krieger, “High speed, radiation hard CMOS pixel sensors for transmission electron microscopy,” Physics Procedia, vol. 37, pp. 1504–1510, 2012. [29] G. R. Hopkinson, A. Mohammadzadeh, and R. Harboe-Sorensen,

“Ra-diation effects on a ra“Ra-diation-tolerant CMOS active pixel sensor,” IEEE

Trans. Nucl. Sci., vol. 51, no. 5, pp. 2753–2761, Oct. 2004.

[30] B. Dryer, A. Holland, N. J. Murray, P. Jerram, M. Robbins, and D. Burt, “Gamma radiation damage study of 0.18 m process CMOS image sensors,” in Proc. SPIE, 2010, vol. 7742.

[31] E. Martin, T. Nuns, J.-P. David, O. Gilard, J. Vaillant, P. Fereyre, V. Prevost, and M. Boutillier, “Gamma and proton-induced dark current degradation of 5T CMOS pinned photodiode cmos image sensors,” IEEE Trans. Nucl. Sci., vol. 61, no. 1, pp. 636–645, Feb. 2014. [32] P. R. Rao, X. Wang, and A. J. P. Theuwissen, “Degradation of CMOS image sensors in deep-submicron technology due to -irradiation,”